PCI Express -teknik har länge använts för att ansluta grafikkort och andra kringutrustning, till exempel NVMe SSD -enheter. Implementeringen av den femte generationen av gränssnittet sker med ankomsten av Alder Lake -processorerna från Intel och Zen 4 -processorerna från AMD. Men PCI Express 6.0 -specifikationen har slutförts och ger flera förbättringar under femte generationen.

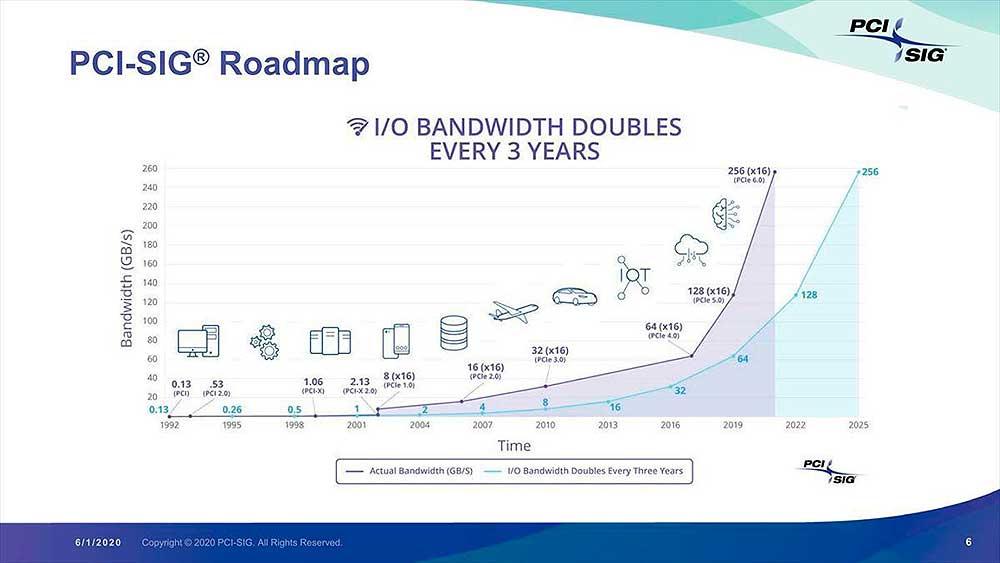

PCI Express 6.0 följer från början samma förbättringar som de tidigare generationerna av detta gränssnitt, det vill säga att det är baserat på att fördubbla bandbredden jämfört med den tidigare generationen. När det gäller PCI Express 6.0 har det dock behövts stora förändringar i utvecklingen av den sjätte generationen av detta gränssnitt.

Bandbredden för PCI Express 6.0 är 128 GB / s för ett 16-linjers gränssnitt, en överdriven hög bandbredd för ett I / O-gränssnitt och det är ett fyrfaldigt hopp jämfört med nuvarande PCI Express 4.0 som vi använder för aktuell grafik kort. Hoppet betyder också ett hopp från NVMe SSD blixtkontroller från 7-8 GB / s till 28 -32 GB / s med PCI Express 6.0.

Bakåtkompatibilitet och problemet med signalinstabilitet

PCI Express -gränssnittet har alltid varit bakåtkompatibelt med tidigare versioner av protokollet, det betyder att vi kan ansluta ett PCI Express 1.0 -kort till en PCI Express 6.0 -kortplats och det kommer att fungera eftersom tappen kommer att vara exakt densamma. Så det är inte möjligt att öka antalet stift för att öka bandbredden utan att öka hastigheten. Lösningen? Öka klockhastigheten med vilken gränssnittet fungerar.

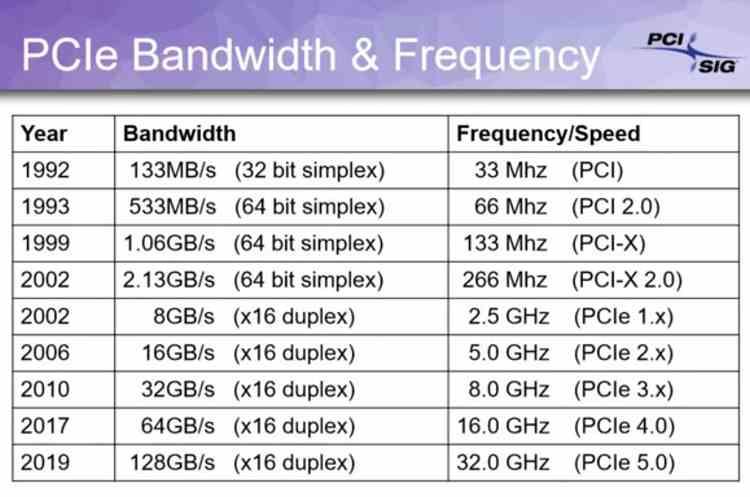

Problemet med PCI Express 6.0? När vi ökar klockhastigheten för ett gränssnitt blir det mer instabilt med avstånd och efter sex generationer har de fått göra ändringar i gränssnittet på grund av den höga hastighet som gränssnittet fungerar på ett traditionellt sätt. Och om du tittar på tabellen som följer dessa linjer talar vi om en teoretisk hastighet på 64 GHz, som deformerar signalen tillräckligt, även på det korta avståndet är båda ändarna i ett PCI Express -gränssnitt.

Detta har tvingat en rad åtgärder att vidta för att göra språnget till PCI Express 6.0 möjligt.

Först av förbättringarna i PCI Express 6.0, användning av PAM4

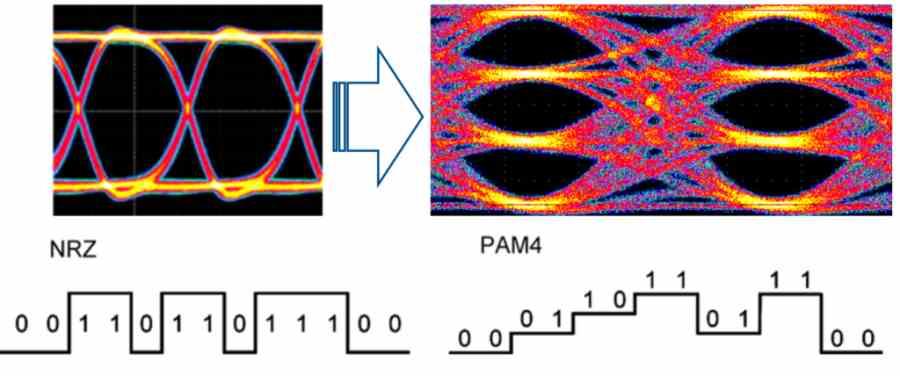

Hur vet ett externt eller internt gränssnitt för ett chip om värdet är 1 eller 0? Tja, enkelt, beroende på spänningen i vilken informationen överförs. Binära system är baserade på användning av två spänningar med tillräckligt avstånd mellan dem så att spänningsfallet eller stigningen gör att signalen inte blir förvirrad. I analoga system förutsätter en enkel variation i spänningen en förändring av informationen. Av denna anledning talar datorer i binärt.

Vad har detta att göra med PCI Express 6.0? Eftersom vi inte kan öka bandbredden eftersom signalen är förvrängd och inte heller antalet stift för bakåtkompatibilitet, måste en lösning hittas och detta går genom användning av PAM4 -kodning eller Pulse Amplitude Modulation, som vi redan har sett i GDDR6X och är inte baserat på användningen av två spänningsvärden utan 4 spänningsvärden för varje stift. På så sätt kan vi koda värdena 00, 01, 10 och 11 på varje stift. Totalt fyra värden istället för de två klassiska värdena som skulle vara 0 eller 1.

Lösningen undviker att öka bandbredden och stiften, men den berättar att det i PCI Express 7.0 inte längre kommer att vara möjligt från konventionella metoder. Vi kanske ser användningen av fotonik och optiska gränssnitt, men med förbättringarna av PCI Express 6.0 färska ur ugnen är det bättre att ha tålamod med dess efterträdare.

Ändringar i paketsystemet

Hoppet till PAM-4 har förändrat hur PCI Express 6.0-gränssnittet skickar sina paket, trots att det är kompatibelt med tidigare generationer genom att kommunicera i det traditionella PAM-2- eller NRZ-läget. Verkligheten är att PAM-4-formatet inte stöder det tidigare paketsystemet och därför har kommunikationsprotokollet ändrats på grund av det.

Den första ändringen har varit den så kallade Forward Error Correction eller FEC, som är det nya protokollet för att korrigera fel vid sändning av data. Problemet är att bandbredden som ska bearbetas är så hög att FEC lägger till enorm latens när data skickas. För att lindra detta använder PCI Express 6.0 -standarden en typ av paket som heter FLIT. Ett paket är inget annat än en uppsättning bitar med en specifik destination. Skicka latens för varje FLIT? Det beror på antalet rader på gränssnittet, men varje paket har en latens på endast 2 ns på en 16-linjers PCI Express 6.0, men går upp till 32 ns på ett enradigt gränssnitt.

FEC fungerar bara med fasta storlekar, det är därför FLIT har en storlek på 256 byte per sändning. Varje paket eller TLP kan ha en storlek som sträcker sig från 0 byte till 4096 byte och därför kan varje paket bestå av flera FLITS.

Tredje uppgraderingen till PCI Express 6.0, variabel förbrukning

PCI Express 6.0 lägger till ett nytt lågeffekttillstånd som kallas L0P. Detta läge gör att gränssnittet kan minska sin strömförbrukning när dataflödet som skickas är lägre än gränssnittet kan överföra. För att göra detta varierar klockhastigheten vid vilken gränssnittet fungerar vid specifika ögonblick av dataöverföring, allt utan att orsaka ett stopp som tillför dataöverföring latens.

Problemet är att denna mekanism är associerad med FLITS och FEC och därför med PAM4, vilket innebär att det bara är möjligt att använda i PCI Express 6.0 -läge och inte i de andra lägena.