Ett av de mest utbredda koncepten inom datoranvändning idag är utan tvekan XMP. Alla användare som är måttligt intresserade av hårdvara vet att när vi talar om minnesöverklockningsprofiler, Intel har tagit mått på AMD, som ständigt försöker anpassa sig till dessa krav genom sin AMP-teknik. Med avgången av Alder Lake-S som en revolutionerande arkitektur har Intel gått ett steg längre genom att presentera XMP 3.0 , men vilka nyheter döljer det?

Vissa undrar skälen till Intels beslut ang RAM och specifikt XMP. Även om vi aldrig kommer att veta, är sanningen att övergången från DDR4 till DDR5 var en idealisk tid ur överklockningsperspektivet för att implementera förändringar och förbättringar, eftersom vi ser 4,800 XNUMX MHz av JEDEC de lämnas kvar bara några dagar efter att Core 12-processorer kommer att introduceras.

Därför, och med tanke på hur snabbt tillverkarna accelererar och uppdaterar sina moduler med ökande seriella hastigheter, återstår det bara att undra, har Intel tagit hänsyn till detta? Är XMP 3.0 uppdaterad med vad som kommer att krävas av det?

Intel XMP 3.0, en nödvändig twist

eXtreme Memory Profile eller XMP har funnits med oss sedan 2007 och i denna tredje version ser man tillbaka och efter 14 år är det normalt att den blå jätten lanserar en ny revision med nyheter. Varför? För de förändringar som DDR5 förutsätter med avseende på DDR4. Vi kommer inte att gå in på detta ämne eftersom vi redan har behandlat det i förlängning, men om det finns något att säga om XMP 3.0 så är det att det är exklusivt för DDR5 som sådant.

Termen Profile of its name kommer till fingret för att förklara den första av punkterna där Intel har gett tillverkarna, eftersom som vi väl vet är denna teknik baserad på erkännandet av en serie konfigurationstabeller som varje tillverkare integrerar för att smaka efter modell , chip och minnesversion för att få IMC att känna igen och tillämpa dessa inställningar via firmware.

Vad är nytt i Intel XMP 3.0

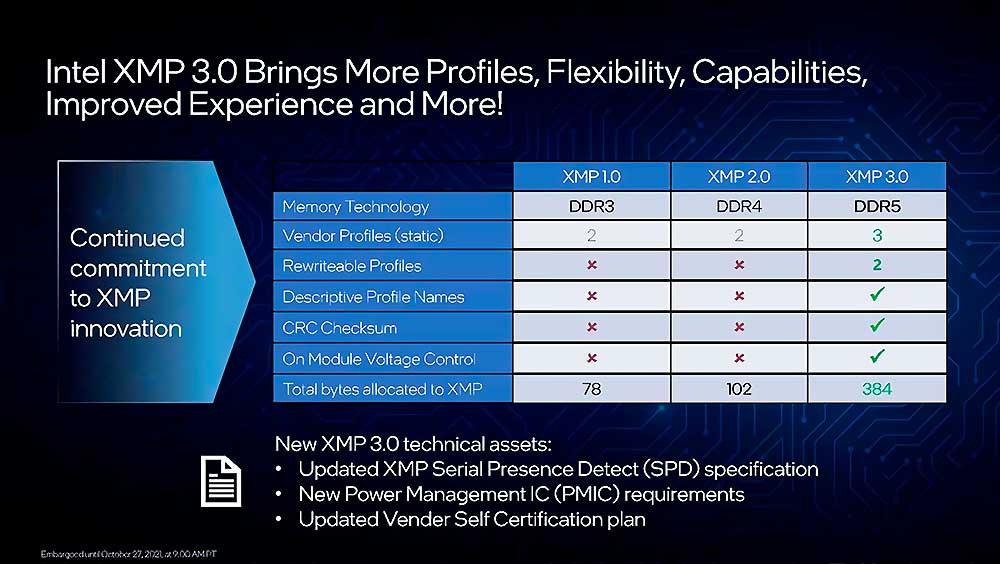

Dessa tabeller inkluderar hastigheter i MHz, klockor och tider för primära, sekundära och tertiära åtkomster som är logiskt snabbare i vissa fall eller långsammare i andra, men som i alla fall ökar den allmänna prestandan hos minnet och med det systemet. I den första versionen med sitt eget namn, XMP, lyckades Intel inkludera inkluderingen av att läsa en profil i minnet plus den för JEDEC (tekniskt sett är det en profil, men de räknas som två)

XMP 2.0 höjde nivån till två läsprofiler, där tillverkare kunde fastställa om de ville ha två olika värden och tabeller, anpassa användarupplevelsen och gynna olika prestanda (tre realer räknar JEDEC). Med XMP 3.0 kan tillverkare nu ha två eller tre profiler att inkludera, och kunna välja två anpassade av användaren.

SPD-uppdatering

En av nyckelpunkterna för XMP-profilen är just SPD eller Serial Presence Detect-specifikation . Detta har orsakat flera huvudvärk för tillverkare och användare, främst för att de kan skrivas från EEPROM och därför blir skadade. Det finns några program som kan göra det och naturligtvis skapar det krascher i minneskontrollern, eftersom den inte kan läsa värdena korrekt från XMP och minnet är oanvändbart tills en ny blinkning sker korrekt.

Nu och med XMP 3.0 kommer vi att ha två uppdateringsbara profiler, vilket hjälper så att om den ena är skadad kan den andra låta minnet fungera, dess SPD kan extraheras och senare kan det flashas modul för modul, reparera minnet som om ingenting hade hände.

CRC-kontrollsumma

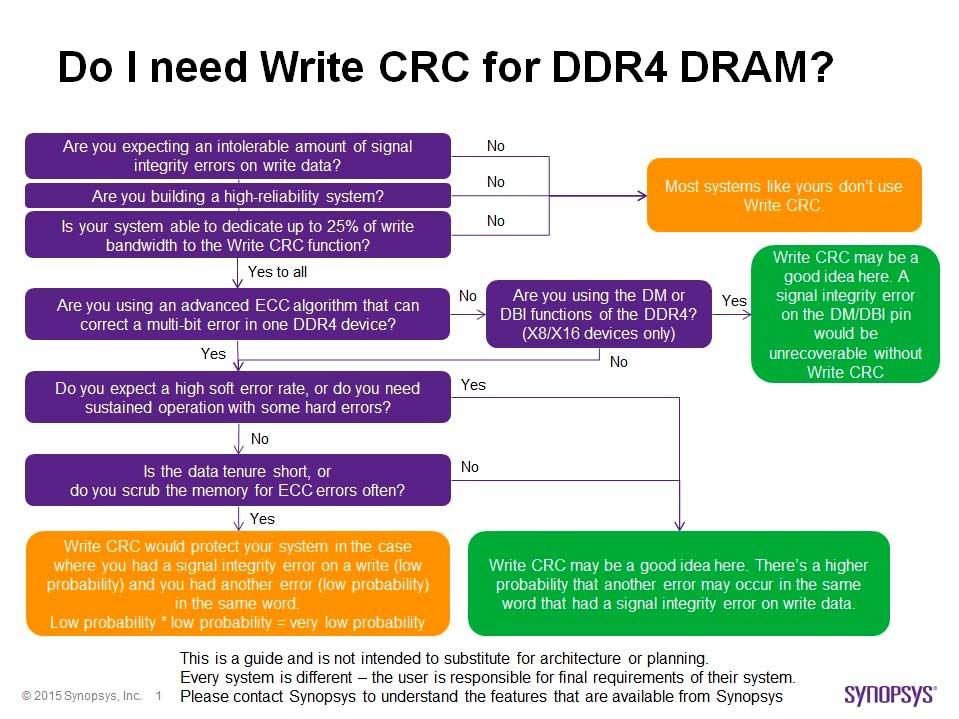

Konstigt nog och redan förklarat detta, varför har inte DDR4-moduler med XMP 2.0 CRC? Det är inte precis så och logiskt sett har det ett varför. CRC som sådan lades till i sin Write-version i JEDEC-standarden för DDR4, men den cykliska redundanskoden har ett problem: hög bandbreddsförbrukning. Uppgifterna visar förbrukning av 25% av den totala skrivningen av systemet och naturligtvis är det inte acceptabelt att förlora den mängden bandbredd med de marginaler och hastigheter som vi flyttar idag.

Detta är inte längre ett problem med DDR5, eftersom förutom att inkludera PMIC i själva minnet, i modulen rent fysiskt sett, är och kommer hastigheterna att vara monstruösa jämfört med DDR4, speciellt om vi har dubbel bandbredd som integrerar denna typ av minne . Därför integrerar Intel med XMP 3.0 den eftertraktade CRC Checksum som kommer att skydda data och integritet för SPD såväl som CPU minneskontroller.

Större utrymmesökning för XMP 3.0

En av nyckelaspekterna och redan att förstå allt vi har sagt om nya XMP 3.0 är att vi logiskt sett behöver mer utrymme för att hysa allt detta. Därför har Intel gått från 78 byte per modul för XMP 1.0, till 102 för XMP 2.0 och höjer den nu till 384 bytes kontroll för XMP 3.0.

Detta är vad som gör att förinställda minnesprofiler som SPD kan väljas från moderkort BIOS / UEFI. Frågan vi har då är beteendet hos BMI för de nya Alder Lake- och Meteor Lake-processorerna (ett betydande frekvenshopp förväntas) med de olika hastigheterna som vi kommer att se från tillverkarna och chipsen.

Kommer vi att se XMP 3.0-profiler över 6000 MHz? Kan processorernas BMI stödja dem utan att svämma över spänningen och därmed förbrukningen och försämringen? För tillfället vet vi att det finns varumärken som arbetar med profiler för DDR5-7000, så det verkar som att antingen dessa nya minnen och chips lyckas utvecklas mycket snabbare än CPU:er och deras BMI, eller så betyder det att potentialen för uppladdning och support / uthålligheten hos de integrerade minneskontrollerna är större än vi kanske tror.

Man måste komma ihåg att även om XMP 3.0 når mycket höga hastigheter i vissa moduler så är det IMC som avgör om den kan stödja nämnda hastighet och dess spänning, vilket är logiskt oberoende av själva RAM-minnet.

Efter att ha sagt och förtydligat detta kan vi bara säga att Intel har tagit ett mycket stort steg framåt, det största sedan de lanserade XMP 2007 och som sådan är det nu AMD som kommer att behöva anpassa sin teknologi och IMC till dessa nya krav med Zen. Fyra.