De allra flesta av er inser säkert inte det faktum att vi står på gränsen till ett vägskäl så långt som CPU och GPU är oroad. Det finns inte mycket marginal, det finns inte mycket tid och det som återstår håller på att ta slut. En förändring behövs i en så grundläggande komponent som själva beräkningskonceptet: i transistorn. Intel har sin vision om problemet och en lösning: detta kommer att vara Intel RibbonFET.

För att förstå lösningen måste vi först vara medvetna om problemet, förstå det och veta vilka gränserna som kommer att sätta prägel på oss, så i det här fallet ska vi börja där, med problemen med transistorer idag. En transistor är den minsta elektriska enhet som kan tillverkas för en elektronisk komponent, ett elektriskt element som sådant som är tillverkat av halvledare och registrerat av otroligt avancerade skannrar med hjälp av en våglängd på speglar.

Det är i grunden en omkopplare som är sammankopplad mellan dussintals lager av kisel (som en allmän regel) av en mycket liten storlek och som har en extremt tydlig funktion: att ändra strömflödet som passerar genom det, ge vika eller skära av det. Varje snitt eller steg representerar antingen en nolla eller en etta i binärt och med tidens gång är det som har uppnåtts att förbättra det, vilket tillåter mer hastighet i tillståndsändringen, mer eller mindre energi för nämnda förändring och mer eller mindre effektivitet när det släpps det aktuella passet.

Vi närmar oss kanten av transistorteknik

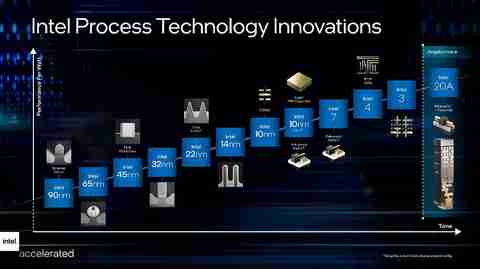

Som vi redan har trott har varje transistor en serie konstruktioner som varierar beroende på tillverkare. Intel har sin vision, TSMC samma och Samsung mer av detsamma, så även om alla mer eller mindre kopieras i förskotten är implementeringen och förbättringarna olika.

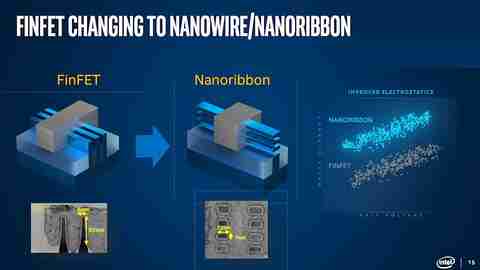

För ett decennium sedan introducerade Intel FinFET-transistorn, som har valts av alla tillverkare, men den designen håller på att ta slut av flera anledningar. Med denna typ av transistor hade vi en flexibel design av samma, normalt breda, där flera portar korsade den, vilket gjorde det möjligt för tillverkare att bättre styra energihantering, svetsning och byggmaterial, samt fortsätta minska dess storlek i nanometer.

Huvudproblemet vi har är enkelt: det kan inte reduceras mycket mer i storlek, eftersom vi har begränsat längsgående utrymme och grindarna på varje transistor inte kan ansluta längre utan att förlora elektroner. Till detta måste läggas att avståndet mellan dem är så litet att svetsning och sammankoppling kräver oerhört dyra nya material och legeringar, vissa fortfarande experimentella, som garanterar energipassage och inte utlöser priset.

Vad är lösningen? En ny typ av transistor som tillåter inte bara fler lager att driva ström, förbättra kontroll, svetsning och effektivitet, utan också minska avståndet mellan transistorer till Ångström (molekylär och atomär måttenhet).

RibbonFET, Intels lösning på den nya gränsen för litografi

Om du inte kan fortsätta att minska utrymmet och kontrollera alla parametrar utan att trigga kostnaden, återstår bara att undersöka en ny väg. Denna nya väg i form av en ny arkitektur för transistorn kallas GAA eller även känd som Gate-All-Around. Härifrån är konceptet uppdelat i tre aspekter eller till och med fyra (det är inte helt klart):

- TSMC GAAFET .

- Samsung MBCFET .

- Intel Band FET .

- Global Foundries är i limbo med rykten, men inget konkret.

Vad händer här? Tja, som hände med FinFET kommer GAA att ha flera varianter, alla baserade på samma transistorkoncept. Vi har redan pratat om Samsung MBCFET, GAAFET har ännu inte exponerats som sådan även om den kommer med företagets 2 nm, så efter presentationen av Intel på sin Architecture Day 2021 och efter att ha avslöjat lite mer detaljer, kommer vi att veta vad av den jätteblå: RibbonFET.

Konceptet är enkelt, men svårt att genomföra. De tar en transistor med flexibel bredd som kommer att minskas med varje litografiskt hopp och som gör att flera lager, nu kallade nanosheets, torra ark eller fenor av industrin, kan kopplas vertikalt på transistorn istället för horisontellt. Vad uppnås? Tja, först och främst, minska transistorns bredd avsevärt, tillåt fler nanoark på en mindre yta och framför allt en enda gate som kommer att styra all energi i cellen.

Elektrostatiken har förbättrats enormt som Intel visade i sin officiella presentation, där vi bara behöver se storlekarna på Pitch Gate och Gate Stack. Det går från 6 nm x 50 nm till 12 nm x 7 nm och med mer kontroll nanosheets och bättre lödda.

En variabel nanosheets design enligt transistorns behov

Tydligen och som vi har sett i olika dokument sedan Intel talade om denna nya typ av transistor, verkar det som att den blå jätten kan samla ett varierande antal nanoblad per transistor.

Denna detalj är viktig, eftersom när Intel går ner i litografin baserat på bättre EUV-skannrar kommer den att kunna behålla samma antal eller ta bort de som behövs för att optimera varje Gate. Dokumenten visar från 2 till 5, men i det sista databladet verkar det runda siffran vara 4. Fler fenor / nanoblad kräver fler steg för att skapa transistorn, så det ökar kostnaden för varje chip, så eventuellt kommer Intel att börja med ett nummer medel för dem tills du har förbättrat gravyr och produktionskontroll, material och svetsar som gör att du kan eliminera ett antal bestämda nanoskivor och minska kostnaderna utan att äventyra stabiliteten, hastigheten eller effektiviteten hos transistorerna.

Detta kommer logiskt att bero på höjden på porten och med det antalet ark som vi kan installera i den, eftersom nu istället för att vara omgiven av tre platser som hände i FinFET, är varje ände helt omgiven av porten, vilket betyder en sidan är optimal, men den andra gör det svårt att minska höjden mellan arken.

När kommer Intel RibbonFET att implementera i sina chips? Enligt företaget självt 2024, säkert i slutet av samma år om allt går bra, även om det vore smidigt skulle vi kunna se det i mitten av samma år. Det kommer i alla fall att vara dess 20A litografiska process som inkluderar den och kommer att konkurrera med TSMC:s GAAFET och Samsungs MBCFET . Intel är så säkra på att det kommer att göra skillnad att det redan har sagt att det kommer att leda halvledarindustrin och dess teknologi igen 2025 – utan tvekan en avsiktsförklaring.