Den framtida ankomsten av chipletbaserade processorer medför en fråga: vilka gränssnitt och protokoll som kommer att användas för att kommunicera de olika elementen i en chiplet med varandra. Även om det kommer att finnas flera olika och en för varje varumärke, är Common Electrical I / O i två av dess varianter kommunikationsgränssnittet som kommer att användas för kommunikation av chipletterna ovanpå en interposer.

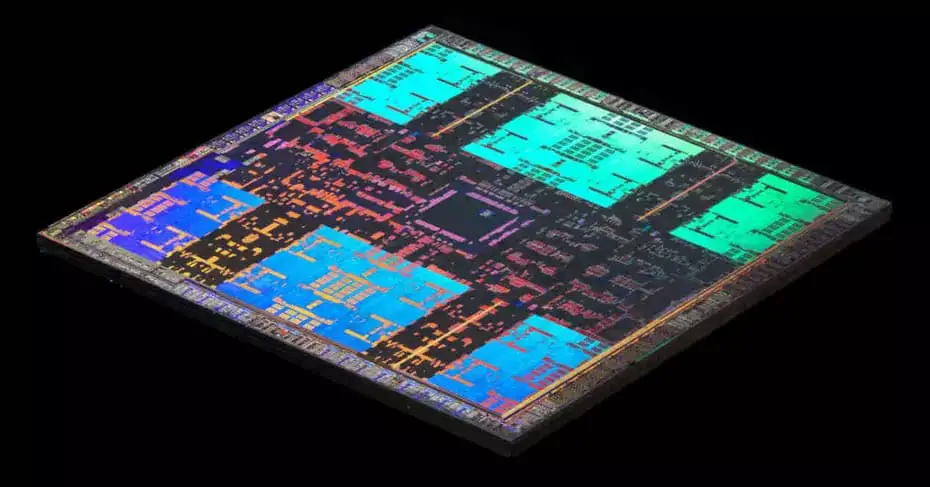

Det råder ingen tvekan om att processorer som består av chiplets kommer att vara normen de närmaste åren, vi vet att det kommer att vara satsningen på framtida mönster från båda Intel, AMD och NVIDIA, där var och en av dem har utvecklat ett eget gränssnitt för kommunikation för användning med dina arkitekturer.

Common Electrical Interface, å andra sidan, är gränssnittet som standardiseras för kommunikation mellan elementen i en chiplet och som inte ägs av dessa tre företag. Dessutom är många av designen byggda FPGA-enheter som använder detta gränssnitt för att kommunicera de olika delarna. Även om det innan du förklarar vad det består av är det bäst att ta en rundtur genom en serie grundläggande begrepp.

Begreppet NoC

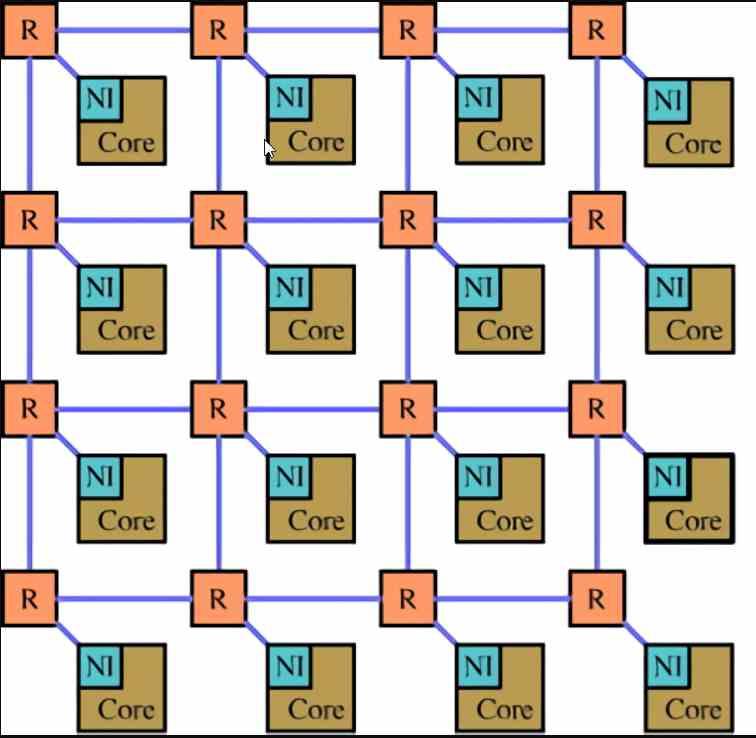

NoC eller nätverk på ett chip, är idén att göra en interkommunikation mellan de olika komponenterna på PC: n som om det vore ett nätverk, för detta har alla element en router som kommunicerar den med de andra elementen, så bara Det är nödvändigt att varje element i nätverket har en inbyggd router som används för att kommunicera och kommunicera med resten

Varje element i komponentnätverket har sin egen adress och sättet att kommunicera mellan de olika komponenterna är att få varje element att ringa nätverksadressen till ett annat element, där inte bara behandlingselementen har en adress inom samma, inte bara processorerna och I / O-gränssnitt, men också minnena som komponerar det, vare sig det är RAM, VRAM och till och med NVMe-chips för att underlätta kommunikation.

Idén om en MCM som NoC

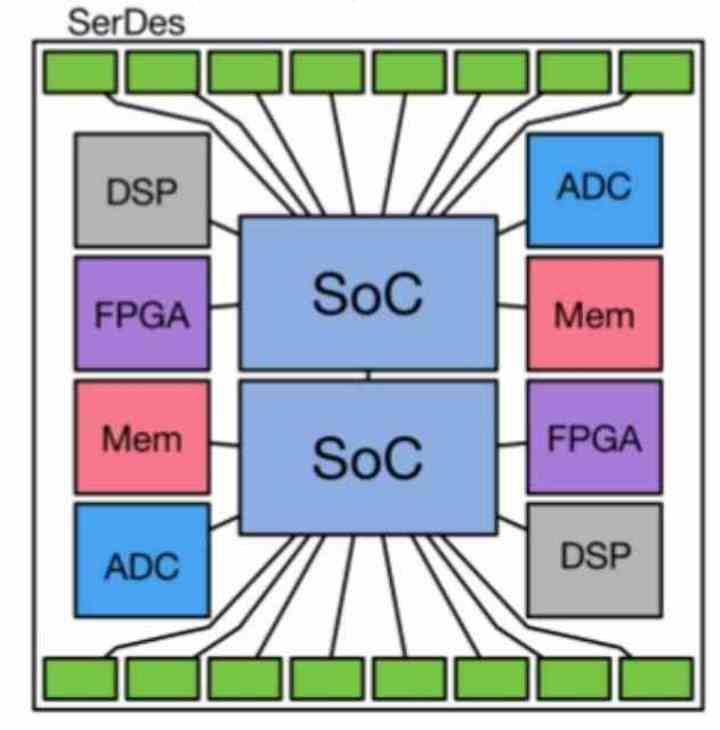

Något som skiljer en SoC från en MCM är att i det första fallet har vi en central enhet på chipet som ansvarar för att kommunicera med varandra alla element i chipet och dessa med minnet är vanligt i alla SoC, oavsett vilket är vilken arkitektur vi pratar om, alla SoC-filer innehåller det gemensamma elementet.

Men i ett MCM som består av flera separata element måste det också finnas en enhet som ansvarar för att kommunicera de olika elementen med varandra. Om vi pratar om en SoC måste det finnas samma enhet som ansvarar för kommunikationen, men om vi talar om ett NoC där varje element kan kommunicera med en annan direkt förändras redan saker.

I ett NoC utförs kommunikation mellan de olika elementen med hjälp av ett nätverksgränssnitt, föreställ dig detta som ett LAN-nätverk, men använd mycket snabbare anslutningar för kommunikation mellan de olika elementen i chiplet, på grund av det korta avståndet och materialet som används.

Vad är den gemensamma elektriska I / O?

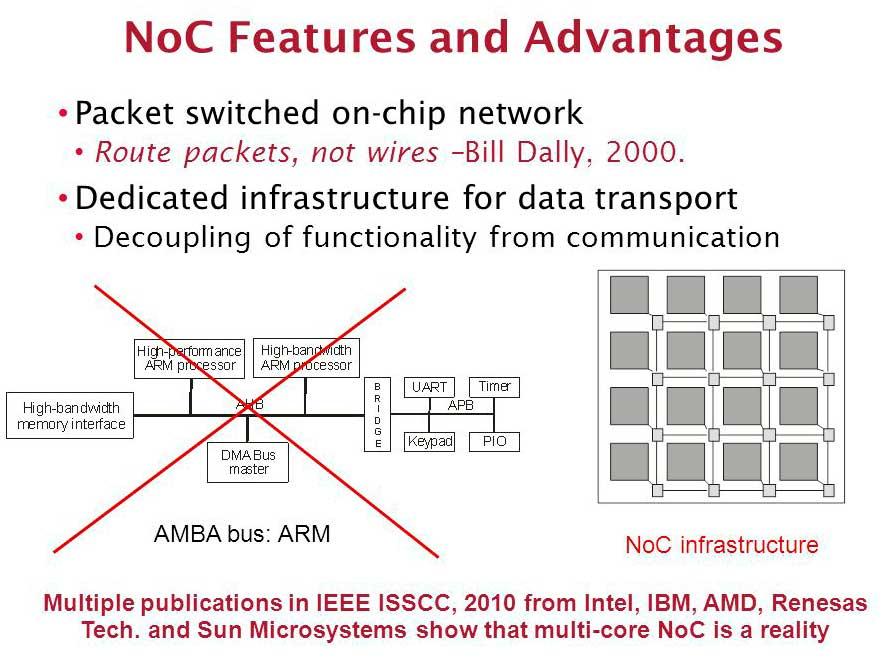

Smakämnen Vanlig elektrisk I / O förkortas till CEI, är en serie avtal gjorda av ett konsortium som heter Optiskt Internet-arbetsforum (OIF), som ansvarar för att definiera de gemensamma kraven för elektriska gränssnitt med en kommunikationshastighet med en överföringshastighet på 3,125 6, 11, 25, 28 -56 och 112, 224 och snart XNUMX Gbps.

CEI har legat till grund för olika typer av I / O-gränssnitt och protokoll såsom Hyper Transport som AMDs Infinity Fabric härrör från, SATA-gränssnittet i flera av dess versioner. olika 803.3- och InfiniBand-gränssnitt.

Dess betydelse beror på att även om Intel och AMD kommer att använda sina egna proprietära gränssnitt för att kommunicera de olika chiplets inom MCM, är förekomsten av ett standardgränssnitt som kan användas extremt viktigt inte bara för att distribuera design baserade på chiplets . av olika processordesigners, men också för utvecklingen av dessa.

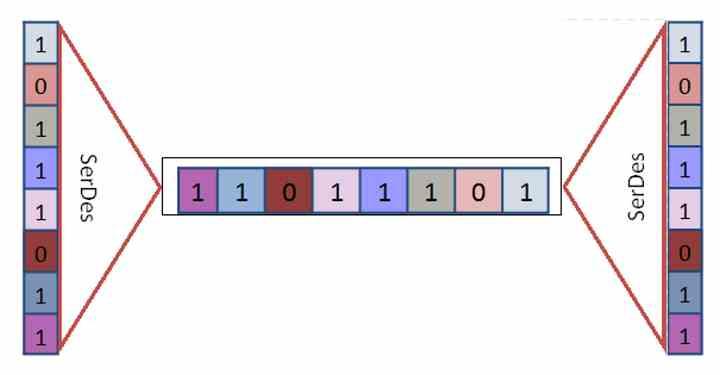

Common Electrical I / O är ett SERDES-gränssnitt som i sin nuvarande version kan nå en överföringshastighet på 112 Gbps. Det har för närvarande olika varianter, men de som intresserar oss är de som är relaterade till chiplets, eftersom de kommer att användas i stor utsträckning för kommunikation mellan de olika elementen.

En SERDES är en typ av gränssnitt som det tar är att ta en serie data parallellt och överföra den i serie till en annan, eftersom det kommer att göra motsatt process, det vill säga den omvandlar en seriell signal till en parallell igen. Därav SERDES-dimensionen.

När det gäller nuvarande 112 Gbps-gränssnitt använder den en PAM4-kodning, på ett sådant sätt att den kan nå 112 Gbps i hastighet med en 28 GHz klockhastighet för kommunikation. Sådana klockhastigheter skulle vara extremt kontraproduktiva om vi talar om långa avstånd, men det är inte fallet med ett MCM som består av chipletter med en mellanlägg nedan, där de olika elementen är för nära för att kommunicera.

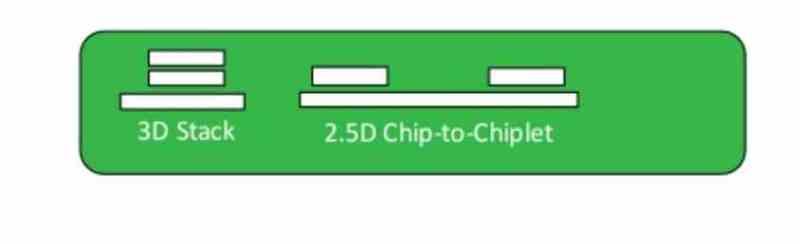

Inom det gemensamma elektriska I / O-gränssnittet har vi två typer, å ena sidan har vi den som ansvarar för kommunikation i en traditionell chiplet, som i sin 112 Gbps-version kallas CEI-112G-MCM och är utformad för att anslutas med ett avstånd mellan båda ändarna är högst 2.5 mm, det korta kabelavståndet gör det möjligt att förbruka mycket lite effekt per överföring.

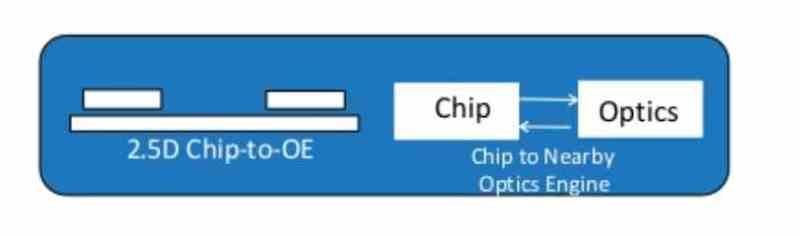

Den andra typen är utformad för kommunikation med en optisk mottagare, och ja, nästa steg efter konventionella mellanlägg är att använda optiska gränssnitt för kommunikation, även om de för närvarande inte används eller kommer de att användas på kort sikt i inhemska system.

Common Electrical I / O för extern kommunikation av chiplets

Trots att det består av olika enheter inuti kan en chiplet ses som en enda enhet som vetter mot utsidan och hur den kommunicerar är genom en serie I / O-gränssnitt som ger anslutning.

Naturligtvis, för kommunikation inom chiplet, måste denna typ av externa gränssnitt omvandlas till en signal av Common Electrical I / O-typen, genom en serie SERDES som ligger nära chipets periferi. strax före de externa gränssnitten, oavsett om det var RAM-, VRAM-, PCI Express-gränssnitt etc.