Om det finns något tydligt i Processorn industrin är det det Intel och AMD dominerar marknaden helt i ett duopol som verkar oöverträffat. Under senare tid har emellertid ODM (detta innebär att de inte tillverkar chips, de utformar bara dem) ARM får mer och mer betydelse, särskilt med mönster som DynamIQ , en satsning som lovar förbättra kraften av processorer samtidigt som konsumtionen bibehålls, och i den här artikeln ska vi berätta vad den består av.

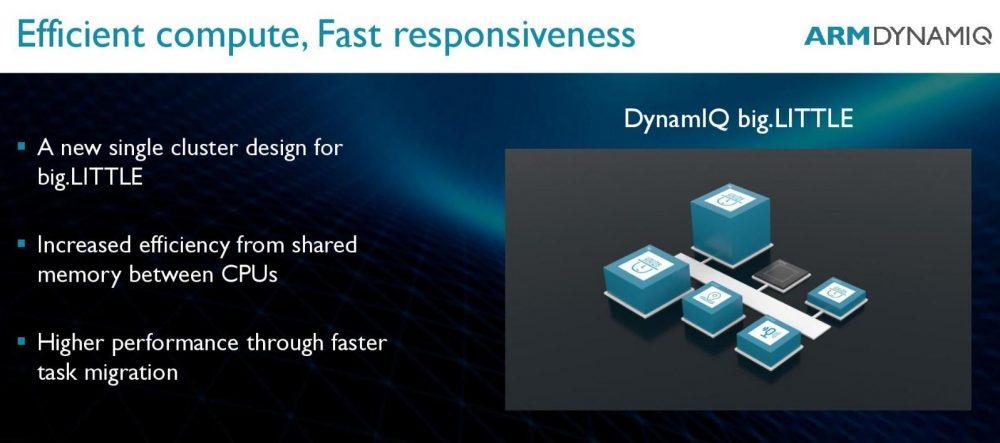

Om det finns en ARM-design som är känd, är det faktiskt big.LITTLE , som består av en heterogen arkitektur som består av större och kraftfullare kärnor för att utföra krävande uppgifter och andra mindre och lågeffektiva kärnor för att spara energi när utrustningen inte gör det. kräver stor kraft. Denna arkitektur har implementerats i smartphonechips under lång tid och inte så länge sedan att Intel (och det verkar till och med att AMD med Zen 5) har antagit ett liknande paradigm (men på sitt eget sätt) i sina stationära processorer, så allt pekar som är vägen att gå.

ARM DynamIQ, hur ökar jag effekten utan att öka förbrukningen?

ARM-arkitekturen har pågått i många år som ett alternativ till Intel och AMD, men särskilt i mobiltelefoner och servrar tack vare dess låga förbrukning, men det var inte förrän Apple beslutade att skapa sitt eget M1-chip och integrera det i sina datorer tills ARM verkligen har gått in i den inhemska PC-industrin.

Denna nya arkitektur som ARM har kallat DynamIQ (det är ett ordspel på engelska som i princip kombinerar ordet "dynamisk" med "IQ", IQ) riktar sig till mobila enheter och IoT enheter, men de har bekräftat att de också avser att nå ekosystemet för persondatorer och till och med servrar, eftersom dess potential är enorm.

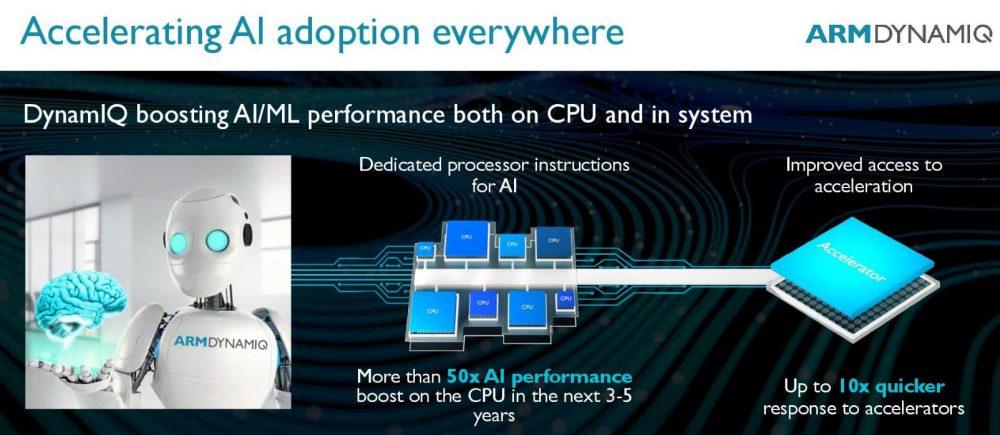

Enligt ARM är målet med denna arkitektur att göra det möjligt för deras marker att vara utrustade med virtual reality- och maskininlärningssystem, och för detta har de lagt till fler kärnor och ett större antal instruktioner (och det är precis vad ARM har alltid gjort "svag" jämfört med x86, eftersom dess marker har mycket mindre och mer specifika instruktionsuppsättningar), levererar upp till 50 gånger mer kraft övergripande för AI-uppgifter.

Det underliggande temat för DynamIQ är heterogen skalbarhet; Dessa två ord döljer mycket jargong från ekosystemet, men eftersom ARM förutspår ytterligare 100 miljarder ARM-marker kommer att säljas under de närmaste 5 åren, pekar de på viktiga områden som fordonsindustrin, artificiell intelligens och maskininlärning i det intressanta slutet av detta tillväxt. Som ett resultat kommer prestanda, skalbarhet och latens att vara viktiga mått framöver som DynamIQ avser att aktivera.

Ett steg bortom big.LITTLE

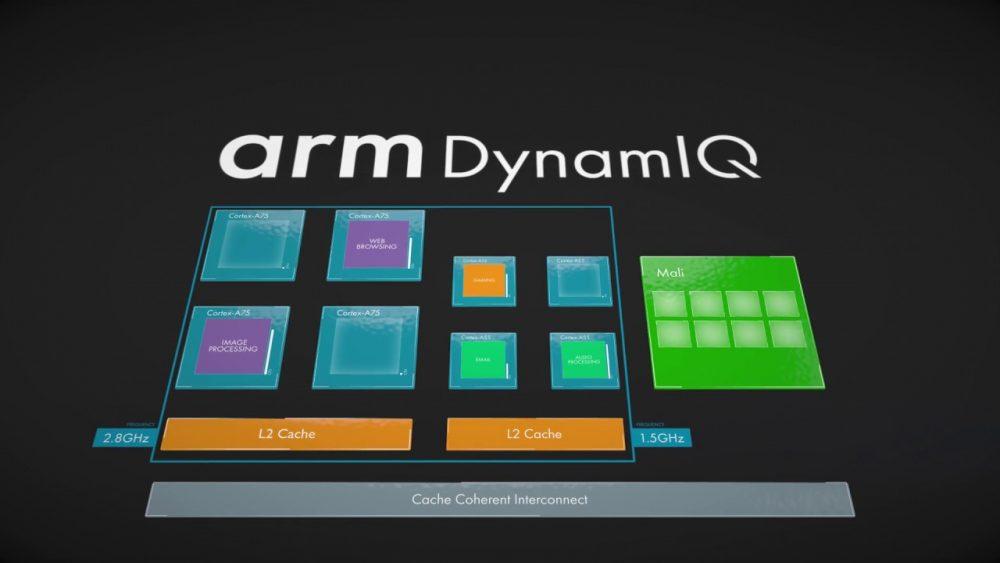

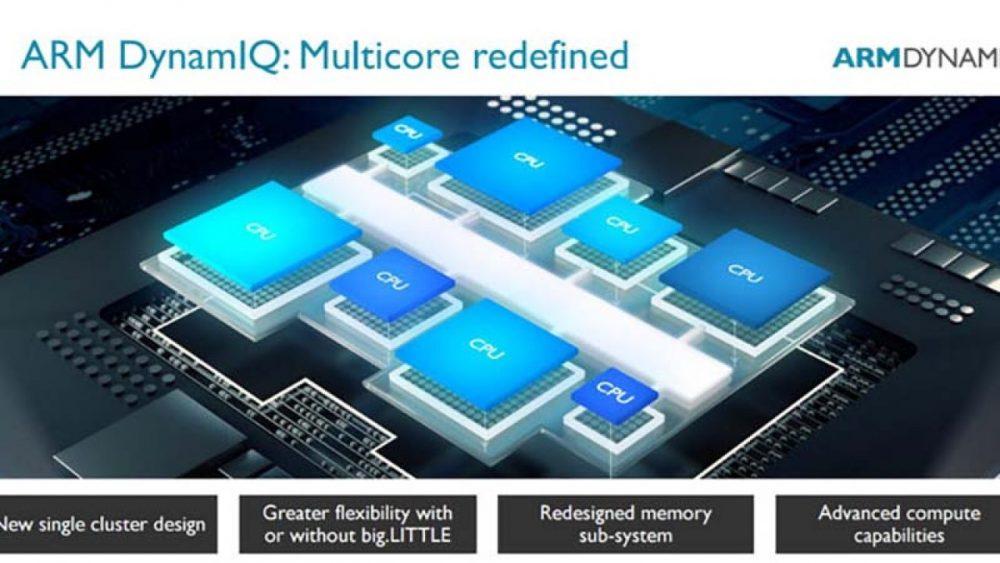

Den första etappen av DynamIQ är ett större klusterparadigm, vilket innebär upp till åtta kärnor för var och en av dem. Detta betyder dock att det också kan finnas en variabel kärndesign inom ett kluster; Dessa åtta kärnor kan vara helt olika från varandra och till och med från olika Cortex-A-familjer i olika konfigurationer.

Likheten med big.LITTLE är mer än tydlig, bara att istället för att ha "stora kärnor" och "små kärnor", här skulle det direkt tillåta att ha ett definierat antal kärnor och att var och en av dem var olika från alla kärnor . andra (detta är skillnaden med big.LITTLE, verkligen).

Många frågor uppstår här, till exempel hur cache-hierarkin tillåter trådar att migrera mellan kärnor i ett kluster (kanske liknar hur trådar migrerar mellan big.LITTLE kluster idag), även när kärnorna har olika cache-layouter. ARM har inte gått in i denna detaljnivå ännu, så det är fortfarande uppe i luften. Varje konfigurationskluster med variabel kärna kommer att vara en del av ett nytt tyg med ytterligare energisparlägen och målet är att ge mycket lägre latens.

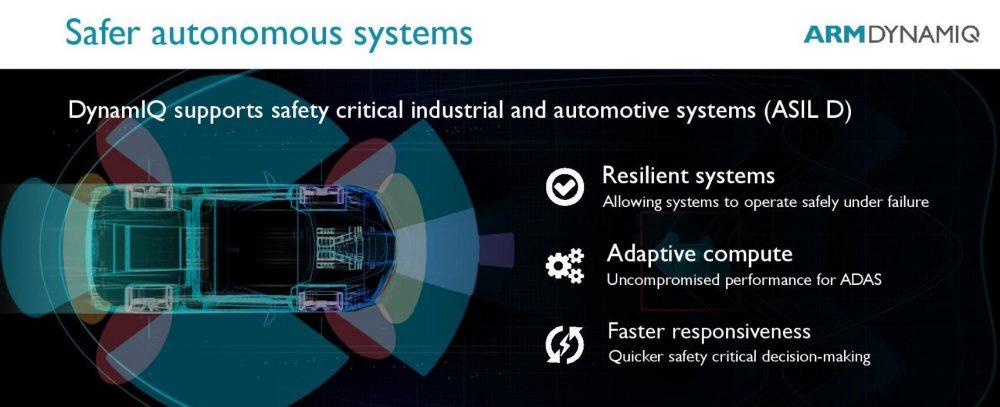

Den underliggande designen gör det också möjligt för varje kärna att styras oberoende för spänning och frekvens, liksom energisparande vilolägen. Enligt bilderna från ARM bör olika andra IP-block som acceleratorer kunna ansluta till detta tyg och dra nytta av den låga latensen; objekt som ARM citerar som säkerhetskritiska bilbeslut kan ha stor nytta av detta.

Ett av ARMs huvudsakliga fokusområden är redundans. Den nya strukturen gör det möjligt att använda ett till synes obegränsat antal kluster så att om en misslyckas kan de andra ta sin plats. Med detta sagt är den typ av redundans som vissa av ARM-chipskunderna kan behöva misslyckas i händelse av fysisk skada, som kan hända i en autonom bilolycka. Det blir intressant att se om visionen om ARM med DynamIQ sträcker sig till den nivån av redundans på SoC-nivån eller om denna typ av implementering beror på ARM-partner.

Tillsammans med det nya ramverket uppgav ARM att en ny design för minnessubsystem har implementerats för att hjälpa till med beräkningsfunktioner; emellertid nämns inget specifikt. På den ytterligare beräkningslinjen hävdar ARM att nya dedikerade processorinstruktioner (såsom begränsad precision) för AI och Maskininlärning kommer integreras i en variant av ARMv8-arkitekturen.

Vi är för närvarande inte säkra på om det här är en tillägg till ARMv8.2-A som introducerade medelprecision för databehandling, eller om det är en helt ny version. ARMv8.2-A lägger också till RAS-funktioner och minnesmodellförbättringar, vilket överensstämmer med den ”nya minnessubsystemdesignen” som nämns ovan. ARM har sagt att nya kärnor kommer att behövas för att göra processorer med denna arkitektur.

För tillfället fokuserar ARM DynamIQ på ny och framtida teknik som AI, fordonsindustrin och mixed reality, även om det är sant att det är uppenbart att DynamIQ kan användas i andra existerande modeller som surfplattor, smartphones, datorer och servrar. Detta beror, ja, på hur ARM gör det kompatibelt med nuvarande kärnkonstruktioner, eftersom de helt enkelt skulle kunna släppa det som en separat licens.