Smakämnen AMD Zen 4 -arkitekturen är den fjärde generationen av AMD Zen -arkitekturen och för med sig en rad viktiga förändringar jämfört med föregående generation och även en rad specifika nyheter. Alla med syftet att öka prestandan över Zen 3 och vara konkurrenskraftiga mot en Intel som lägger allt kött på grillen. Vad är nytt i AMD Zen 4 -arkitekturen? Vi förklarar det för dig.

Flera år har gått sedan AMD släppte sina första Ryzen 1000-processorer baserat på sin första generationens Zen-arkitektur. Vilket var en förändring av lycka för företaget som leds av Lisa Su och att AMD inte längre kommer att ses som ett varumärke med billiga processorer som alltid är i släp från Intel. Idag kan AMD -arkitekturer inte bara byta slag mot Intels, utan också överträffa dem i flera avseenden.

När det gäller Zen 3 har den antagit att AMD -sköldpaddan har tagit Intelharen. Som har insett faran med en AMD som har minskat marknadsandelarna i x86 -processorer i de olika segmenten av samma där de tävlar från dig till dig. Men trots sin eventuella fördel kan AMD inte låta sig sova på en marknad med ständiga förändringar och evolution där man ska vila på lagrarna är att direkt lämna loppet och till och med försvinna. Det är därför AMD har designat Zen 4 med viktiga förändringar jämfört med Zen 3 och som innehåller flera olika processorer.

Konfiguration av kärnorna i Zen 4

Zen -arkitekturen omfattar kärnorna i något som AMD kallar CCX, som består av en serie kärnor med följande egenskaper:

- Varje kärna har en privat första och andra nivå -cache, det vill säga att resten av kärnorna inte kan komma åt den.

- L3 -cachen är delad och alla har tillgång till den. Dessutom kommunicerar de olika kärnorna internt via ett nätverk av Infinity Fabric -gränssnitt.

- I Zen och Zen 2 består varje CCX av 4 kärnor och deras delade L3. I Zen 3 gick det från 4 till 8 kärnor. Zen 4 kommer att ha samma typ av konfiguration som Zen 3 och därför 8 kärnor per CCX .

En annan skillnad är att Zen 4 -arkitekturen är konstruerad för att byggas under TSMC: s 5nm -nod, som har andra designregler än sin 7nm -nod. Så varje chip som använder Zen 4 -kärnorna kommer att baseras på den tillverkningsnoden. Antingen en CCD -chiplet eller en monolitisk APU.

Zen 4-arkitekturen kommer att integrera AVX-512-instruktioner

Den första stora nyheten kommer att vara i stöd för AVX-512-instruktioner , som hittills varit exklusivt för Intel -processorer. Dessa instruktioner, som namnet antyder, är 512-bitars långa SIMD-instruktioner, de längsta hittills som har använts i en CPU med x86 -arkitektur. Dessutom innehåller AVX-512-instruktionerna olika tillägg för olika applikationer. AVX512 -tillägg som stöds av Zen 4 -kärnor? De är följande

- AVX512VL

- AVX512BW

- AVX512CD

- AVX512_IFMA

- AVX512DQ

- AVX512F

- AVX512_VPOPCNTDQ

- AVX512_BITALG

- AVX512_VNNI

- AVX512_VBMI2

- AVX512_VBMI

- AVX512_BF16

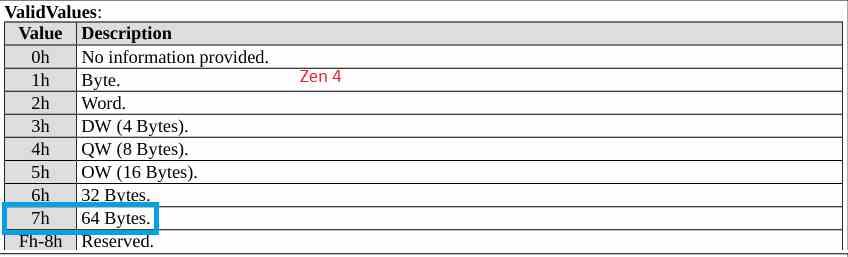

Dessutom förutsätter implementeringen av AVX-512-instruktionerna i Zen 4 att datacachelinjerna på första nivån och efterföljande cachennivåer har ökat storleken på cachelinjen från 32 till 64 byte eller 512 bitar . Vilket är viktigt för att samla in all data för en enda cykel AVX-512 instruktion. Denna lilla förbättring innebär inte bara stöd för AVX-512-instruktioner, utan bandbredden för CPU: s Load / Store-enheter har ökat och därmed processorns interna bandbredd. Dessutom betyder det att Zen 4 kan ladda 64 byte data direkt att det finns en ny AVX-512 enhet kan utföra dessa instruktioner i en enda cykel.

AVX-512-instruktionerna innehåller dock en begränsning och det är deras höga förbrukningsnivå. Detta kan få Zen 4 -processorerna att köra under sina vanliga klockhastigheter när du använder denna typ av instruktioner.

Cache -systemändringar i Zen 4 -arkitekturen

| Cache | AMD Zen 4 | AMD Zen 3 |

|---|---|---|

| L1-data | 32 KB 8-vägs | 32 KB 8-vägs |

| L1 Instruktioner | 32 KB 8-vägs | 32 KB 8-vägs |

| L2 | 1 MB 8-vägs | 512 KB 8-vägs |

| L3 | 32MB 16-vägs | 32MB 16-vägs |

| L1 ITLB (MMU) | 64 helt associativa ingångar | 64 helt associativa ingångar |

| L1 DTLB (MMU) | 512 ingångar 4.Way | 512 ingångar 4.Way |

| L2 ITLB (MMU) | 72 helt associativa ingångar | 64 helt associativa ingångar |

| L2 DTLB (MMU) | 3072 12-vägs biljetter | 2048 8-vägs biljetter |

Sedan den första AMD Zen har cache -systemet för AMD -processorer förblivit mer eller mindre detsamma. Med undantag för den sista nivån cache som delas av alla kärnor i CCD, men i fallet med Zen 4 kommer det att ske förändringar i vad som är cachestrukturen i själva kärnan, som du kan se i följande tabell.

Den första ändringen att markera är i L2 -cachen i varje kärna , detta kommer att öka kapaciteten hos 512 kB till 1 MB minne , vilket ökar chanserna att hitta data i cachen, men istället kommer L1- och L3 -cacheminnen att vara oförändrade i storlek. Naturligtvis, som vi har kommenterat tidigare, har storleken per cachelinje gått från 32 byte till 64 byte.

Det finns också ändringar i TLB eller översiktsutseende buffertar . De används av MMU i varje processorkärna för att översätta virtuella adresser till fysiska adresser. Som du kan se från tabellen som startar det här avsnittet, blick framåt-bufferten för datacachen på första nivån har ökat från 64 poster till 72 poster . Å andra sidan har L2 -cachen gått från 2048 poster till 3072 poster s. Detta representerar en ökning med 50% i detta avseende och inte bara i kapacitet, utan också i antal samtidiga åtkomster .

Stöd för RAM -minne via Compute Express Link

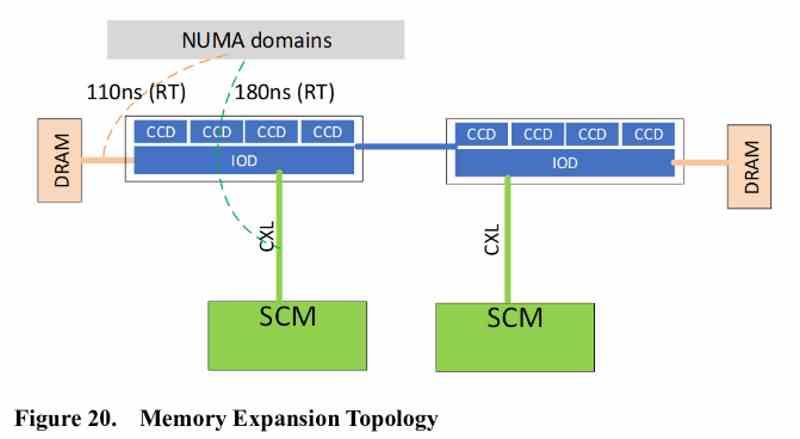

Det är här vi måste börja differentiera utbudet av processorer för bärbara datorer och stationära datorer från den framtida AMD EPYC under kodenamnet Genoa och det är att medan PCI Express 5.0 -standarden inte kommer att vara tillgänglig för processorer under socket AM5 det kommer att vara. på Zen 4-baserade AMD HEDT och server-processorer och med det stöd för CXL .

Nyckeln till CXL-standarden är att den ger minneskonsistens till PCI Express 5.0-gränssnittet, vilket innebär att minnesmoduler oavsett om de är icke-flyktigt minne, RAMeller en kombination av dessa kan inte bara anslutas via det klassiska minnesgränssnittet , men också via PCI Express -porten.

På marknaden finns det redan expansionsmoduler för RAM -minne via PCI Express med CXL, även kallat Storage Class Memory eller SCM. AMD kommer att integreras i sitt AMD EPYC Genoa möjligheten att utöka system -RAM via PCIe 5.0 -gränssnittet . Naturligtvis, med motsvarigheten till en högre latens för åtkomst till nämnda minne jämfört med DDR5, LPDDR5 eller någon annan typ av minne som är kompatibel med vilken AMD gör kompatibla processorer och APU: er med Zen 4 -arkitektur.

Användningen av två olika minnesbrunnar på fysisk nivå innebär också implementering av DMA -mekanismer för att kopiera data från de två minnesutrymmena , som, trots att de är enade på adresseringsnivå, inte är så på den fysiska nivån, vilket innebär att det behövs en mekanism för att kopiera data från ett RAM -utrymme till det andra.

Större intern och extern bandbredd

Det finns en detalj som inte har sagts i allt detta och det är att AMD använder sitt Infinity Fabric -gränssnitt för att kommunicera både internt och externt de olika komponenterna. OM gränssnitt med en bandbredd på 32 byte har använts för att kommunicera cacheminne med varandra i flera generationer AMD Zen och hoppet från 32 Bytes per cache -linje till 64 Bytes representerar också ett hopp i den aspekten och att mängden data som cirkulerar inuti CCD och CCX med Zen 4 -arkitekturen har fördubblats jämfört med Zen 3.

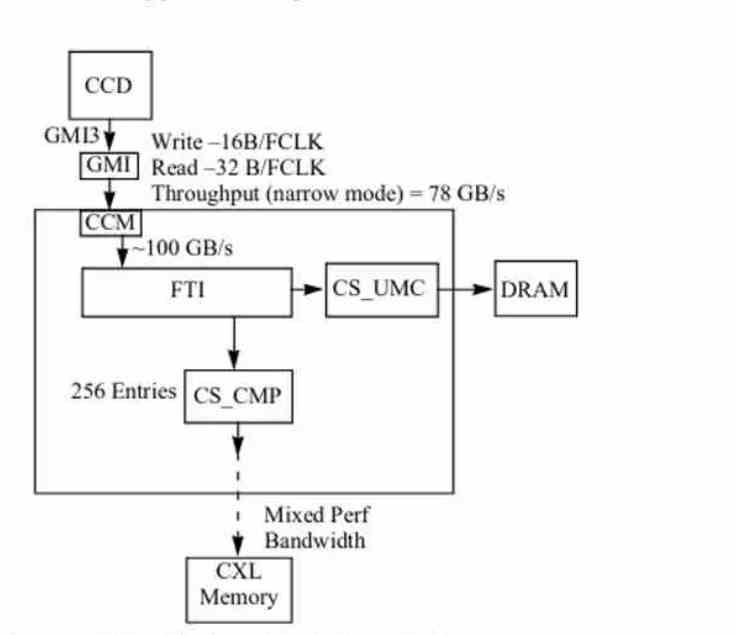

Men när det gäller kommunikation med Northbridge eller IOD, det verkar inte som att det kommer att bli förändringar och GM I -port som kommunicerar CCD Chiplets som innehåller Zen 4 -kärnorna kommer att fortsätta att ha en 16-byte / cykelbuss för skrivning och en 32-byte buss. / cykel för avläsning med IOD -klockfrekvens . Som vi kommer ihåg att i Zen -arkitekturen beror på klockhastighet för DRAM -regulatorn som används . I diagrammet som extrapolerar bandbredderna kan vi utläsa att klockhastigheten för IOD är 2400 MHz, vilket motsvarar memclk för DDR5-4800.

Vi kan inte glömma det IO Hub heller . Som också finns i IOD eller Northbridge och är ansvarig för att kommunicera med kringutrustning. Att vara en av delarna som också har fått förbättringar till följd av stödet från de nya I / O -gränssnitten. Som är fallet med USB4 och PCI Express 5.0. Så AMD har ökat sin bandbredd från 750 MHz till 1150 MHz .

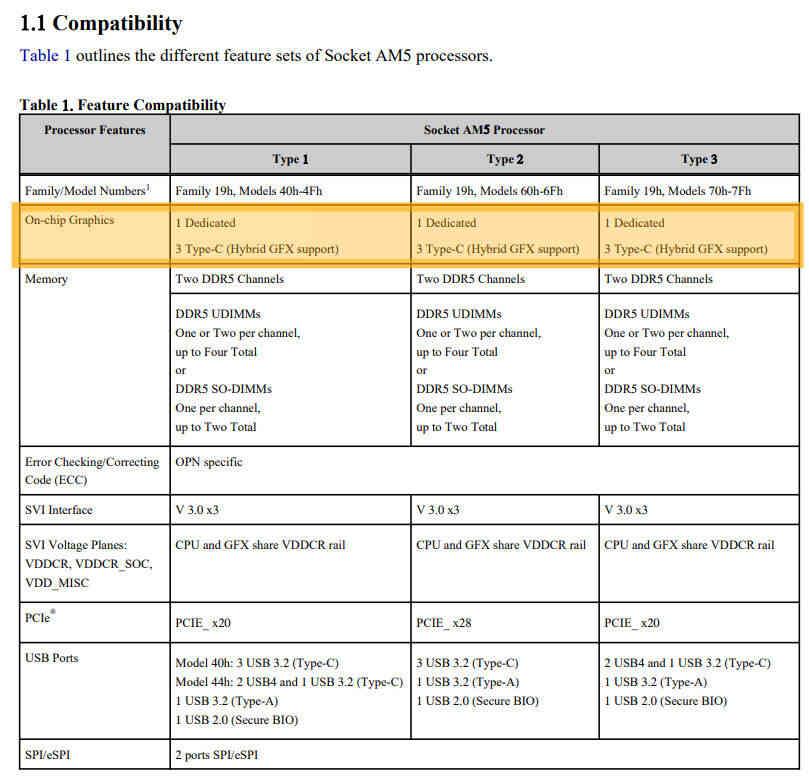

Som tjänar så att det maximala antalet PCIe 4.0 -körfält har gått från 24 rader till 28 rader . Detta innebär att moderkort tillverkare kan integrera en andra M.2 NVMe SSD eller ett USB 4 -gränssnitt . Naturligtvis kommer dessa 4 extra rader inte att finnas tillgängliga på alla Zen 4 -kompatibla chipset som kan ses i tabellen som följer med de två sista styckena.