Intel och AMD har meddelat användningen av 3DIC-teknik av alla slag för att bygga framtida processorer, en trend som kommer att växa under de kommande åren. Men hur kunde framtida Intel- och AMD-processorer byggas med denna teknik? I den här artikeln kommer vi att försöka belysa hur dessa framtida processorer kan vara.

När nya tillverkningsnoder används kan man se hur kostnaderna växer mer och mer, detta tvingar inte bara att ta nya strategier när det gäller utformningen av nya processorer utan också nya sätt att bygga dem.

Vad förstår vi som 3DIC?

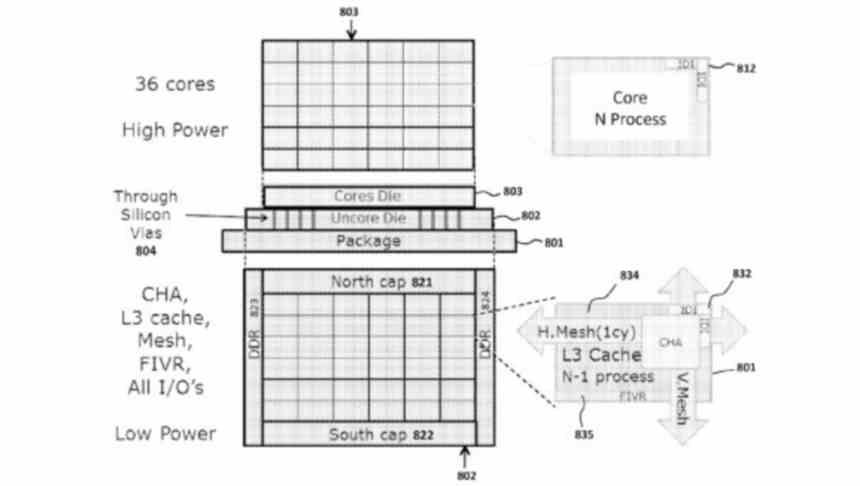

3DIC är förkortningen för en tredimensionell integrerad krets, vilket är namnet på alla processorer eller uppsättningar av samma som består av flera olika chips som är sammankopplade med varandra och använder vias genom kisel eller TSV. Hittills på marknaden för PC-hårdvarukomponenter har vi sett 3D-NAND-minnet från olika märken, liksom de olika generationerna av HBM-minne som bara demonstrationer

En av fördelarna med 3DIC är att vi kan använda flera marker med olika tillverkningsnoder på ett kombinerat sätt, detta är en fördel eftersom inte alla element i en processor behöver skalas till en ny tillverkningsnod, eftersom de inte ger en högre prestanda för dem.

Direkt dö-till-dö eller hur man bygger en komplex processor med hjälp av 3DIC

Tanken att ansluta två logikchips en-till-en i en 3DIC-struktur, med användning av en vertikal TSV-sammankoppling, har potential att helt förändra alla sektorer inom processorindustrin. Från SoC: er med mycket låg effekt som fungerar som den centrala processorn i din telefon till avancerade chips specialiserade på datacenter.

Idén att separera en processor i två eller flera vertikalt inriktade delar är något vi redan har sett i Intel Lakefield, där CPU kärnor och Northbridge är separerade från Southbridge på olika marker och använder tillverkningsnoder. annorlunda. Men vi bör börja titta på några modeller av SoC och till och med processorer.

Men Intel-arkitektur är inte det enda sättet att bygga en modern CPU med 3DIC-teknik, men det finns också en annan typ av konfiguration där CPU-kärnor och "uncore" för samma processor är uppdelade i två eller flera olika chips som är sammankopplade via TSV.

Den största utmaningen som CPU-arkitekter står inför just nu är energikostnaden för dataöverföring i processorn, som i en konfiguration vi pratar om minskar kraftigt, varför 3DIC inte bara kommer att bli framtida satsning för Intel och AMD utan också något som vi kommer att se i ARM världen.

En möjlig framtida 3DIC-processor av Intel eller AMD

För vårt exempel tar vi som exempel skrivbordsprocessorerna baserade på Zen 2 och Zen 3, som delar upp kärnorna i uncore, ett element som också kallas Northbridge, även om AMD kallar det Scalable Data Fabric. Vi kommer att använda den här arkitekturen eftersom den har en mycket tydlig uppdelning av komponenterna.

AMD, eller Intel, skulle kunna släppa en framtida processor där vi tycks se en monolitisk konfiguration, men verkligen vara en 3DIC-processor där uncore finns på ett annat chip i stacken än de olika kärnorna.

Detta skulle innebära att anslutningen mellan CCD och Chiplets med SDF inte bara skulle vara mer direkt och därför med mindre latens utan också konsumera mindre tack vare det faktum att det skulle vara möjligt för AMD eller Intel att använda ett större antal stift med lägre hastighet, men utan att förlora bandbredd för att kommunicera de olika kärnorna med resten av processorn, vilket i sin tur gör det möjligt att avsevärt öka prestandan per watt för de olika processorerna.

Tanken att separera processorerna i flera nivåer gör att saker som att bygga flerkärniga system som går utöver åtta kärnor på samma chip och interkommunikera dem alla i tillräcklig hastighet, med god latens och förbrukar mycket lite energi jämfört med nuvarande modeller.

Vilka handikapp möter Intel och AMD när de distribuerar 3DIC?

Den största avvägningen är den enorma kostnaden för att göra en 3DIC-processor, vilket kräver ytterligare tillverkningssteg, men den största avvägningen är vad som kallas termisk stalling, vilket uppstår när två komponenter är så nära att temperaturen på en. det påverkar prestandan hos en annan och tillåter inte att komponenter når klockhastigheter som de kan uppnå separat och till och med i en 3DIC-konfiguration.

Detta gör att dessa konfigurationer också kräver mycket mer komplexa och dyra kylsystem, vilket tillsammans tar bort dem från hemsystem och gör dem idealiska för servrar av alla slag, men paradoxalt nog är de också framtiden för SoCs för PostPC-enheter. De är begränsade i storlek och kan inte expandera mer horisontellt, så de kan bara göra det vertikalt.

Anledningen till detta är att med varje ny nod ökar inte bara kostnaden för varje skivmillimeter i kvadrat utan det blir allt svårare att bygga större och större processorer utan en farlig felfrekvens. Allt detta kommer att tvinga de flesta mönster att gå från att vara ett enormt monolitiskt chip till att bestå av flera vertikala marker, bara för att kostnaden per skiva kommer att vara så hög att även de höga kostnaderna för 3DIC-tillverkning inte kommer att vara ett hinder.