Если вы какое-то время следили за миром микропроцессоров, то наверняка вы знакомы с сокращениями RISC и CISC, которые являются не чем иным, как определением структуры набора инструкций, которые обрабатывает процессор. Что ж, в последние годы появилась новая парадигма, получившая название VISC. Из чего он состоит?

Большинство процессоров на рынке приелись, так как мало что приносят. Они основаны на улучшении производительности за счет корректировки мелких деталей, чтобы все работало лучше, чем раньше, но в последние годы не было революции, подобной той, которая произошла с нарушением порядка в середине 90-х годов, однако это может измениться. благодаря архитектурам VISC, которые представляют новую парадигму.

VISC - это набор инструкций?

Первое, что может прийти в голову при чтении этих сокращений и из-за их сходства, - это слова RISC и CISC, которые относятся к природе набора регистров и инструкций процессора, который не является предметом данной статьи, поскольку Под концепцией VISC мы имеем в виду не новый способ категоризации инструкций, а нечто совершенно иное.

Чтобы понять, как работает парадигма VISC, мы должны принять во внимание две разные концепции, касающиеся ЦП представление. Первая из них заключается в том, что современные процессоры ПК имеют внутренний набор инструкций даже меньше, чем RISC, поскольку они передают каждую из инструкций в более мелких микрокомандах внутри во время процесса. фаза декодирования. Если мы пуристы, то сегодня вывод: все процессоры не в том, что они RISC, а в том, что у них очень сокращенный набор инструкций, которые работают внутри и служат для построения остальных инструкций. То есть, как только инструкция достигает блока управления ЦП, она разбивается на список инструкций.

Таким образом, война между RISC и CISC была выиграна первым, но с той ловушкой, что x86, наиболее широко используемая архитектура CISC, превратила в ловушку внутреннее поведение как RISC. По сей день, кроме ARM, остальные ISA RISC отсутствуют или находятся на грани исчезновения. Более того, даже ARM приняла концепцию разделения инструкций на более простые, так что обе парадигмы, помимо определения общего ISA семейства, уже исчезли.

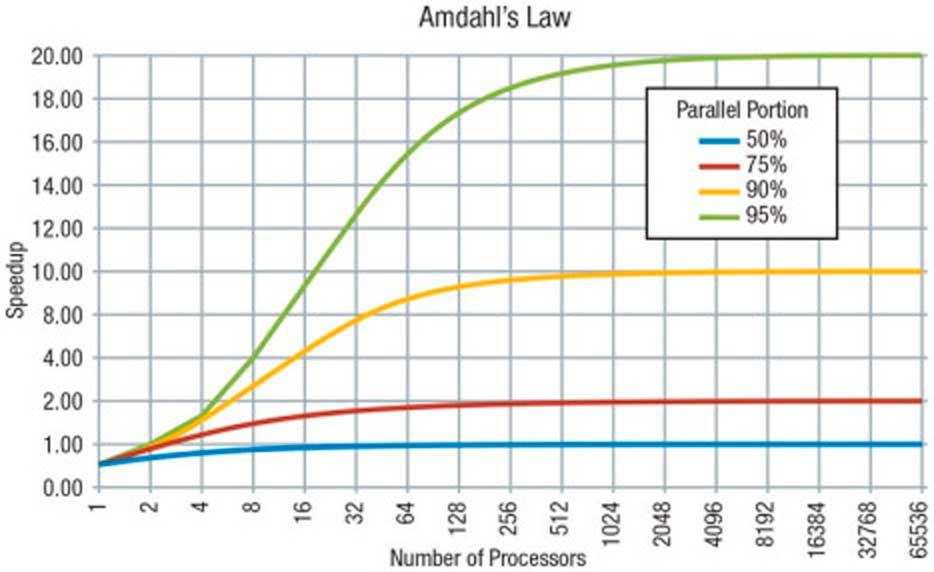

Закон Амдала

Чтобы понять программу, мы должны понимать, что программа состоит из двух частей:

- Тот, который может выполняться только последовательно и, следовательно, может быть решен только одним ядром, выполняя одно ядро исполнения.

- Та часть кода, которая может выполняться параллельно, что означает, что она может быть решена несколькими ядрами одновременно, и чем больше их в процессоре, тем быстрее эта часть будет решена.

Если мы примем во внимание то, что было объяснено в предыдущем разделе, то вы сделаете вывод, что некоторые из инструкций процессора, которые становятся микрокодом, то, что они делают, становятся последовательностью инструкций, которые могут работать последовательно или параллельно между несколькими ядрами, хотя обычно что большая часть инструкций выполняется в одном ядре и что код выполняется параллельно с помощью общих элементов.

Следовательно, тот факт, что часть кода выполняется несколькими ядрами, зависит исключительно от разработчика программы, который должен явно запрограммировать ее так, чтобы определенные части работали параллельно.

VISC и виртуальные ядра

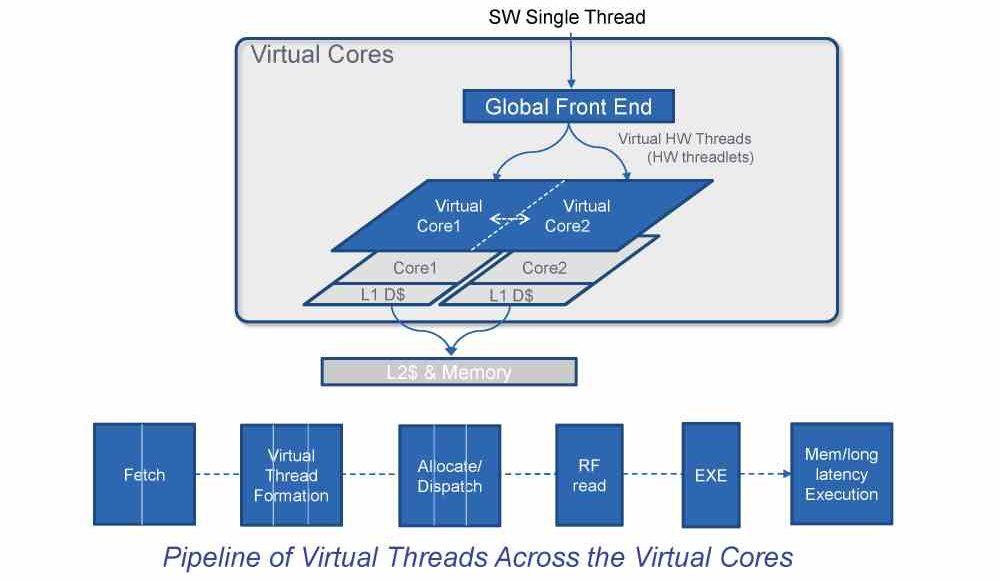

После того, как мы объяснили все вышесказанное, мы можем объяснить, что означает аббревиатура VISC, определение которой является прямым ответом на следующий вопрос: разве они не работают при создании микрокоманд на этапе декодирования? параллельно с несколькими ядрами вместо того, чтобы делать это одновременно?

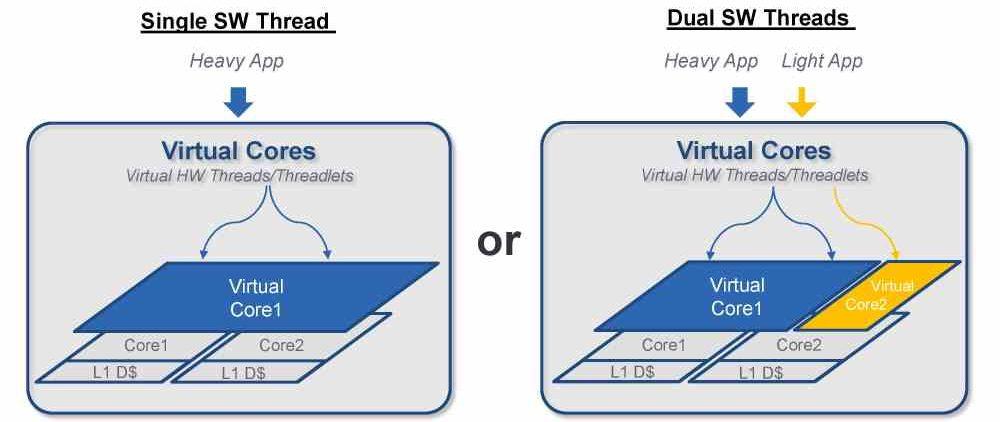

Что ж, ответ на вопрос об архитектуре VISC, который впервые был задан компанией Soft Machines в 2015 году как концепция повышения производительности процессора. Этот небольшой стартап был куплен Intel в 2016 году, и с тех пор они работают над разработкой архитектуры VISC. Как это работает? Что ж, это можно определить очень легко: один поток выполнения отправляется на глобальный интерфейс процессора, который преобразуется в несколько, которые выполняют одну и ту же функцию, работают параллельно и работают в виртуальных ядрах. Процесс преобразования выполняется на программном уровне через уровень трансляции, но мы должны помнить, что это может быть что-то столь же простое, как микроконтроллер, выполняющий передачу инструкций.

В отличие от того, что происходит при распределении задач в обычном многоядерном процессоре, в архитектуре VISC не предполагается, что ядро может свободно выполнять инструкцию, но что элементы для ее выполнения доступны в процессоре для ее выполнения. Например, может случиться так, что в обычном ядре векторная единица не используется, но в этой парадигме ее можно использовать для формирования одной из инструкций.

VISC и производительность

При принятии новой парадигмы с точки зрения архитектуры первое, что нужно учитывать, - это то, как она влияет на производительность, поскольку не стоит менять текущую парадигму, если это не приводит к увеличению общей производительности процессора. Самый классический способ повысить производительность процессора - это увеличить количество инструкций, которые выполняются за такт, что означает усложнение аппаратного обеспечения из-за того, что при добавлении ядер мы должны учитывать всю инфраструктуру, которая окружает их, что становится таким же или более сложным.

Что отличает VISC от остальных, так это не что иное, как распределение ресурсов процессора для выполнения различных инструкций за несколько тактов, от 1 до 4 ядер. Таким образом, если есть две инструкции, конкурирующие за другие ресурсы в ядре, то их можно очень быстро переназначить другой части процессора, где эти же ресурсы доступны.

Текущая парадигма, которая представляет собой выполнение не по порядку, что она делает, это переупорядочивает выполнение инструкций в соответствии с свободными ресурсами в любое время, а затем переупорядочивает вывод уже обработанных данных. Ограничение? Распределение ресурсов выполняется на одноядерном, а не на многоядерном уровне, и это ключ к более высокой производительности архитектур VISC.

Существуют ли эти процессоры сегодня?

Хотя концепция очень хороша на бумаге, никто еще не представил процессор, работающий в соответствии с этой парадигмой, но, учитывая, что мы постепенно приближаемся к пределам текущей парадигмы, важно помнить, что есть решения, которые могут служить для повышения производительности ЦП наших ПК в будущем.

Наличие более мощного процессора - это не только наличие более быстрого или большего числа ядер, но и знание того, как использовать в своих интересах доступные ресурсы. Выполнение вне очереди было первым шагом в этом смысле, однако с тех пор, помимо перехода на многоядерность, изменения были в основном незначительными. VISC по-прежнему является концепцией, однако она не является невозможной, и это способ гораздо более эффективно использовать ресурсы, доступные в процессоре.

Пока мы знаем, что эта концепция возможна в ЦП, поскольку Soft Machines разработала и построила процессор с этой парадигмой, поэтому, хотя это было на экспериментальном уровне, мы знаем, что такое проектирование возможно. Другое отличие состоит в том, что сложно привести весь набор инструкций и регистров x86 к этой парадигме, которая по своей природе чрезвычайно сложна.