Значительная часть возможностей наших ПК основана на разделении работы, когда несколько элементов совместно выполняют часть кода для работы с ней. Но иногда возникают конфликты в доступе к данным и инструкциям, которые становятся проблемой производительности. Один из способов исправить это - транзакционная память.

Одна из самых больших проблем с многоядерностью ЦП Системы, которые используют наши ПК, заключается в том, что они основаны на модели фон Неймана, которая заключается в том, что имеется только одна общая память. По мере увеличения количества исполнительных блоков, ядер, потоков и других элементов, которые работают параллельно в ЦП, увеличивается. Между ними возникает все больше и больше конфликтов. Не только в доступе к данным, но и к информации, содержащейся в различных адресах памяти, и, следовательно, к значениям переменных, используемых программами. Есть много способов избежать этих конфликтов, один из них - транзакционная память, которую мы собираемся описать в этой статье.

Введение в проблему

При написании программы она кодируется серией инструкций, которые, по-видимому, выполняются последовательно. Но уже при параллелизме инструкций с одним ядром в середине выполнения могут входить разные исполнительные единицы. К этому мы должны принять во внимание, что выполнение не по порядку добавляет сложности, поскольку доступ к памяти и данным во время выполнения осуществляется беспорядочно.

При большом количестве запросов возникает конкуренция за доступ к одной и той же памяти. Это приводит к тому, что запросы задерживаются все дольше и дольше, увеличивая задержку памяти с ЦП при выполнении определенных инструкций и влияя на пропускную способность. Для этого существуют механизмы, которые максимально избегают этих конфликтов при доступе к памяти, таким образом, чтобы процессы обращались к памяти из упорядоченной памяти. Это позволяет избежать конфликтов при изменении данных в своей иерархии, а также уменьшить проблемы конкуренции и, как следствие, задержку доступа.

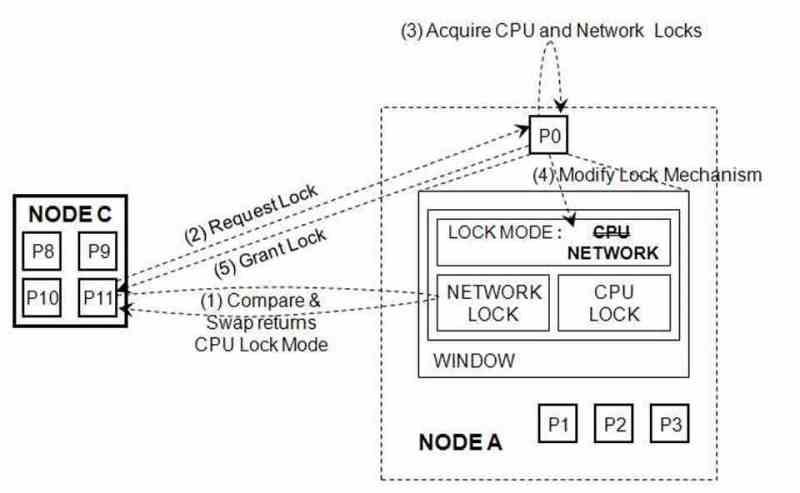

Самый простой способ добиться этого - использовать блокировки, которые представляют собой участки кода, в которых мы отмечаем, что они не должны выполняться одновременно разными потоками ЦП. То есть за эту часть кода может отвечать только одно его ядро. Итак, мы сделали блокировку для остальных ядер, и остальные смогут начать выполнение только тогда, когда будет достигнута инструкция, завершающая блокировку. Что произойдет, когда будет завершена часть кода, выделенная для всех ядер, кроме одного.

Что такое транзакционная память?

Один из способов избежать проблем, описанных в предыдущем разделе, - использовать транзакционную память. Это не тип памяти или хранилища, поэтому мы не говорим о чистом оборудовании. Его происхождение находится в транзакциях баз данных, это тип инструкций, выполняемых в модулях Load-Store.

Система транзакций в процессоре работает следующим образом:

- Создается копия части памяти, к которой хотят получить доступ несколько ядер, по одной для каждого экземпляра.

- Каждый экземпляр изменяет свою личную копию независимо от остальных частных копий.

- Если данные были изменены в частной копии, а не в остальных, то модификация также копируется в остальные частные копии.

- Если два экземпляра вносят изменения в одни и те же данные в одно и то же время, и это создает несогласованность в данных, то обе частные копии удаляются. а частные копии остальных копируются

Четвертый момент важен, поскольку именно в этой части становится ясно, что необходимо сериализовать эту часть кода. Это означает, что остальные экземпляры перестают изменять свои личные копии, и изменения вносятся только одним из экземпляров. Когда он заканчивается, изменения копируются в остальные частные копии. Когда часть кода, помеченная как транзакционная, уже выполнена и все частные копии содержат одинаковую информацию, результат копируется в соответствующие строки кэша и адреса памяти.

Системы транзакционной памяти Intel TSX

Аббревиатура TSX, Расширения транзакционной синхронизации, относится к серии дополнительных инструкций для x86 ISA, которые предназначены для добавления поддержки транзакционной памяти в Intel ЦП. Следовательно, это серия инструкций и связанных с ними механизмов, которые позволяют разграничивать определенные разделы кода как транзакционные, а ЦП Intel может выполнять процесс, который мы обсуждали в предыдущем процессе. Но в этом случае реализация Intel немного сложнее. Поскольку, как мы видели ранее, в случае конфликта между двумя данными весь процесс прерывается одним из запущенных экземпляров.

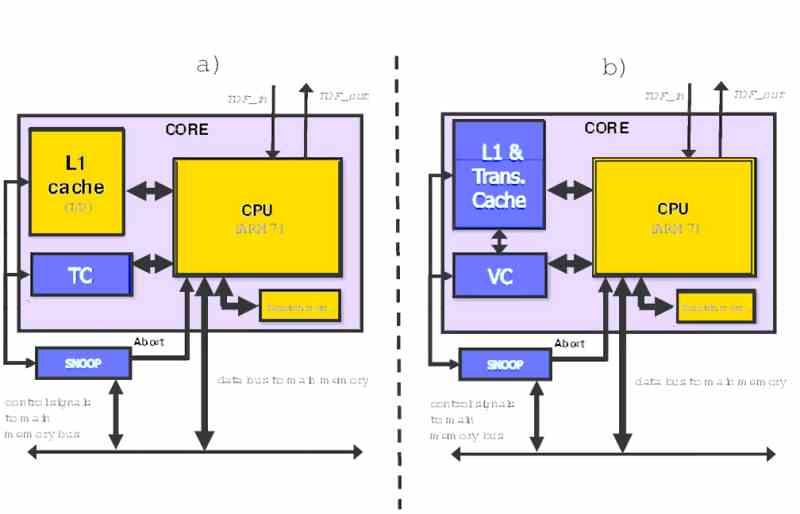

Его реализация на аппаратном уровне достигается за счет добавления нового типа кеша, называемого кешем транзакций, в котором различные операции выполняются с разными данными. Имейте в виду, что транзакционная память стремится уменьшить количество конфликтов при доступе к памяти. Хотя кеши поддерживают большее количество запросов, чем Оперативная память как правило, они также ограничены, особенно на уровнях, наиболее удаленных от ядер. Все это сочетается с использованием внутренней памяти и частных регистров, которые служат поддержкой частных копий, выполняемых различными ядрами.

Инструкции Intel TSX не являются сложным набором, у нас есть, с одной стороны, инструкция XBEGIN, которая отмечает нас, когда начинается транзакционный раздел памяти, инструкция XEND, которая отмечает конец, и XABORT, которая служит для отметки выхода из процесса. при возникновении исключительной ситуации.

Конец инструкций Intel TSX?

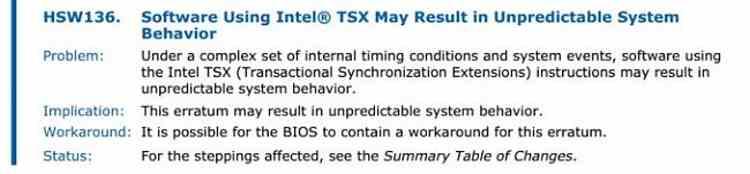

Сегодняшние блоки управления ЦП на самом деле представляют собой полноценные микроконтроллеры, это означает, что способ декодирования инструкций и список инструкций могут быть обновлены. Intel сделала первую реализацию на архитектуре Haswell, и до сих пор она оставалась в составе процессоров Intel. Поскольку недавно он был отключен с помощью прошивки на собственных ядрах Intel шестого, седьмого и восьмого поколений.

Время от времени Intel выполняет удаленные обновления своих ЦП, которые выполняются через Intel Management Engine, который у нас есть на нашем ПК, без нашего ведома. Обычно они не распространены, но могут включать оптимизацию выполнения определенных инструкций или даже исключение поддержки других. Устранение Intel TSX в Intel Core связано с тем, что с последними модификациями внутреннего микрокода блока управления это подразумевает конфликт в работе программного обеспечения, что означает, что ЦП не работает должным образом.

Но настоящая причина в том, что Intel TSX позволяет запускать вредоносный код под радаром классических систем безопасности, особенно тот, который влияет на операционную систему. Поскольку частные копии не соответствуют среде пользователя или операционной системе. Так что это все еще проблема, аналогичная проблеме спекулятивного исполнения.