Технология PCI Express уже давно используется для подключения видеокарт и других периферийных устройств, таких как твердотельные накопители NVMe. Реализация интерфейса пятого поколения происходит с приходом процессоров Alder Lake от Intel и процессоры Zen 4 от AMD. Но спецификация PCI Express 6.0 была доработана и содержит несколько улучшений по сравнению с пятым поколением.

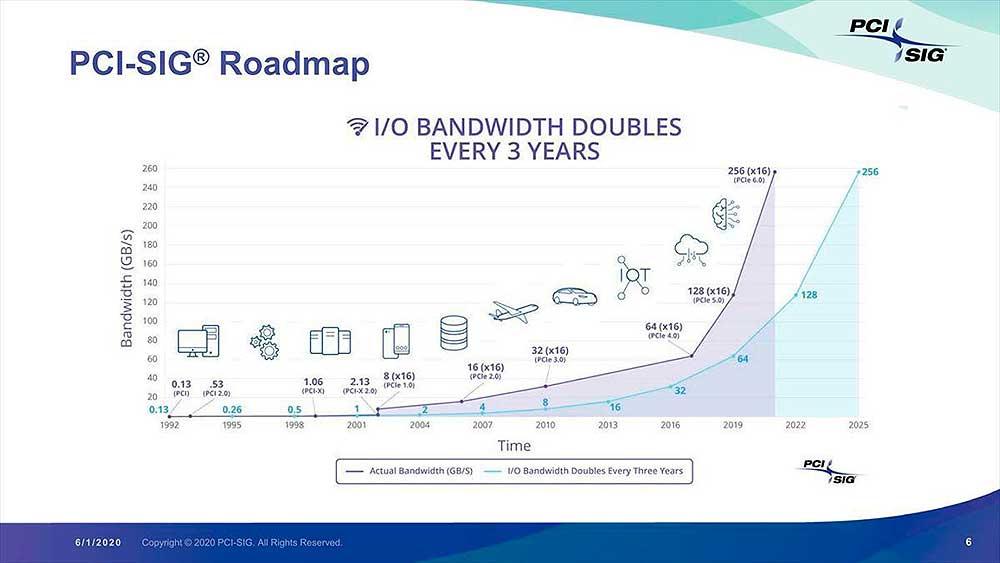

PCI Express 6.0 с самого начала следует тем же улучшениям, что и предыдущие поколения этого интерфейса, то есть он основан на удвоении пропускной способности по сравнению с предыдущим поколением. Однако в случае с PCI Express 6.0 потребовались глубокие изменения при разработке шестого поколения этого интерфейса.

Пропускная способность PCI Express 6.0 составляет 128 ГБ / с для 16-строчного интерфейса, что является преувеличенно высокой пропускной способностью для интерфейса ввода-вывода, и это четырехкратный скачок по сравнению с текущим PCI Express 4.0, который мы используем для текущей графики. карты. Скачок также означает прыжок из NVMe SSD флэш-контроллеры от 7-8 ГБ / с до 28-32 ГБ / с с PCI Express 6.0.

Обратная совместимость и проблема нестабильности сигнала

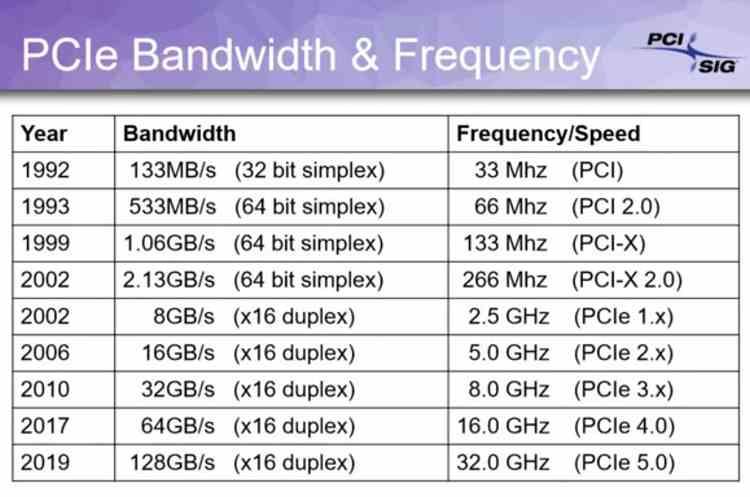

Интерфейс PCI Express всегда был обратно совместим с предыдущими версиями протокола, это означает, что мы можем вставить карту PCI Express 1.0 в слот PCI Express 6.0, и она будет работать, потому что вывод будет точно таким же. Таким образом, невозможно увеличить количество контактов для увеличения пропускной способности без увеличения скорости. Решение? Увеличьте тактовую частоту, с которой работает интерфейс.

Проблема с PCI Express 6.0? По мере того, как мы увеличиваем тактовую частоту интерфейса, он становится более нестабильным с расстоянием, и после шести поколений им пришлось вносить изменения в интерфейс из-за высокой скорости, с которой интерфейс работает традиционным образом. И если вы посмотрите на таблицу, которая сопровождает эти строки, мы говорим о теоретической скорости 64 ГГц, что достаточно искажает сигнал, даже на небольшом расстоянии оба конца находятся в интерфейсе PCI Express.

Это вынудило принять ряд мер, чтобы сделать возможным переход на PCI Express 6.0.

Первое из улучшений в PCI Express 6.0, использование PAM4

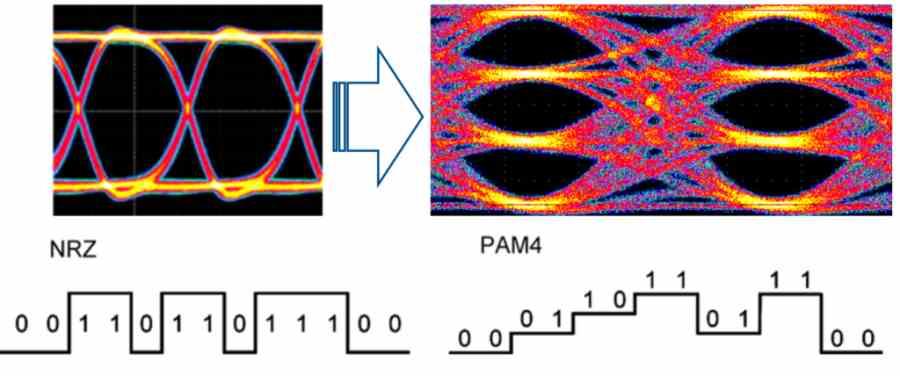

Как внешний или внутренний интерфейс микросхемы узнает, какое значение имеет значение: 1 или 0? Ну просто, в зависимости от напряжения, в котором передается информация. Бинарные системы основаны на использовании двух напряжений с достаточным расстоянием между ними, чтобы падение или повышение напряжения не приводило к путанице в сигнале. В аналоговых системах простое изменение напряжения предполагает изменение информации. По этой причине компьютеры говорят в двоичном формате.

При чем здесь PCI Express 6.0? Поскольку мы не можем увеличить полосу пропускания, потому что сигнал искажен, а не количество контактов для обратной совместимости, необходимо найти решение, и для этого нужно использовать кодирование PAM4 или амплитудно-импульсную модуляцию, которые мы уже видели в GDDR6X и основан не на использовании двух значений напряжения, а на использовании 4 значений напряжения для каждого контакта. Таким образом мы можем кодировать значения 00, 01, 10 и 11 на каждом выводе. Всего четыре значения вместо двух классических значений, равных 0 или 1.

Решение позволяет избежать увеличения пропускной способности и количества выводов, но оно говорит нам, что в PCI Express 7.0 это больше невозможно с помощью обычных методов. Мы можем увидеть использование фотоники и оптических интерфейсов, но с улучшениями PCI Express 6.0, только что появившимися из духовки, лучше подождать с его преемником.

Изменения в системе пакетов

Переход к PAM-4 изменил способ отправки пакетов интерфейсом PCI Express 6.0, несмотря на то, что он совместим с предыдущими поколениями, обмениваясь данными в традиционном режиме PAM-2 или NRZ. Реальность такова, что формат PAM-4 не поддерживает предыдущую пакетную систему, и поэтому протокол связи изменился из-за этого.

Первым изменением стало так называемое прямое исправление ошибок или FEC, новый протокол для исправления ошибок при отправке данных. Проблема в том, что обрабатываемая полоса пропускания настолько высока, что FEC добавляет огромную задержку при отправке данных. Чтобы облегчить это, стандарт PCI Express 6.0 использует тип пакета под названием FLIT. Пакет - это не что иное, как набор битов с определенным местом назначения. Задержка отправки каждого FLIT? Это зависит от количества линий на интерфейсе, но каждый пакет имеет задержку всего 2 нс на 16-строчном PCI Express 6.0, но достигает 32 нс на однолинейном интерфейсе.

FEC работает только с фиксированными размерами, поэтому FLIT имеет размер 256 байт на отправку. Каждый пакет или TLP может иметь размер от 0 до 4096 байтов, и поэтому каждый пакет может состоять из нескольких FLITS.

Третье обновление до PCI Express 6.0, переменное потребление

PCI Express 6.0 добавляет новое состояние низкого энергопотребления, получившее название L0P. Этот режим позволяет интерфейсу снизить энергопотребление, когда передаваемый поток данных меньше, чем интерфейс может передать. Для этого изменяется тактовая частота, с которой интерфейс работает в определенные моменты передачи данных, и все это без остановки, которая увеличивает задержку передачи данных.

Проблема в том, что этот механизм связан с FLITS и FEC и, следовательно, с PAM4, что означает, что его можно использовать только в режиме PCI Express 6.0, но не в других режимах.