Концепция Cache DRAM заключается в добавлении дополнительного уровня кеша между процессором и Оперативная память память в целях повышения производительности первого. Но какие изменения это означает в архитектуре процессора и как работает эта концепция? Мы объясняем вам и попутно, какие процессоры будут использовать эту архитектуру.

Несколько дней назад Apple появился патент, в котором упоминалось использование Cache DRAM в одном из будущих процессоров, концепция, которая, хотя и может показаться экзотической, не является, поэтому мы собираемся демистифицировать ее.

Память DRAM как кэш, противоречие

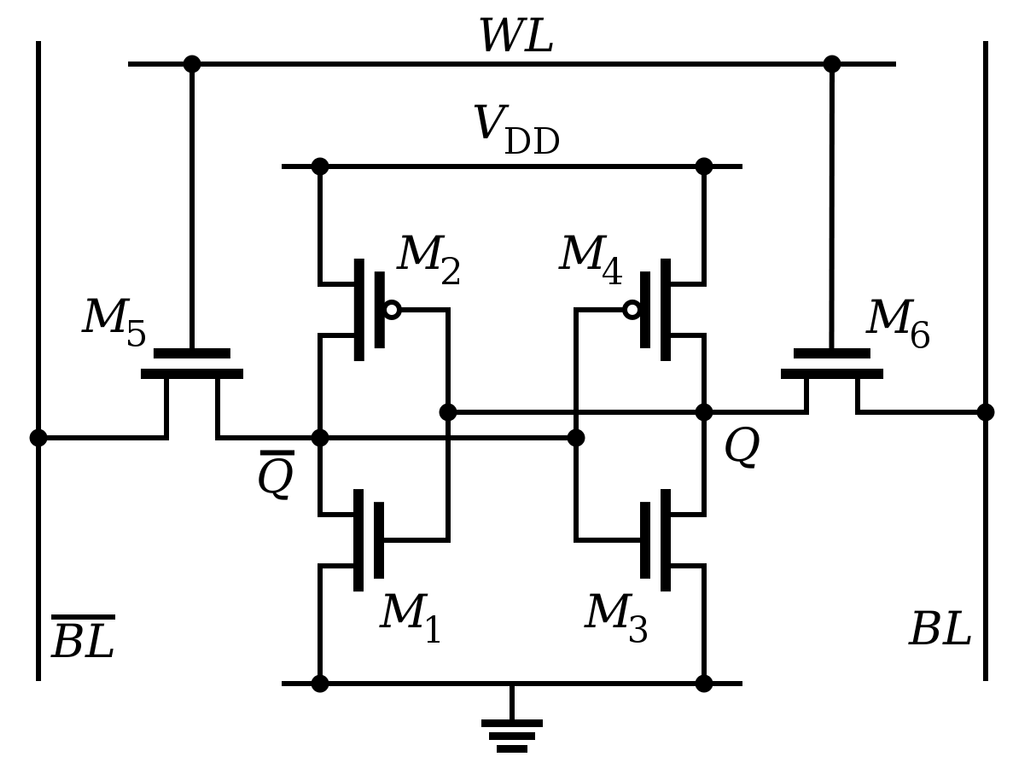

Вся текущая память RAM, которая используется вне процессора, относится к типу DRAM или Dynamic RAM, тогда как память, которая используется внутри процессоров, является статической RAM или SRAM. Оба работают примерно одинаково с точки зрения доступа к данным, но они не одинаковы в том, как они хранят немного памяти.

Память DRAM намного дешевле, но по своей природе требует постоянного обновления, а ее скорость доступа ниже, чем у SRAM, поэтому она обычно не используется в процессорах. С другой стороны, он масштабируется хуже, чем DRAM, поэтому, несмотря на то, что IBM использовала память DRAM в качестве кэша последнего уровня в своих процессорах для высокопроизводительных вычислений, POWER, в следующем поколении они будут использовать SRAM. объем памяти.

Таким образом, концепция кеш-памяти, которая связана с памятью типа SRAM, вместе с концепцией DRAM в принципе не совпадают, и хотя мы имеем дело с процессорами IBM, мы не будем говорить об использовании памяти DRAM в качестве кеша внутри процессор.

Кэш DRAM и память HBM в качестве примера

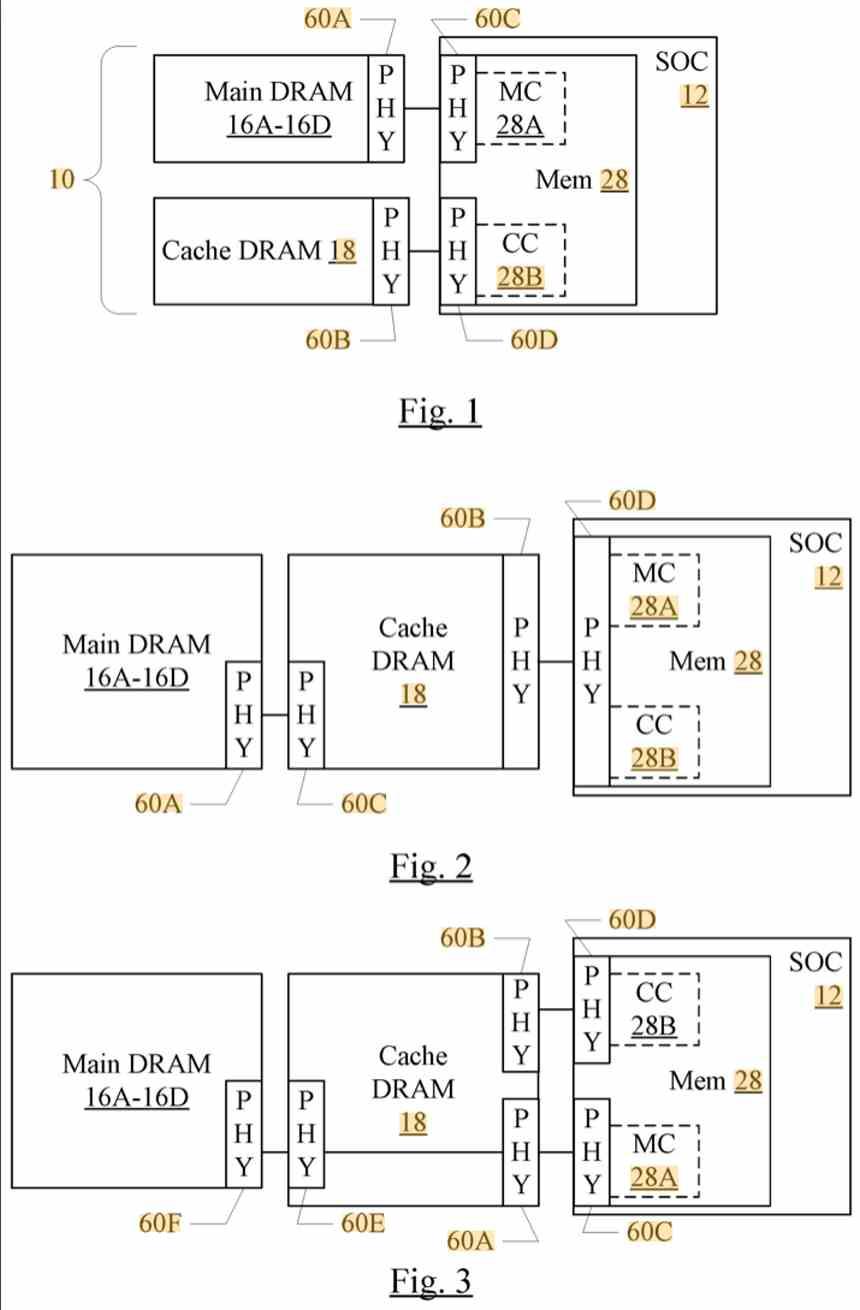

Кэш-память DRAM - это концепция добавления дополнительного уровня в иерархию памяти между кешем последнего уровня процессора и основной системной памятью, но построенная через память DRAM с более высокой скоростью доступа и меньшей задержкой, чем DRAM, используемая в качестве основной памяти.

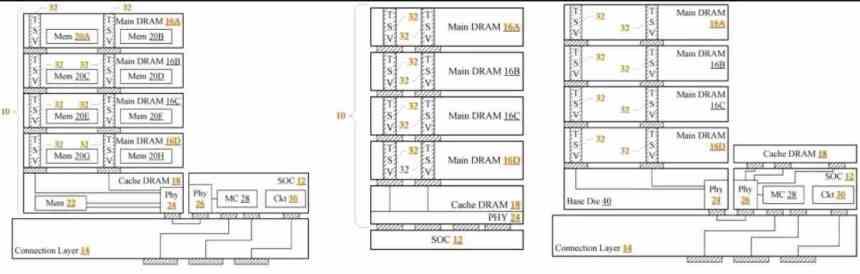

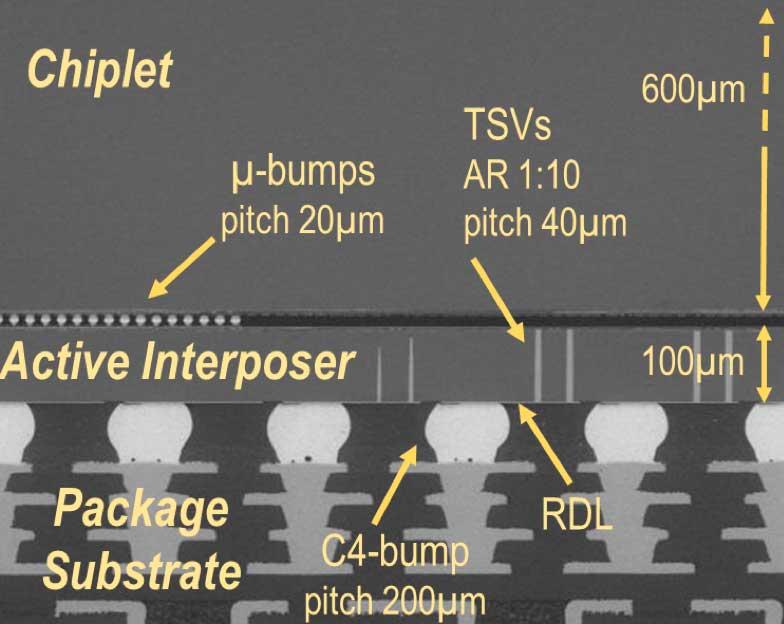

Одним из способов достижения этого является использование памяти типа HBM в качестве кеш-памяти DRAM, которая представляет собой тип памяти DRAM, в которой разные микросхемы памяти уложены и соединены вертикально с помощью кабеля, называемого TSV, или сквозных путей. кремний тем, что они проходят сквозь микросхемы. Этот тип подключения также используется для построения памяти 3D-NAND.

Поскольку соединение вертикальное, необходим переходник, который представляет собой часть электроники в виде платы, которая отвечает за связь между процессором и памятью HBM. Оба процессора, будь то ЦП or GPU / ГРАФИЧЕСКИЙ ПРОЦЕССОР, установлены на указанном переходнике, что из-за небольшого расстояния дает памяти HBM возможность функционировать как тип памяти DRAM с более низкой задержкой, чем классическая память DDR и GDDR.

Следует пояснить, что если бы DRAM находилась ближе к процессору, поскольку конфигурация 3DIC помещает ее чуть выше него, то уровень задержки по сравнению с памятью HBM был бы ниже, а, следовательно, и скорость доступа выше, из-за того, что электроны имеют путешествовать на меньшее расстояние.

Мы действительно использовали память HBM, чтобы дать вам представление, но в качестве примера работает любой тип памяти в конфигурации 2.5DIC.

Но стандартного интерпозера недостаточно

Следующая проблема заключается в том, что кэш не работает так же, как оперативная память, поскольку система поиска данных процессора не копирует строки команд из ОЗУ одну за другой, а скорее систему памяти. Кэш копирует фрагмент памяти, в котором текущая строка кода находится на последнем уровне кеша.

На последнем уровне хранится кеш процессора, который используется всеми ядрами, но по мере приближения к первому уровню они становятся более частными. Следует уточнить, что в порядке убывания каждый уровень кеша содержит фрагмент предыдущего кеша. Когда процессор ищет данные, он ищет их в порядке возрастания уровней кэша, где каждый уровень имеет большую емкость, чем предыдущий.

Но для того, чтобы память HBM вела себя как кеш-память, нам нужен элемент, который связывает процессор с указанной памятью, промежуточное устройство, чтобы иметь необходимую схему, чтобы вести себя как кэш-память. Таким образом, обычный преобразователь нельзя использовать, и необходимо добавить в него дополнительную схему, которая позволяет памяти HBM вести себя как дополнительный кэш памяти.