Dacă ai urmărit de ceva vreme lumea microprocesoarelor, cel mai sigur lucru este că vei fi familiarizat cu acronimele RISC și CISC, care nu sunt altceva decât o definiție a structurii setului de instrucțiuni pe care le gestionează un procesor. Ei bine, în ultimii ani a apărut o nouă paradigmă care a fost numită VISC. În ce constă?

Majoritatea procesoarelor de pe piață au devenit plictisitoare, deoarece aduc puțin pe masă. Acestea se bazează pe îmbunătățirea performanțelor prin reglarea pieselor mici, astfel încât întregul să funcționeze mai bine decât înainte, dar în ultimii ani nu a existat o revoluție ca cea care a avut loc odată cu execuția necorespunzătoare la mijlocul anilor 90, totuși acest lucru s-ar putea schimba datorită arhitecturilor VISC, care reprezintă o nouă paradigmă.

Este VISC un set de instrucțiuni?

Primul lucru care poate veni în minte la citirea acestor acronime și datorită asemănării lor sunt cuvintele RISC și CISC, care se referă la natura setului de registre și instrucțiuni ale procesorului, care nu face obiectul acestui articol, întrucât sub conceptul VISC nu ne referim la un nou mod de a clasifica instrucțiunile, ci la ceva total diferit.

Pentru a înțelege cum funcționează paradigma VISC, trebuie să luăm în considerare două concepte diferite în ceea ce privește Procesor performanţă. Primul dintre acestea este faptul că CPU-urile PC au astăzi un set intern de instrucțiuni chiar mai mic decât RISC, deoarece ceea ce fac este să transfere fiecare dintre instrucțiuni în microinstrucțiuni mai mici intern în timpul procesului. faza de decodare. Dacă suntem puriști, concluzia astăzi toate procesoarele nu este că sunt RISC, ci că au un set foarte redus de instrucțiuni care funcționează intern și care servește la construirea restului instrucțiunilor. Adică, de îndată ce o instrucțiune ajunge la unitatea de control al procesorului, aceasta este împărțită într-o listă de instrucțiuni.

Deci războiul dintre RISC și CISC a fost câștigat de primii, dar cu capcana că x86, cea mai folosită arhitectură CISC, a făcut capcana de a se comporta intern ca un RISC. Până astăzi, cu excepția ARM, restul ISA RISC sunt dispărute sau pe cale de dispariție. În plus, chiar și ARM a adoptat conceptul de împărțire a instrucțiunilor în altele mai simple, astfel încât ambele paradigme în afara definirii ISA comun al unei familii sunt deja dispărute.

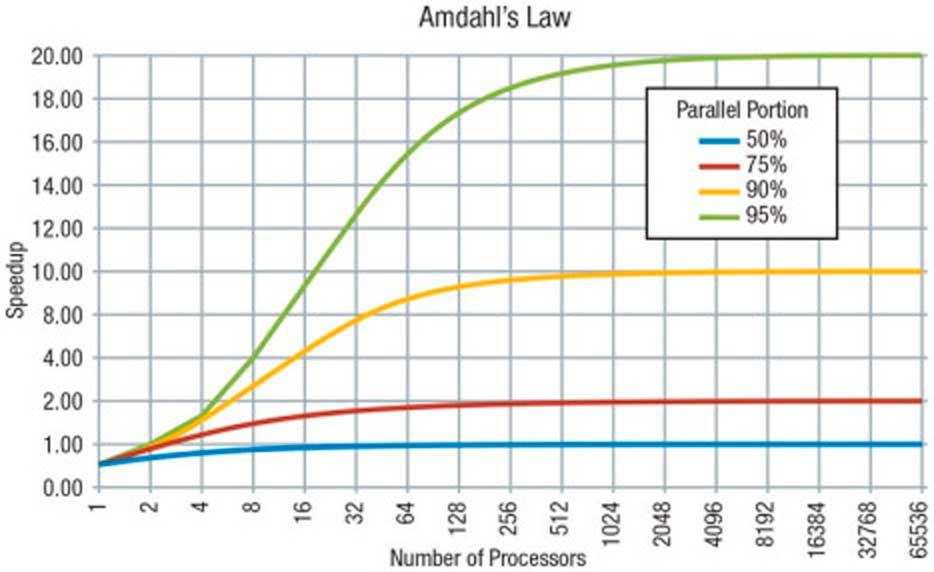

Legea lui Amdahl

Pentru a înțelege un program trebuie să înțelegem că un program are două părți diferite:

- Acela care poate fi executat doar în serie și, prin urmare, poate fi rezolvat doar de un singur nucleu prin executarea unui nucleu de execuție solo.

- Acea parte a codului care poate fi executată în paralel, ceea ce înseamnă că poate fi rezolvată de mai multe nuclee în același timp și cu cât sunt mai multe în procesor, cu atât mai repede se va rezolva această parte.

Dacă luăm în considerare ceea ce s-a explicat în secțiunea anterioară atunci veți concluziona că unele dintre instrucțiunile procesorului care devin microcod ceea ce fac este să devină o succesiune de instrucțiuni care pot funcționa în serie sau în paralel între mai multe nuclee, deși de obicei este că majoritatea instrucțiunilor sunt executate într-un singur nucleu și că codul este executat în paralel prin elemente partajate.

Prin urmare, faptul că o parte a codului este executată de mai multe nuclee depinde exclusiv de dezvoltatorul programului, care trebuie să îl programeze în mod explicit, astfel încât anumite părți să funcționeze în paralel.

VISC și nuclee virtuale

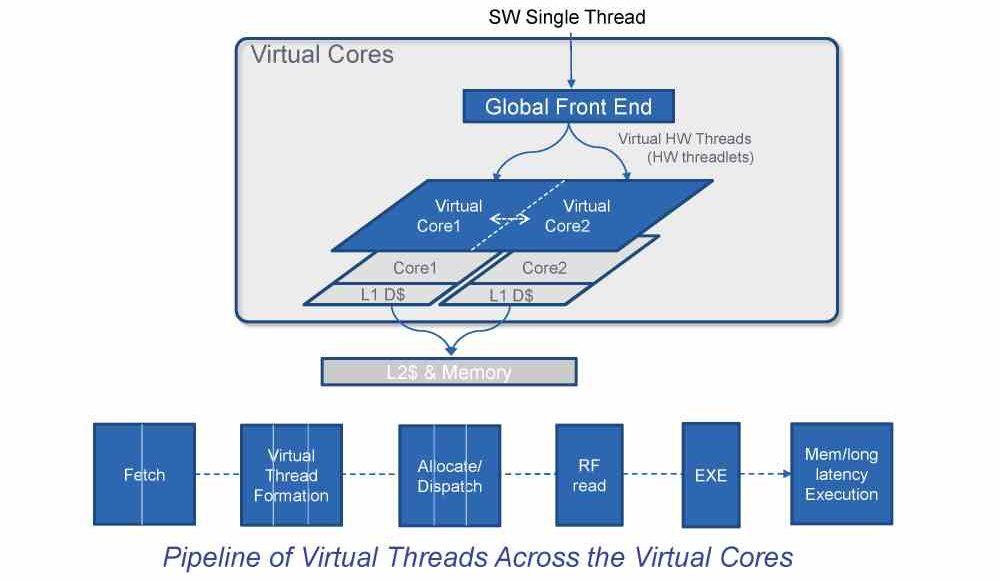

Odată ce am explicat toate cele de mai sus, atunci putem explica ce înseamnă acronimul VISC, a cărui definiție este răspunsul direct la următoarea întrebare: La generarea microinstrucțiunilor în etapa de decodare, nu pot funcționa? în paralel cu mai multe nuclee în loc să o faci într-un singur idem?

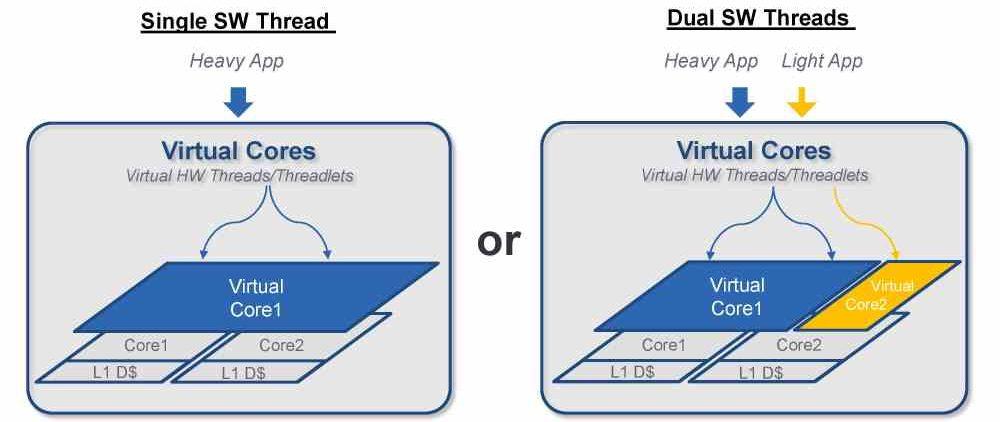

Ei bine, răspunsul la întrebarea despre arhitectura VISC, care a fost ridicat pentru prima dată de o companie numită Soft Machines în 2015 ca un concept de îmbunătățire a performanței procesorului. Acest mic startup a fost cumpărat de Intel în 2016 și de atunci au lucrat la dezvoltarea unei arhitecturi VISC. Cum functioneazã? Ei bine, se poate defini foarte ușor: un singur thread de execuție este trimis către Global Front End al procesorului, care este convertit în mai multe care îndeplinesc aceeași funcție și care funcționează în paralel și rulează în nuclee virtuale. Procesul de conversie se execută la nivel de software printr-un strat de translație, dar trebuie să avem în vedere că acesta poate fi ceva la fel de simplu ca un microcontroler care realizează transferul instrucțiunilor.

Spre deosebire de ceea ce se întâmplă în distribuția sarcinilor într-un procesor multicore convențional, într-o arhitectură VISC nu se intenționează ca un nucleu să fie liber să execute o instrucțiune, ci ca elementele care să o execute să fie disponibile în cadrul procesorului pentru a o executa. De exemplu, se poate întâmpla ca într-un nucleu convențional să nu fie utilizată unitatea vectorială, dar în această paradigmă poate fi folosită pentru a forma una dintre instrucțiuni.

VISC și performanță

Atunci când adoptăm o nouă paradigmă în ceea ce privește arhitectura, primul lucru de luat în considerare este modul în care aceasta afectează performanța, deoarece nu merită să schimbați paradigma actuală dacă nu are ca rezultat o creștere a performanței generale a procesorului. Cea mai clasică modalitate de a crește performanța unui procesor este creșterea numărului de instrucțiuni care se rezolvă pe ciclu de ceas, asta înseamnă a face hardware-ul din ce în ce mai complex, datorită faptului că la adăugarea nucleelor trebuie să numărăm toată infrastructura care le înconjoară care devine la fel sau mai complexă.

Ceea ce diferențiază VISC de restul este nimeni altul decât distribuirea resurselor procesorului pentru execuția diferitelor instrucțiuni se realizează în câteva cicluri de clock, între 1 și 4 nuclee. În acest fel, dacă există două instrucțiuni care concurează pentru alte resurse într-un nucleu, atunci ele pot fi realocate foarte rapid unei alte părți a procesorului unde aceleași resurse sunt disponibile.

Paradigma actuală, care este execuția în neregulă, ceea ce face este să reordoneze execuția instrucțiunilor în funcție de resursele libere în orice moment și apoi să reordoneze ieșirea datelor deja procesate. Limitarea? Alocarea resurselor se realizează la nivel unic, mai degrabă decât multi-core, iar aceasta este cheia unei performanțe mai mari pentru arhitecturile VISC.

Există aceste procesoare astăzi?

Deși conceptul este foarte bun pe hârtie, nimeni nu a prezentat încă un procesor care să funcționeze sub această paradigmă, dar având în vedere că ne apropiem treptat de limitele paradigmei actuale, este important de reținut că există soluții care pot servi pentru a îmbunătăți performanța procesorului computerelor noastre pentru viitor.

A avea un procesor mai puternic nu înseamnă doar a avea unul mai rapid sau cu mai multe nuclee, ci se bazează pe a ști să profiti de resursele disponibile. Execuția neliniștită a fost primul pas în acest sens, însă de atunci, în afara trecerii la multicore, schimbările au fost în general minore. VISC este încă un concept, însă nu este unul imposibil și este o modalitate de a profita de resursele disponibile în procesor într-un mod mult mai eficient.

Până acum știm că conceptul este posibil într-un CPU, deoarece Soft Machines a proiectat și construit unul cu această paradigmă, așa că, deși a fost la nivel experimental, știm că este posibil să se realizeze un astfel de design. Un alt lucru diferit este dificultatea de a aduce întregul set de instrucțiuni și registre x86 la această paradigmă, care este extrem de complexă prin natura sa.