O bună parte a puterii în computerele noastre se bazează pe împărțirea muncii, unde mai multe elemente împărtășesc execuția unei părți din cod pentru a lucra cu acesta. Dar uneori există conflicte în ceea ce privește accesul la date și instrucțiuni care devin o problemă de performanță. O modalitate de a remedia problema este memoria tranzacțională.

Una dintre cele mai mari probleme cu multicore Procesor sistemele pe care le folosesc computerele noastre sunt că se bazează pe modelul Von Neumann, adică există o singură memorie partajată bine. Pe măsură ce crește numărul de unități de execuție, nuclee, fire și alte elemente care funcționează în paralel într-un procesor. Din ce în ce mai multe conflicte sunt create între ele. Nu numai în accesarea datelor, ci și în informațiile conținute în diferitele adrese de memorie și, prin urmare, valoarea variabilelor utilizate de programe. Există multe metode pentru a evita aceste conflicte, una dintre ele este memoria tranzacțională, pe care o vom descrie în acest articol.

O introducere a problemei

Când scrieți un program, acesta este codat într-o serie de instrucțiuni care aparent sunt executate secvențial. Dar deja cu paralelismul instrucțiunilor cu un singur nucleu în mijlocul execuției, pot intra diferite unități de execuție. La aceasta trebuie să luăm în considerare faptul că execuția din funcție adaugă complexitatea faptului că accesul la memorie și date în timpul rulării se face într-un mod dezordonat.

Atunci când există un număr mare de solicitări, se ajunge la crearea unei contestații pentru a accesa aceeași memorie. Acest lucru face ca solicitările să fie întârziate din ce în ce mai mult, crescând latența memoriei cu CPU în anumite instrucțiuni și afectând lățimea de bandă. Pentru aceasta, există mecanisme care evită pe cât posibil aceste conflicte în accesul la memorie, în așa fel încât procesele să acceseze memoria din memoria ordonată. Acest lucru evită conflictele la modificarea datelor în ierarhia sa, precum și la reducerea problemelor de dispută și, în consecință, a latenței de acces.

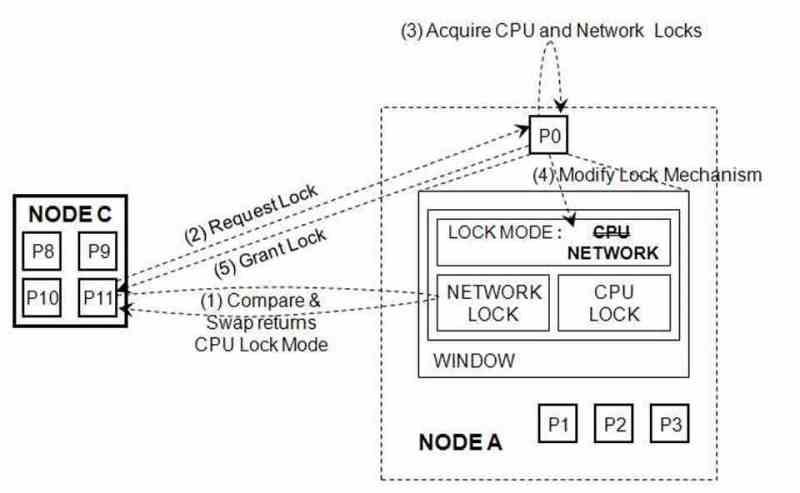

Cel mai simplu mod de a realiza acest lucru este prin blocări, care sunt secțiuni ale codului în care marcăm că nu trebuie executate simultan de diferite fire de procesare. Adică, doar un singur nucleu al acestuia poate fi responsabil pentru această parte a codului. Deci, am făcut o blocare la restul nucleelor, iar restul vor putea intra în execuție numai atunci când se ajunge la instrucțiunea care termină blocarea. Ceea ce se va întâmpla atunci când partea de cod izolată la toate nucleele, cu excepția unuia, a fost finalizată.

Ce este memoria tranzacțională?

O metodă de evitare a problemelor descrise în secțiunea anterioară este utilizarea memoriei tranzacționale. Ceea ce nu este un tip de memorie sau stocare, deci nu vorbim despre o piesă pură de hardware. Originea sa se află în tranzacțiile bazelor de date, este un tip de instrucțiuni executate în unitățile Load-Store.

Sistemul de tranzacții dintr-un procesor funcționează după cum urmează:

- Este creată o copie a părții de memorie pe care mai multe nuclee doresc să o acceseze, una pentru fiecare instanță.

- Fiecare instanță își modifică copia privată independent de restul copiilor private.

- Dacă o dată a fost modificată într-o copie privată și nu în rest, atunci modificarea este copiată și în restul copiilor private.

- Dacă două instanțe modifică aceleași date în același timp și creează o inconsecvență în date, atunci ambele copii private sunt șterse. iar copiile private ale restului sunt copiate

Al patrulea punct este important, deoarece este în acea parte în care devine clar că este necesar ca acea parte a codului să fie serializată. Aceasta înseamnă că restul instanțelor nu mai modifică copiile lor private, iar modificările sunt făcute doar de una dintre instanțe. Când se termină, modificările sunt apoi copiate în restul copiilor private. Când partea de cod marcată ca tranzacțională a fost deja executată și toate copiile private conțin aceleași informații, atunci rezultatul este copiat în liniile cache corespunzătoare și în adresele de memorie.

Sisteme de memorie tranzacțională, Intel TSX

Acronimul TSX, Extensii de sincronizare tranzacțională, se referă la o serie de instrucțiuni suplimentare pentru x86 ISA, care sunt destinate să adauge suport de memorie tranzacțională Intel CPU-uri. Prin urmare, este o serie de instrucțiuni și mecanisme asociate cu acestea care permit delimitarea unor secțiuni specifice ale codului ca tranzacționale și pentru ca procesorul Intel să efectueze procesul pe care l-am discutat în procesul anterior. Dar, în acest caz, implementarea Intel este puțin mai complexă. Întrucât, așa cum am văzut anterior, dacă există un conflict între două date, întregul proces este întrerupt de una dintre instanțele care rulează.

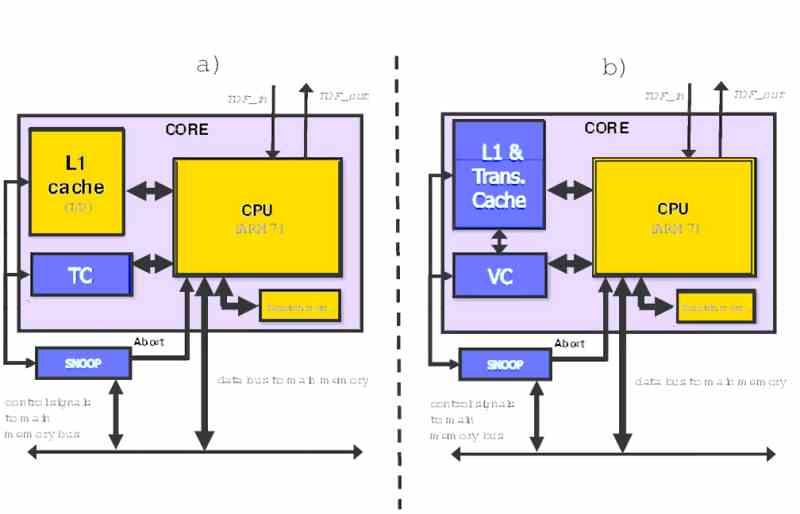

Implementarea sa în hardware se realizează prin adăugarea unui nou tip de cache numit cache tranzacțional în care sunt efectuate diferite operațiuni pe diferite date. Rețineți că ceea ce caută memoria tranzacțională este de a reduce conflictele atunci când accesați memoria. Deși cache-urile acceptă o cantitate mai mare de cereri decât RAM în general, acestea sunt, de asemenea, limitate și mai ales la nivelurile cele mai îndepărtate de nuclee. Toate acestea sunt combinate cu utilizarea de memorii interne și registre private care servesc drept suport pentru copiile private executate de diferitele nuclee.

Instrucțiunile Intel TSX nu sunt un set complex, avem pe de o parte instrucțiunea XBEGIN care ne marchează când începe o secțiune tranzacțională de memorie, instrucțiunea XEND care marchează sfârșitul și XABORT, care servește pentru a marca o ieșire din proces când apare o situație excepțională.

Sfârșitul instrucțiunilor Intel TSX?

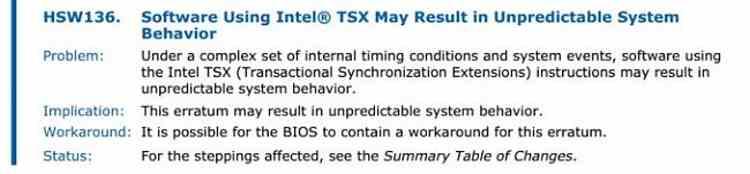

Unitățile de control ale procesorului de astăzi sunt de fapt microcontrolere complete, ceea ce înseamnă că modul în care decodează instrucțiunile și lista instrucțiunilor pot fi actualizate. Intel a realizat prima implementare pe arhitectura Haswell și a rămas până acum în procesoarele Intel. De vreme ce a fost recent dezactivat prin firmware pe nucleele de generația a șasea, a șaptea și a opta a Intel.

Din când în când, Intel efectuează actualizări de la distanță ale procesoarelor sale, care sunt efectuate prin intermediul motorului de gestionare Intel pe care îl avem în computerul nostru, fără să știm. Nu sunt de obicei obișnuite, dar pot include optimizări pentru executarea anumitor instrucțiuni sau chiar eliminarea suportului pentru alții. Eliminarea Intel TSX din Intel Core se datorează faptului că, cu cele mai recente modificări ale microcodului intern al unității de control, aceasta implică un conflict în funcționarea software-ului, ceea ce înseamnă că CPU nu funcționează așa cum ar trebui.

Dar adevăratul motiv este că Intel TSX permite executarea codului rău intenționat sub radarul sistemelor clasice de securitate, în special a celor care afectează sistemul de operare. Deoarece copiile private nu corespund mediului utilizatorului sau sistemului de operare. Deci, este încă o problemă similară cu cea a execuției speculative.