Cu siguranță, ați auzit (sau ați citit) vorbiri despre Cod de corecție a erorilor ECC în multe componente hardware, toate legate de memorie (fie RAM sau depozitare), deși foarte puțini înțeleg importanța acestuia. Din acest motiv, în acest articol vom explica cum funcționează ECC într-un SSD controlor și cum, datorită acesteia, este posibil să crești longevitatea și să faci o diferență mare în durata de viață utilă a SSD-urilor .

Fiecare dispozitiv care utilizează memorie NAND Flash necesită un cod aleator de corecție a erorilor de biți (cunoscut sub numele de eroare „soft”). Acest lucru se datorează faptului că o mulțime de zgomot electric este produs în interiorul unui cip NAND, iar nivelurile de semnal ale biților care trec printr-un lanț de cipuri NAND sunt foarte slabe.

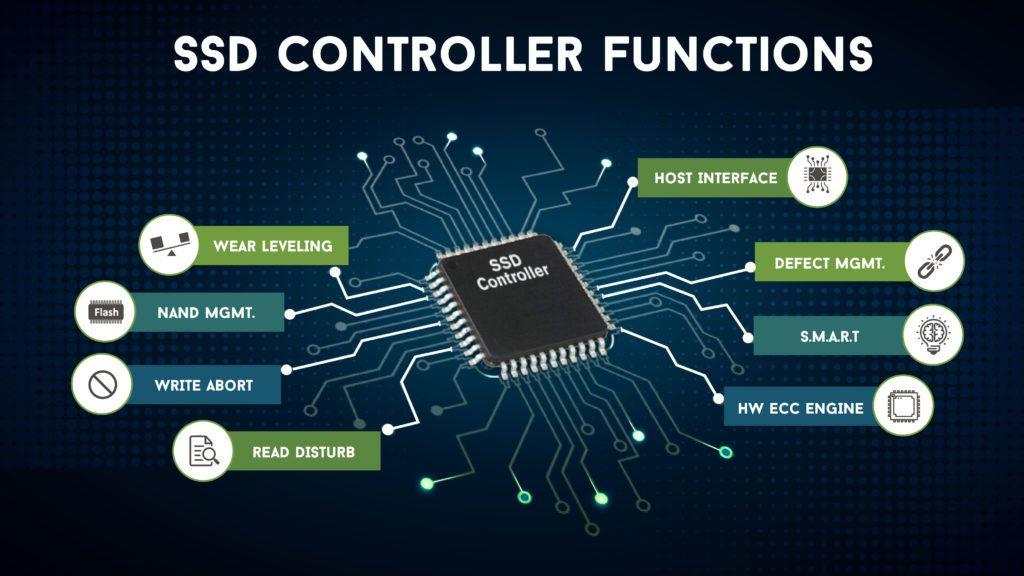

Unul dintre modurile în care Memorie NAND a devenit cele mai ieftine toate se datorează faptului că necesită corectarea erorilor dintr-un element din afara cipului NAND în sine; În cazul SSD-urilor, ECC este efectuat pe controler .

Cum funcționează ECC pe un controler SSD

Aceeași corecție a erorilor ajută, de asemenea, la corectarea erorilor de biți datorate purtați pe memorie celulele în sine . Atitudinea poate determina „blocarea” biților într-o stare sau alta (cunoscută drept eroare „tare” sau eroare grea) și poate crește frecvența erorilor „moi”.

Deși nu este un concept prea larg, rezistența la memoria flash este o măsură a câtor cicluri de ștergere / scriere poate rezista un bloc flash înainte de apariția erorilor „dure”. Foarte des aceste eșecuri sunt doar în biți individuali și este foarte rar ca întregul bloc să eșueze. Cu un număr suficient de mare de ștergere / scriere, rata de eroare „soft” crește, de asemenea, din cauza unui număr de alte mecanisme din SSD în sine.

If ECC poate fi utilizat pentru a corecta aceste erori „dure” și erorile „moi” nu cresc, atunci durata întregului bloc se prelungește mult, cu mult peste rezistența specificată de producător.

Să luăm un exemplu: să spunem că un cip NAND neutilizat are suficiente erori „moi” pentru a necesita 8 biți de ECC, adică fiecare pagină citită poate avea până la 8 biți care au fost corupți la întâmplare (în general din cauza zgomotului electric noi vorbeau despre). la început). ECC utilizat în acest cip poate corecta erori pe 12 biți, astfel încât ECC nu a putut rezolva această problemă ar trebui să găsim 8 erori „moi” legate de zgomotul electric, plus alte 5 „moi” din cauza uzurii.

Acum, producătorii de memorie flash garantează că prima dintre cele 5 eșecuri va apărea cândva după specificația de rezistență a SSD. Aceasta înseamnă că niciun pic nu va eșua din cauza uzurii până la depășirea ciclurilor de ștergere / scriere specificate de producător. Acum rețineți că specificațiile nu sunt suficient de precise pentru a prezice atunci când următorul bit va eșua și că poate dura câteva mii de cicluri de ștergere / scriere deasupra specificației pentru ca acest lucru să se întâmple; amintiți-vă că producătorul garantează că nu se va întâmpla înainte de ciclurile X, dar nu când se va întâmpla odată ce acestea sunt depășite.

Aceasta înseamnă că poate dura mult timp înainte un bloc devine atât de corupt că trebuie să fie eliminat din service (și, de asemenea, pentru aceasta, SSD, de obicei, are blocuri „suplimentare” pentru a le înlocui pe cele corupte), ceea ce înseamnă, la rândul său, că rezistența Eroare corectată bloca ar putea fi de multe ori mai mare decât rezistența specificată, în funcție de numărul de erori în exces pe care ECC este proiectat să le corecteze.

Ce impact are codul de corecție a erorilor asupra unui SSD?

Așa cum am explicat mai înainte, memoria flash este atât de ieftină, deoarece nu include ECC-ul în cipuri în sine, ci este integrat în alt hardware extern pentru acestea și, după cum vei presupune că acesta are un preț. Un ECC mai sofisticat necesită mai multă putere de procesare pe controler și poate fi mai lent dacă algoritmii nu sunt foarte moderni. De asemenea, numărul de erori care pot fi corectate va depinde de cât de mare este corectat sectorul de memorie, astfel încât un controler SSD cu un algoritm ECC sofisticat să folosească o mulțime de resurse, reducerea SSD general performanță . Aceste îmbunătățiri fac și ele controlorul mai scump .

Algoritmii ECC au propria lor stare matematică în funcție de controler (cu alte cuvinte, nu există un standard) și chiar și cele mai de bază codificări ECC (Reed-Solomon și LDPC) sunt destul de complicate de înțeles. Când cineva vorbește despre limita Shannon (numărul maxim de biți care poate fi corectat), este o cantitate care, așa cum nu știi de la producător în specificațiile tehnice, este extrem de dificil de calculat.

Doar rămâneți cu el: mai mulți biți de corecție duc la o durată de viață mai lungă pentru SSD, dar are un impact asupra performanței sau chiar a prețului produsului, având nevoie de un controler mai puternic.