Conceptul de Cache DRAM constă în adăugarea unui nivel suplimentar de cache între procesor și RAM memorie pentru a spori performanța primului. Dar, ce schimbări înseamnă în arhitectura unui procesor și cum funcționează acest concept? Vă explicăm și, de altfel, ce procesoare vor folosi această arhitectură.

Acum câteva zile un Apple a apărut un brevet în care a fost menționată utilizarea Cache DRAM într-unul din procesorii săi viitori, un concept care, deși poate părea exotic, nu este, așa că îl vom demitifica.

Memoria DRAM ca cache, o contradicție

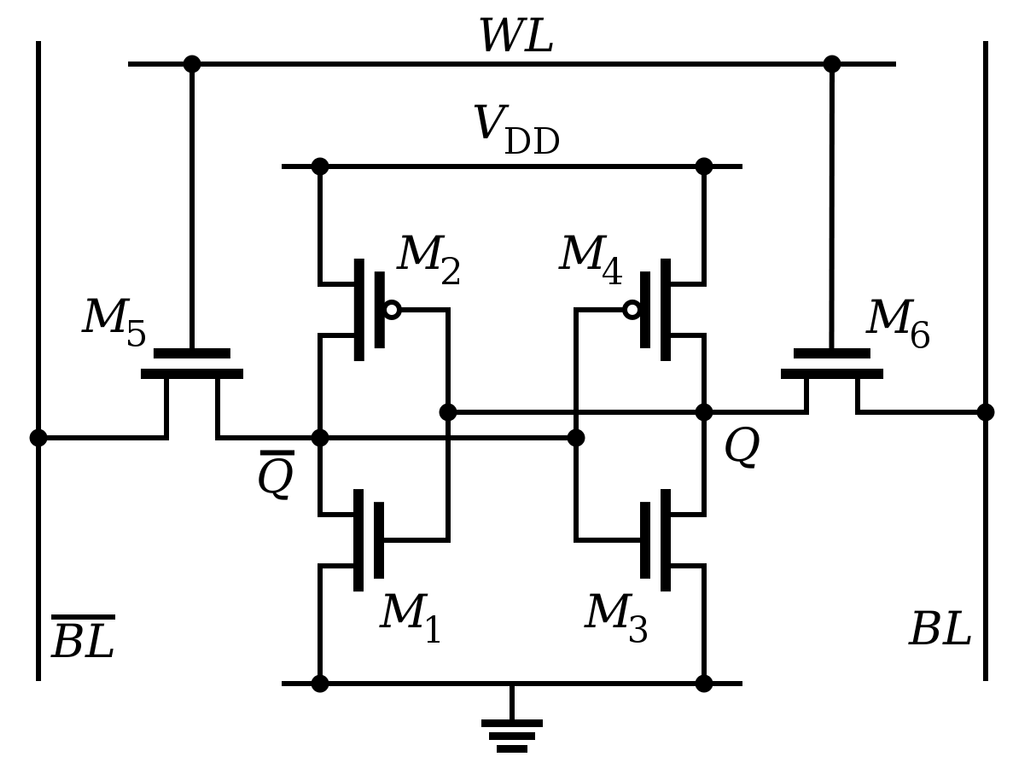

Toate amintirile RAM actuale care sunt utilizate în afara unui procesor sunt de tip DRAM sau Dynamic RAM, în timp ce amintirile care sunt utilizate în interiorul procesoarelor sunt Static RAM sau SRAM. Ambele funcționează cam la fel în ceea ce privește modul de accesare a datelor, dar ceea ce nu sunt la fel este în modul în care stochează un pic de memorie.

Memoria DRAM este mult mai ieftină, dar, prin natura sa, necesită o reîmprospătare constantă, iar viteza de acces este mai mică decât SRAM, deci nu este utilizată în general în cadrul procesoarelor. Pe de altă parte, scalează într-un mod mai rău decât DRAM, așa că, în ciuda faptului că IBM a folosit memoria DRAM ca memorie cache de ultim nivel în procesoarele sale pentru calcul de înaltă performanță, POWER, în următoarea sa generație vor folosi SRAM memorie.

Deci, conceptul de cache, care este legat de o memorie de tip SRAM, împreună cu conceptul DRAM, în principiu, nu se potrivesc și, deși avem cazul CPU-urilor IBM, nu vom vorbi despre utilizarea memoriei DRAM ca cache în procesorul.

Memoria cache DRAM și memoria HBM ca exemplu

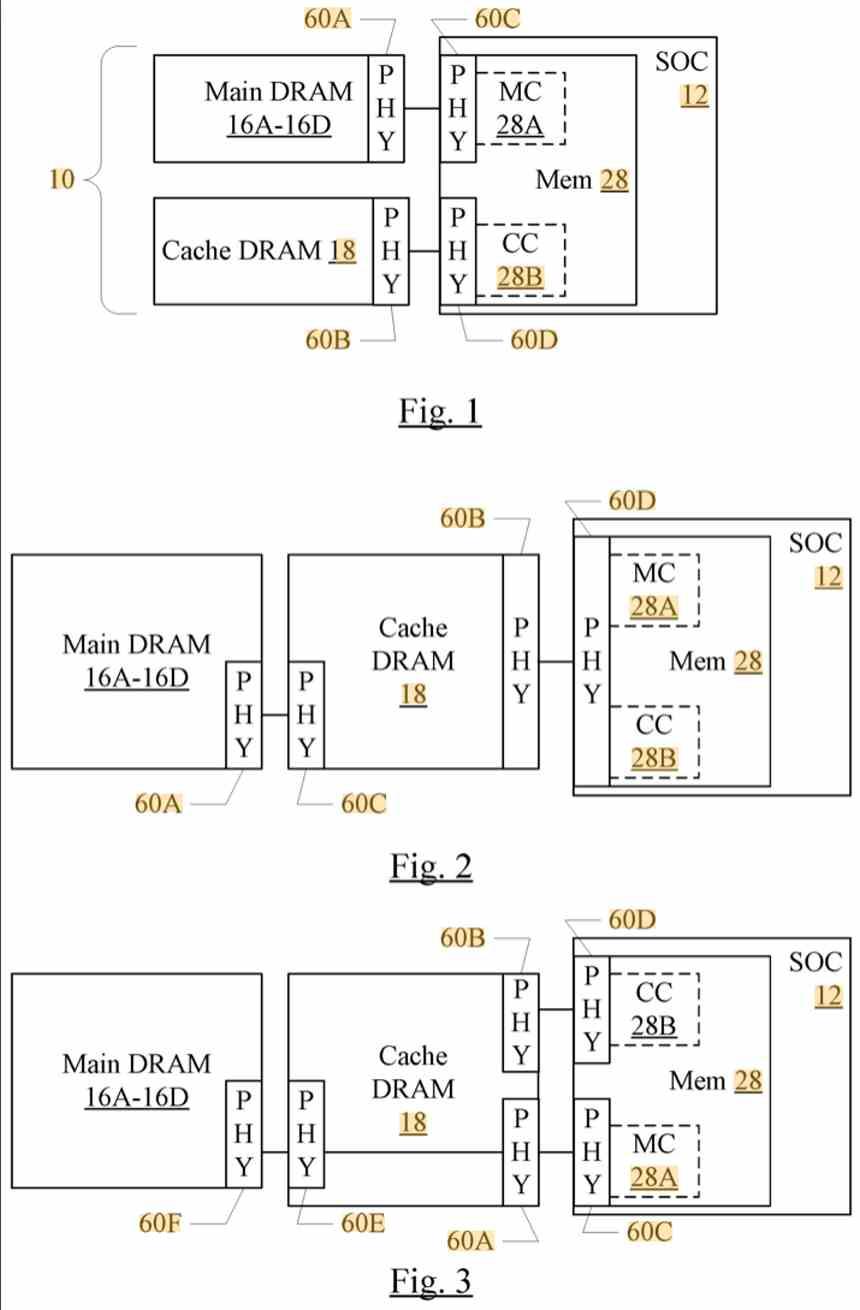

Cache DRAM este conceptul de adăugare a unui strat suplimentar în ierarhia memoriei între memoria cache de ultim nivel a procesorului și memoria principală a sistemului, dar construită printr-o memorie DRAM cu o viteză de acces mai mare și o latență mai mică decât DRAM-ul folosit ca memorie principală.

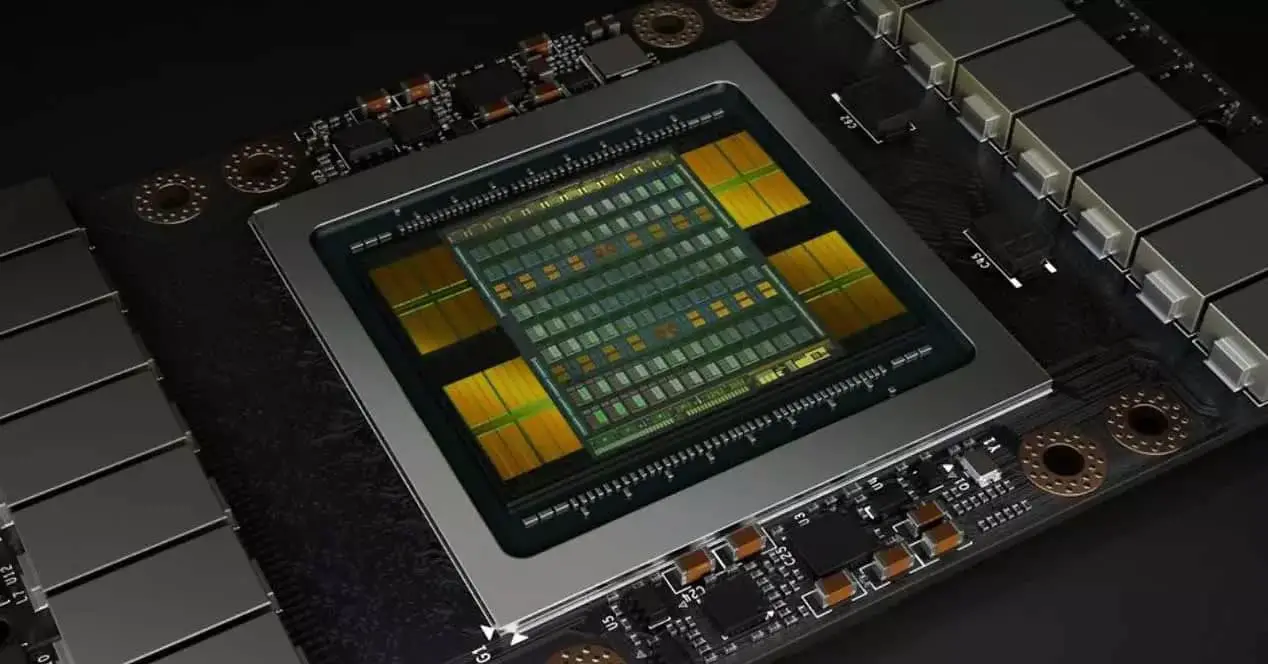

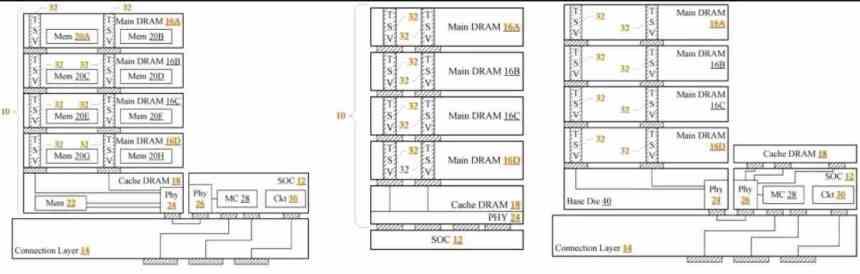

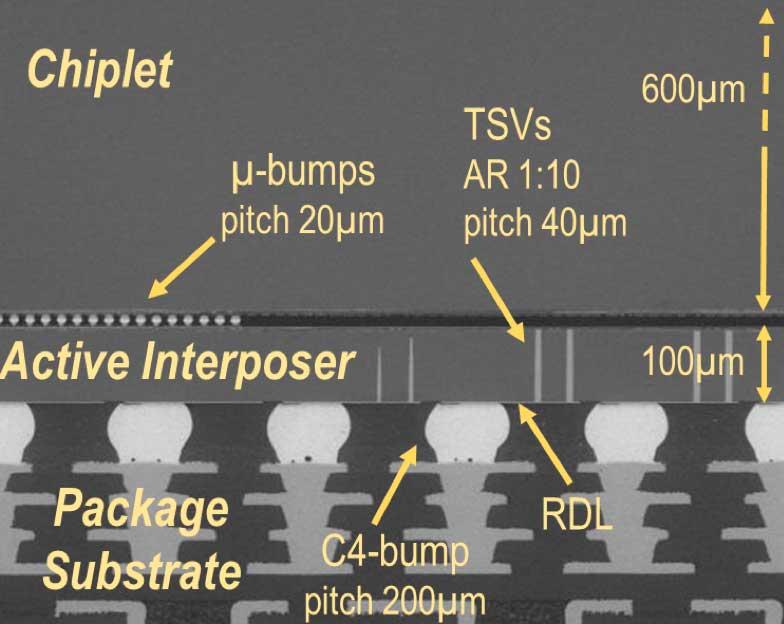

O modalitate de a realiza acest lucru este prin utilizarea memoriei de tip HBM ca o memorie cache DRAM, care este un tip de memorie DRAM în care diferite cipuri de memorie sunt stivuite și conectate vertical folosind un tip de cablare numit TSV sau căi intermediare. siliciu prin faptul că trec prin jetoane. Acest tip de conexiune este utilizat și pentru construirea memoriei 3D-NAND.

Deoarece conexiunea este verticală, este necesar un interpozator, care este o piesă electronică sub forma unei plăci care este responsabilă pentru comunicarea procesorului și a memoriei HBM. Atât procesorul, fie Procesor or GPU, sunt montate pe interpozitorul menționat, care datorită distanței scurte conferă memoriei HBM capacitatea de a funcționa ca un tip de memorie DRAM cu latență mai mică decât memoria clasică DDR și GDDR.

Ar trebui clarificat faptul că dacă DRAM-ul ar fi mai aproape de procesor, întrucât o configurație 3DIC îl plasează chiar deasupra acestuia, atunci nivelul de latență comparativ cu memoria HBM ar fi mai mic și, prin urmare, viteza de acces mai mare, datorită faptului că electronii au pentru a parcurge o distanță mai mică.

Am folosit cu adevărat memoria HBM pentru a vă face o idee, dar orice tip de memorie într-o configurație 2.5DIC funcționează ca exemplu.

Dar un interpozitor standard nu este suficient

Următoarea problemă este că o memorie cache nu funcționează în același mod ca o memorie RAM, deoarece ceea ce face sistemul de căutare a datelor al procesorului nu este copierea liniilor de instrucțiuni din RAM una câte una, ci mai degrabă sistemul de memorie. Ce face cache-ul este să copieze fragmentul de memorie unde se află linia curentă de cod în ultimul nivel al cache-ului.

Ultimul nivel stochează memoria cache a unui procesor este partajat de toate nucleele, dar pe măsură ce ne apropiem de primul nivel, acestea sunt mai private. Trebuie clarificat faptul că, în ordine descrescătoare, fiecare nivel de cache conține un fragment din cache-ul anterior. Când un procesor caută date, ceea ce face este să le caute în ordine crescătoare a nivelurilor cache, unde fiecare nivel are mai multă capacitate decât precedentul.

Dar, pentru ca memoria HBM să se comporte ca o memorie cache, atunci avem nevoie ca elementul care comunică procesorul cu memoria menționată, interpozatorul, să aibă circuitele necesare pentru a se comporta ca o memorie cache. Deci, un interpozitor convențional nu poate fi utilizat și este necesar să adăugați circuite suplimentare în interpozitor care să permită memoria HBM să se comporte ca o memorie cache suplimentară.