Sempre falamos sobre novos processos e melhorias litográficas, aqueles que levam o hardware ao próximo nível. Mas geralmente não falamos sobre os problemas que as empresas gostam TSMC or Intel tem que enfrentar para seguir em frente e inovar. Agora que os taiwaneses atingiram a produção em massa de 5 nm e estão prestes a começar com 3 nm, é um bom momento para entender os principais obstáculos que enfrentaram.

Um determinado chip precisa enfrentar vários problemas quando é introduzido em um produto de alto desempenho. Do calor às vibrações variadas, pelas frequências atingidas, tudo se torna cada vez mais complexo para funcionar exatamente porque reduzir os transistores e aumentar a densidade dos nós exige inspeção, medição e teste de cada chip de uma maneira mais complexa, ou seja, cada salto litográfico acrescenta certos problemas.

O 5nm como sucessor do 7nm representa apenas algumas mudanças importantes

A principal delas é que a própria aleta do transistor deve ser fisicamente mais forte. Reduzir o tamanho de cada extremidade e porta requer uma série de camadas verticais maiores se os transistores FinFET típicos forem mantidos .

Aletas e portões se alongam, ficam mais altos, portanto a quantidade de materiais e seu depósito é crucial para manter o fluxo atual uniforme nas três paredes da referida porta. Poderíamos pensar que, aumentando a altura, é possível passar um fluxo de corrente vertical maior em cada transistor, mas a verdade é que a proporção de largura e altura é a chave para aumentar seu desempenho, pois as proporções não são equivalentes ao desempenho.

Isso gera um problema de controle nas fábricas para garantir que o processo de gravação do transistor esteja correto. Para tentar evitar isso, a inteligência artificial está sendo usada através do aprendizado de máquina para detectar certos problemas antes que a bolacha termine certos processos vitais, para que se saiba com antecedência se é uma bolacha predisposta a falhas.

O segundo problema que os 5nm enfrentam é curioso, pois é o excesso de dados do próprio wafer e chip. Aqui, novamente, o Deep Learning assume a liderança, pois é capaz de determinar por meio de imagens de visão de máquina e com certos algoritmos os problemas e pontos de interesse em que os engenheiros devem se concentrar para melhorar o processo de fabricação do nó.

Esse fato reduziu os tempos de entrega efetivos desse processo litográfico de 5 nm, pois graças ao aprendizado profundo, o TSMC pôde ver e antecipar onde estavam os problemas mais sérios, sem ter que perder grandes quantidades de horas com base em evidências e gravações de bolachas erros.

O 3nm pode ser a mudança de paradigma para a nova geração de nós

Se os 5 nm forçaram os transistores a serem alongados verticalmente para agrupá-los horizontalmente em maiores números e, assim, aumentar a densidade do nó, os 3 nm representarão mudanças mais importantes.

Embora não seja confirmado pela TSMC, NVIDIA e AMD pode ter que redesenhar suas arquiteturas para gravuras, como os taiwaneses são mais do que propensos a ir para o Samsung caminho e substitua os transistores FinFET por GAA ou Gate-all-around.

A intenção preventiva não é essa, pois isso implicaria uma mudança drástica, começando com as máscaras em branco e terminando com um novo tipo de gravura e lentes. Além disso, pouco se sabe é que, mesmo que o TSMC tenha conseguido manter os FinFETs por mais uma geração, os novos transistores exigirão novos materiais nas bolachas, como cobalto ou rutênio.

Como se isso não bastasse, os filmes e as camadas devem ser mais finos para favorecer a transferência elétrica de corrente, mas isso implica que serão mais difíceis de limpar, polir, medir e, é claro, inspecionar. Como se isso não bastasse e dado outro paradigma curioso, uma lógica digital de um chip menor em seus transistores, eles adquirem um comportamento mais análogo.

Novos materiais e funcionalidades de cada transistor

Se adicionarmos isso aos novos materiais que definirão as barbatanas e os portões, encontraremos alguns dos problemas do passado, mas multiplicados em termos de dificuldade em resolvê-los. Vazamentos de energia, fraquezas estruturais, tensões não medidas e, claro, maior indutância serão alguns dos problemas enfrentados por todas as empresas do setor, não apenas a TSMC como fabricante de wafer.

Os dados principais estarão na funcionalidade de cada transistor. Anteriormente, quando um transistor morreu, ele parou de funcionar, mesmo caso se estivesse danificado. Atualmente, isso não ocorre devido à fabricação e ao design do mesmo: ele continuará funcionando, mas com um desempenho mais baixo que, se expandido, reduz o conjunto deles para um nível mais baixo.

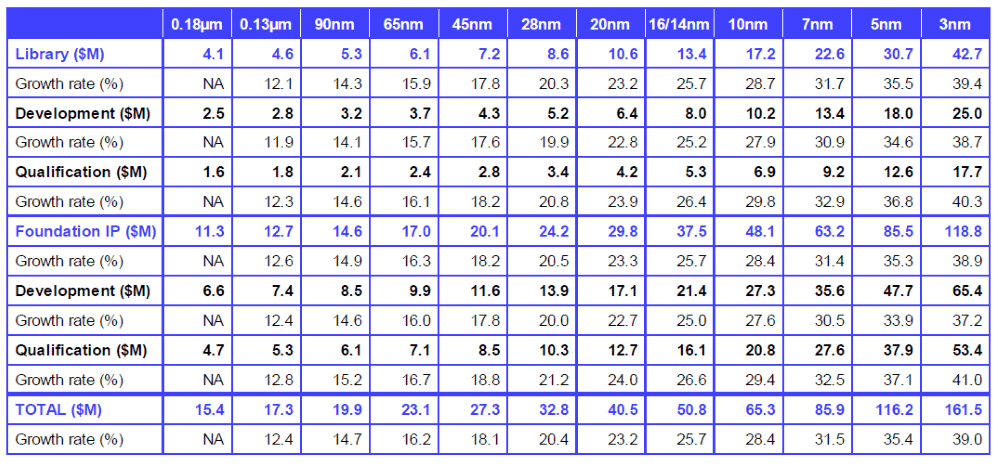

Portanto, a perfeita funcionalidade dos transistores é fundamental na indústria e envolve bilhões de dólares em pesquisa, prevenção e detecção de erros, algo que nos 3 nm será essencial se você quiser aumentar o desempenho de cada chip. É engraçado como a indústria está mudando. A dificuldade de um nó não é tanto obter bolachas funcionais, mas garantir que essas bolachas obtenham a taxa de desempenho e confiabilidade que se destinam e para as quais foram projetadas, existe atualmente o desafio, porque uma bolacha com alta densidade de chip se o desempenho final destes estiver abaixo do seu antecessor.

O próximo desafio será o átomo e, a partir daí, um campo incrível se abre, onde o silício pode ser apenas a base de uma série de compostos moleculares que permitem reduzir seu tamanho abaixo do átomo, algo verdadeiramente incrível.