A tecnologia PCI Express é usada há muito tempo para conectar placas gráficas e outros periféricos, como SSDs NVMe. A implementação da quinta geração da interface ocorre com a chegada dos processadores Alder Lake de Intel e os processadores Zen 4 de AMD. Mas a especificação PCI Express 6.0 foi finalizada e traz várias melhorias em relação à quinta geração.

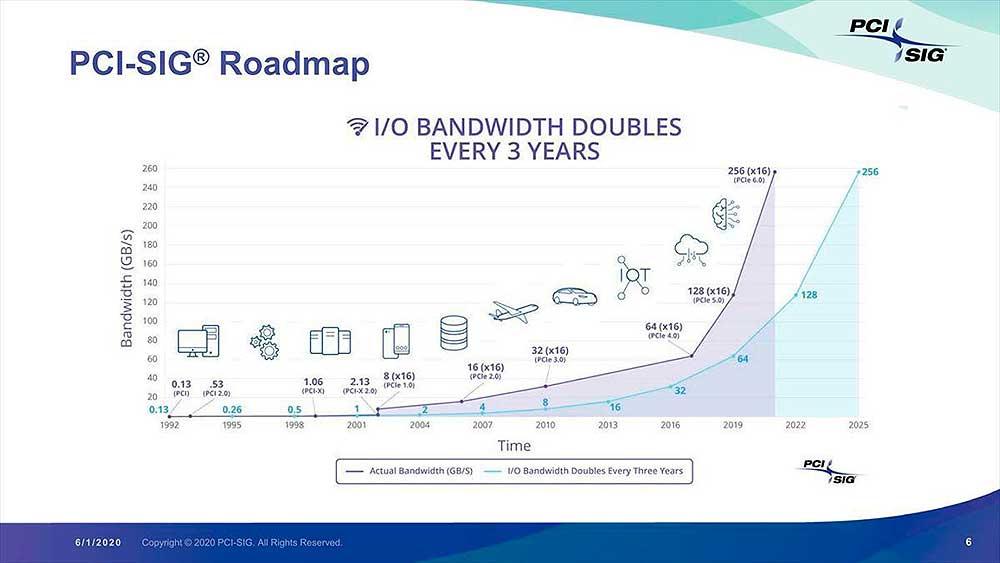

O PCI Express 6.0 segue desde o início as mesmas melhorias das gerações anteriores desta interface, ou seja, baseia-se na duplicação da largura de banda em relação à geração anterior. Porém, no caso do PCI Express 6.0, mudanças profundas foram necessárias no desenvolvimento da sexta geração desta interface.

A largura de banda do PCI Express 6.0 é de 128 GB / s para uma interface de 16 linhas, uma largura de banda exageradamente alta para uma interface de E / S e que é um salto de quatro vezes em comparação com o PCI Express 4.0 atual que estamos usando para os gráficos atuais cartões. O salto também significa um salto do NVMe SSD controladores de flash de 7 a 8 GB / s a 28 a 32 GB / s com PCI Express 6.0.

Compatibilidade com versões anteriores e o problema de instabilidade do sinal

A interface PCI Express sempre foi compatível com as versões anteriores do protocolo, isso significa que podemos conectar uma placa PCI Express 1.0 em um slot PCI Express 6.0 e funcionará porque a pinagem será exatamente a mesma. Portanto, não é possível aumentar o número de pinos para aumentar a largura de banda sem aumentar a velocidade. A solução? Aumente a velocidade do clock em que a interface funciona.

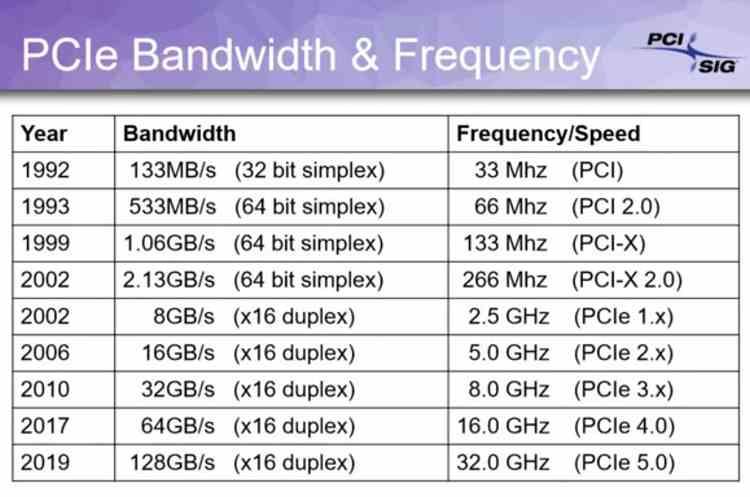

O problema com PCI Express 6.0? À medida que aumentamos a velocidade do clock de uma interface, ela se torna mais instável com a distância e, após seis gerações, eles tiveram que fazer alterações na interface devido à alta velocidade com que a interface funciona de maneira tradicional. E se você olhar a tabela que acompanha essas linhas estamos falando de uma velocidade teórica de 64 GHz, o que deforma bastante o sinal, mesmo na curta distância ambas as pontas estão em uma interface PCI Express.

Isso forçou uma série de medidas a serem adotadas para tornar possível o salto para o PCI Express 6.0.

Primeira das melhorias no PCI Express 6.0, uso de PAM4

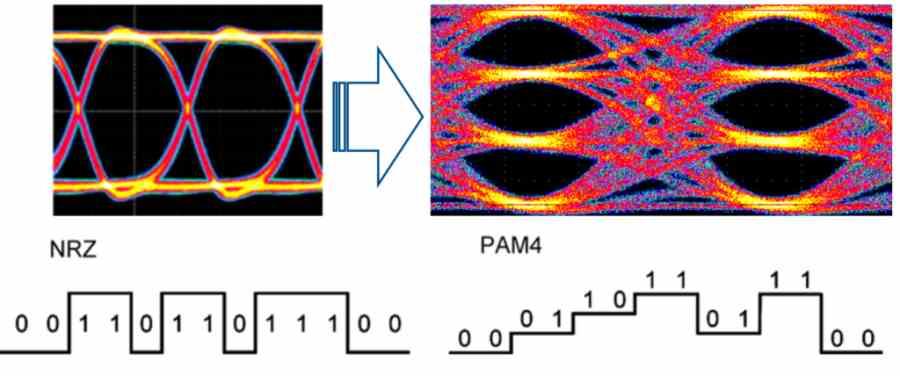

Como uma interface externa ou interna de um chip sabe se o valor é 1 ou 0? Bem, simples, dependendo da voltagem em que a informação é transmitida. Os sistemas binários baseiam-se no uso de duas tensões com distância suficiente entre elas para que a queda ou aumento de tensão não confunda o sinal. Em sistemas analógicos, uma simples variação na tensão supõe uma mudança na informação. Por esta razão, os computadores falam em binário.

O que isso tem a ver com PCI Express 6.0? Como não podemos aumentar a largura de banda porque o sinal está distorcido e nem o número de pinos para compatibilidade com versões anteriores, uma solução tem que ser encontrada e isso passa pelo uso de codificação PAM4 ou Modulação de Amplitude de Pulso, que já vimos no GDDR6X e não se baseia no uso de dois valores de tensão, mas de 4 valores de tensão para cada pino. Desta forma, podemos codificar os valores 00, 01, 10 e 11 em cada pino. Quatro valores no total, em vez dos dois valores clássicos que seriam 0 ou 1.

A solução evita aumentar a largura de banda e os pinos, mas nos diz que no PCI Express 7.0 isso não será mais possível com os métodos convencionais. Podemos ver o uso de fotônica e interfaces ópticas, mas com as melhorias para o PCI Express 6.0 recém-saído do forno, é melhor ter paciência com seu sucessor.

Mudanças no sistema de pacotes

O salto para o PAM-4 mudou a maneira como a interface PCI Express 6.0 envia seus pacotes, apesar de ser compatível com as gerações anteriores por meio da comunicação no modo PAM-2 ou NRZ tradicional. A realidade é que o formato PAM-4 não suporta o sistema de pacotes anterior e, portanto, o protocolo de comunicação mudou por causa disso.

A primeira mudança foi o chamado Forward Error Correction ou FEC, que é o novo protocolo para correção de erros no envio de dados. O problema é que a largura de banda a ser processada é tão alta que o FEC adiciona uma latência enorme ao enviar os dados. Para aliviar isso, o padrão PCI Express 6.0 usa um tipo de pacote chamado FLIT. Um pacote nada mais é do que um conjunto de bits com um destino específico. A latência de envio de cada FLIT? Depende do número de linhas na interface, mas cada pacote tem uma latência de apenas 2 ns em um PCI Express 16 de 6.0 linhas, mas chega a 32 ns em uma interface de linha única.

O FEC só funciona com tamanhos fixos, por isso o FLIT tem um tamanho de 256 bytes por envio. Cada pacote ou TLP pode ter um tamanho que varia de 0 bytes a 4096 bytes e, portanto, cada pacote pode ser composto de vários FLITS.

Terceira atualização para PCI Express 6.0, consumo variável

O PCI Express 6.0 adiciona um novo estado de baixo consumo denominado L0P. Este modo permite que a interface corte seu consumo de energia quando o fluxo de dados enviado for inferior ao que a interface pode transmitir. Para isso, varia a velocidade do clock em que a interface funciona em momentos específicos da transmissão de dados, tudo sem causar uma paralisação que agregue latência à transmissão dos dados.

O problema é que este mecanismo está associado a FLITS e FEC e portanto ao PAM4, o que significa que só é possível usar no modo PCI Express 6.0 e não nos outros modos.