Um dos conceitos mais difundidos na computação hoje é, sem dúvida, o de XMP. Qualquer usuário moderadamente interessado em hardware sabe que quando falamos sobre perfis de overclock de memória, Intel tomou a medida de AMD, que constantemente tenta se adaptar a esses requisitos por meio de sua tecnologia AMP. Com a saída de Alder Lake-S como uma arquitetura revolucionária, a Intel deu um passo além ao apresentar XMP3.0 , mas que notícia esconde?

Alguns se perguntam as razões para as decisões da Intel em relação RAM e especificamente XMP. Embora nunca saberemos, a verdade é que a passagem de DDR4 para DDR5 foi um momento ideal do ponto de vista do overclock para implementar mudanças e melhorias, já que como estamos vendo o 4,800 MHz do JEDEC eles estão sendo deixados para trás apenas alguns dias após o lançamento das CPUs Core 12.

Portanto, e dada a rapidez com que os fabricantes aceleram e atualizam seus módulos com velocidades seriais crescentes, resta apenas perguntar se a Intel levou isso em consideração? O XMP 3.0 está atualizado com o que será exigido dele?

Intel XMP 3.0, um toque necessário

eXtreme Memory Profile ou XMP está conosco desde 2007 e nesta terceira versão olhando para trás e depois de 14 anos é normal que o gigante azul lance uma nova revisão com novidades. Porque? Pelas mudanças que DDR5 supõe com respeito a DDR4. Não entraremos neste tópico porque já o tratamos em extensão, mas se há algo a dizer sobre o XMP 3.0 é que ele é exclusivo do DDR5 como tal.

O termo Perfil do seu nome vem ao dedo para explicar o primeiro dos pontos em que a Intel deu os fabricantes, já que como bem sabemos esta tecnologia se baseia no reconhecimento de uma série de tabelas de configuração que cada fabricante integra a gosto por modelo , chip e versão de memória para fazer com que o IMC reconheça e aplique essas configurações por meio do firmware.

O que há de novo no Intel XMP 3.0

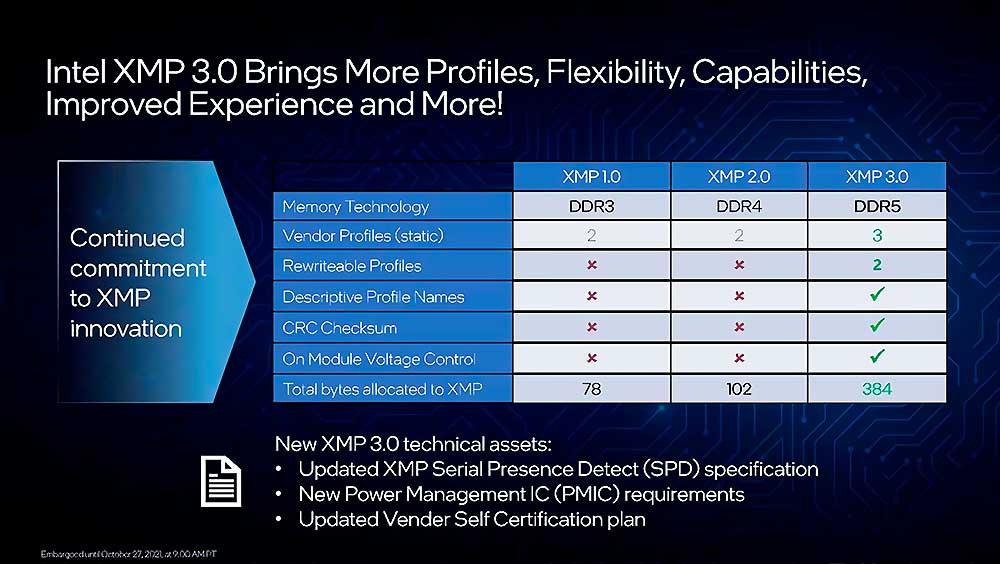

Estas tabelas incluem velocidades em MHz, relógios e tempos de acessos primários, secundários e terciários que são logicamente mais rápidos em alguns casos ou mais lentos em outros, mas que em todos os casos aumentam o desempenho geral da memória e com ela do sistema. Na primeira versão chamada por seu próprio nome, XMP, a Intel conseguiu incluir nela a inclusão de um perfil de leitura dentro da memória mais o do JEDEC (tecnicamente é um perfil, mas eles contam como dois)

O XMP 2.0 elevou o nível para dois perfis de leitura, onde os fabricantes poderiam estabelecer se desejavam dois valores e tabelas diferentes, personalizando a experiência do usuário e favorecendo desempenhos diferentes (três reais contando o JEDEC). Com o XMP 3.0, os fabricantes agora podem ter dois ou três perfis para incluir, podendo selecionar dois personalizados pelo usuário.

Atualização SPD

Um dos pontos-chave para o perfil XMP é precisamente o Especificação SPD ou Serial Presence Detect . Isso trouxe várias dores de cabeça aos fabricantes e usuários, principalmente porque eles podem ser gravados da EEPROM e, portanto, ficarem corrompidos. Existem alguns programas que podem fazer isso e, claro, cria travamentos no controlador de memória, uma vez que não consegue ler os valores corretamente do XMP e a memória fica inutilizável até que um novo flashing ocorra corretamente.

Agora e com o XMP 3.0 teremos dois perfis atualizáveis, o que ajuda para que se um estiver corrompido o outro possa deixar a memória funcionando, seu SPD possa ser extraído e posteriormente possa ser flasheado módulo por módulo, reparando a memória como se nada tivesse ocorrido.

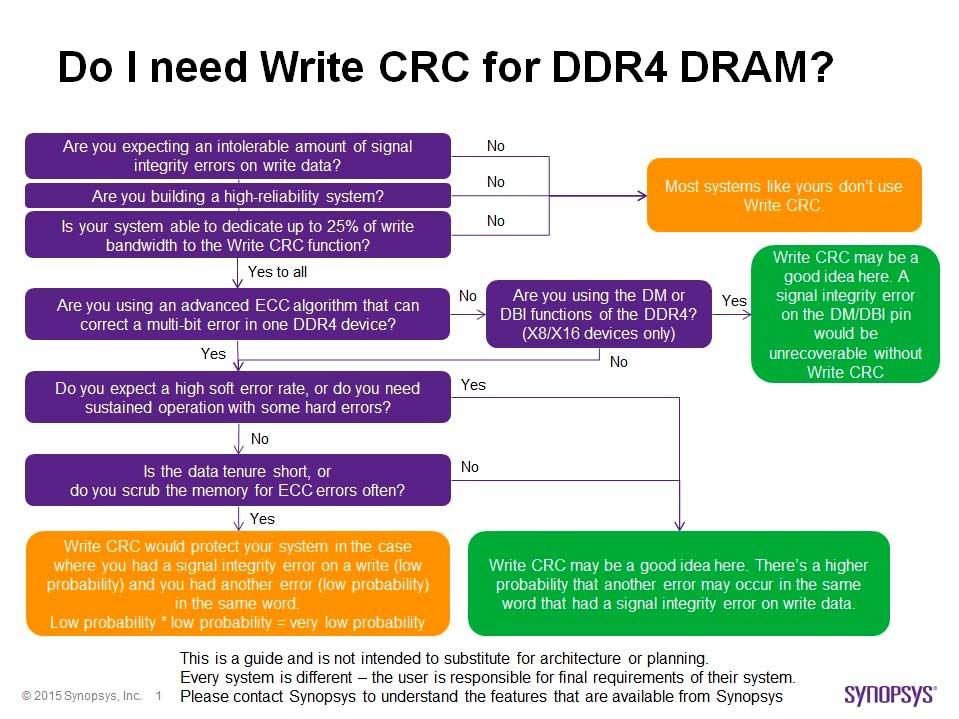

CRC soma de verificação

Curiosamente e já explicado isso, por que os módulos DDR4 com XMP 2.0 não possuem CRC? Não é exatamente assim e logicamente tem um porquê. O CRC como tal foi adicionado em sua versão Write no padrão JEDEC para DDR4, mas o código de redundância cíclica tem um problema: alto consumo de largura de banda. Os dados mostram o consumo de 25% da escrita total do sistema e, claro, não é aceitável perder essa quantidade de largura de banda com as margens e velocidades que movemos hoje.

Isso não é mais um problema com o DDR5, pois além de incluir o PMIC na própria memória, no módulo fisicamente falando, as velocidades são e serão monstruosas em relação ao DDR4, principalmente se tivermos banda dupla que integra este tipo de memória . Portanto, a Intel com XMP 3.0 integra o procurado CRC Checksum que protegerá os dados e integridade do SPD, bem como o CPU controlador de memória.

Maior aumento de espaço para XMP 3.0

Um dos aspectos fundamentais e já entendendo tudo o que falamos sobre o novo XMP 3.0 é que, logicamente, precisamos de mais espaço para abrigar tudo isso. Portanto, a Intel passou de 78 bytes por módulo para XMP 1.0 para 102 para XMP 2.0 e agora aumenta para 384 bytes de controle para XMP 3.0.

Isso é o que permite que perfis de memória predefinidos como SPD sejam selecionados a partir do motherboard BIOS / UEFI. A questão que temos então é o comportamento do IMC dos novos processadores Alder Lake e Meteor Lake (um salto de frequência significativo é esperado) com as diferentes velocidades que veremos dos fabricantes e chips.

Vamos ver perfis XMP 3.0 acima de 6000 MHz? O IMC das CPUs pode suportá-las sem transbordar a tensão e com isso o consumo e degradação? No momento sabemos que existem marcas trabalhando em perfis para DDR5-7000, então parece que ou essas novas memórias e chips estão conseguindo evoluir muito mais rápido que CPUs e seu IMC, ou isso significa que o potencial de upload e suporte / a resistência dos controladores de memória integrados é maior do que podemos pensar.

Deve-se ter em mente que embora o XMP 3.0 atinja velocidades muito altas em alguns módulos, é o IMC que determina se ele é capaz de suportar essa velocidade e sua tensão, que é logicamente independente da própria RAM.

Dito e esclarecido isso, só podemos dizer que a Intel deu um grande passo em frente, o maior desde o lançamento do XMP em 2007 e, como tal, agora é a AMD que vai ter que adaptar sua tecnologia e IMC a esses novos requisitos com o Zen. Quatro.