O conceito de Cache DRAM consiste em adicionar um nível adicional de cache entre o processador e o RAM memória para aumentar o desempenho do primeiro. Mas, que mudanças isso significa na arquitetura de um processador e como funciona esse conceito? Explicamos para você e, incidentalmente, quais processadores usarão essa arquitetura.

Alguns dias atrás, um Apple surgiu uma patente em que se mencionou o uso de Cache DRAM em um de seus futuros processadores, um conceito que embora possa parecer exótico não é, então vamos desmistificá-lo.

Memória DRAM como cache, uma contradição

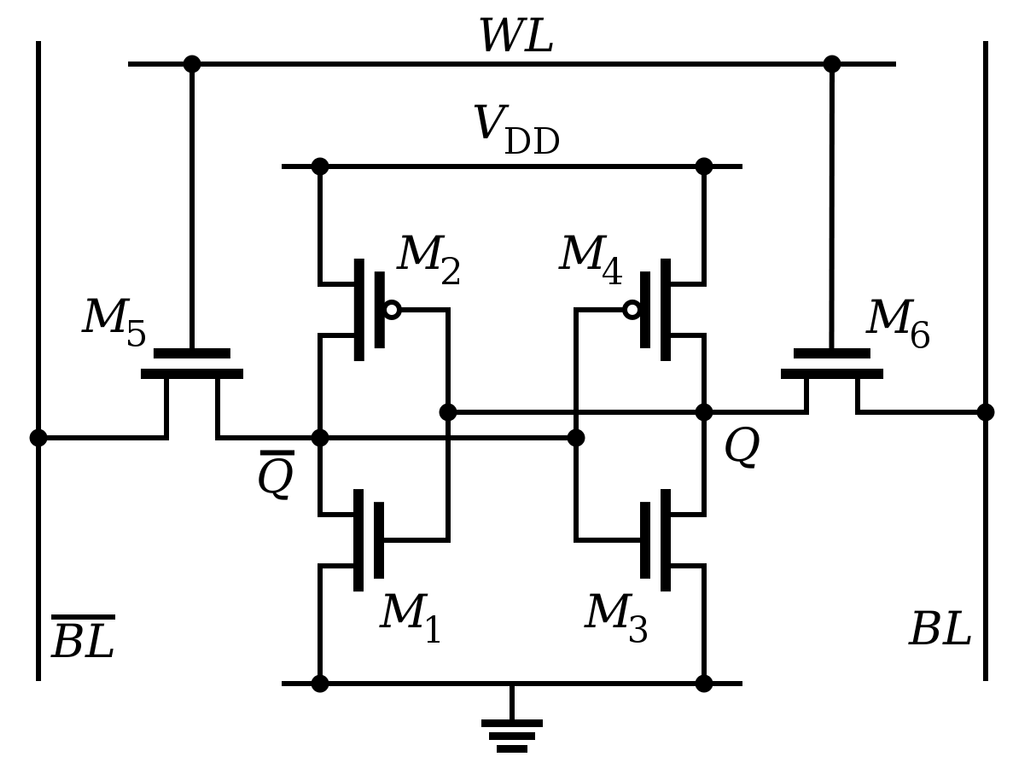

Todas as memórias RAM atuais que são usadas fora de um processador são do tipo DRAM ou RAM dinâmica, enquanto as memórias que são usadas dentro dos processadores são RAM estática ou SRAM. Ambos funcionam praticamente da mesma forma em termos de acesso aos dados, mas o que não são iguais é a maneira como armazenam um pouco de memória.

A memória DRAM é muito mais barata, mas por sua natureza requer atualização constante e sua velocidade de acesso é mais lenta do que a SRAM, portanto, geralmente não é usada em processadores. Por outro lado, ele escala de forma pior do que DRAM, então apesar do fato de que a IBM tem usado memória DRAM como um cache de último nível em suas CPUs para computação de alto desempenho, POWER, em sua próxima geração eles usarão SRAM memória.

Portanto, o conceito de cache, que está relacionado a uma memória do tipo SRAM, junto com o conceito de DRAM em princípio não combinam e embora tenhamos o caso de CPUs IBM não vamos falar sobre o uso de memória DRAM como cache dentro o processador.

Cache DRAM e memória HBM como exemplo

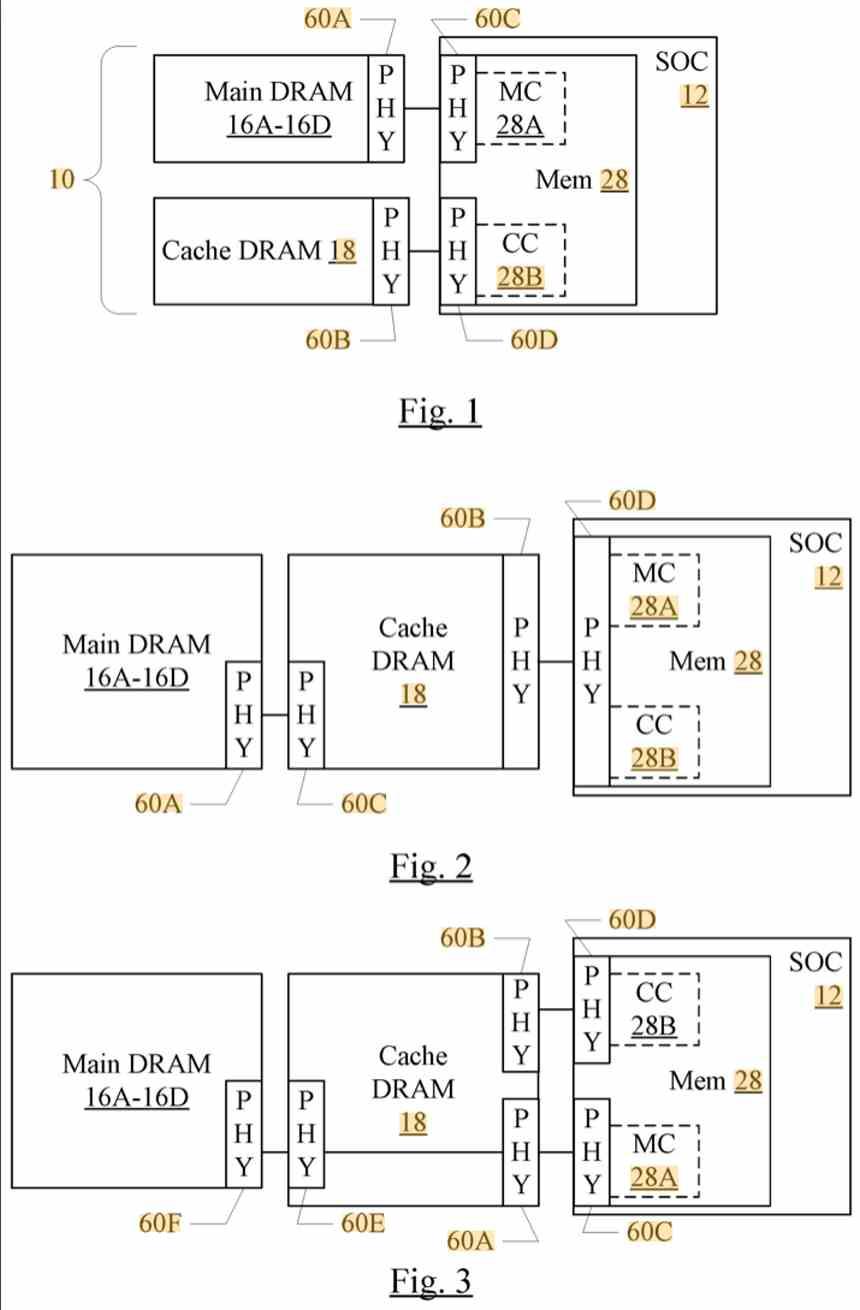

Cache DRAM é o conceito de adicionar uma camada adicional na hierarquia de memória entre o cache de último nível do processador e a memória principal do sistema, mas construída por meio de uma memória DRAM com maior velocidade de acesso e menos latência do que a DRAM usada como memória principal.

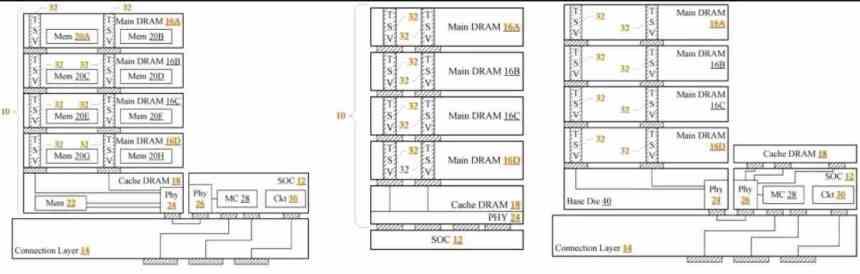

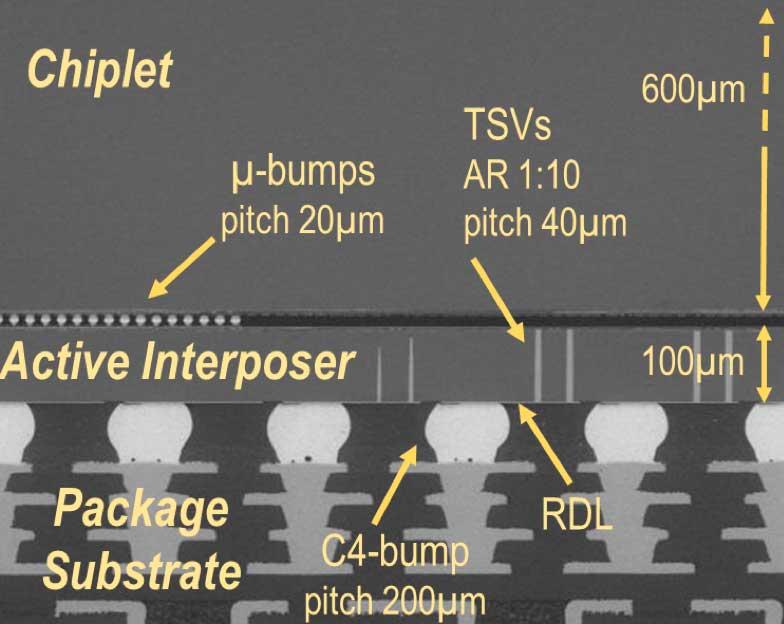

Uma maneira de conseguir isso é usando a memória do tipo HBM como um cache DRAM, que é um tipo de memória DRAM na qual diferentes chips de memória são empilhados e conectados verticalmente usando um tipo de cabeamento chamado TSV ou through-path. silício pelo fato de passarem pelos chips. Este tipo de conexão também é usado para a construção de memória 3D-NAND.

Como a conexão é vertical, é necessário um interposer, que é uma peça eletrônica em forma de placa que é responsável por comunicar o processador e a memória HBM. Tanto o processador, seja CPU or GPU, são montados no referido interposer, o que devido à curta distância dá à memória HBM a capacidade de funcionar como um tipo de memória DRAM com menor latência do que as memórias DDR e GDDR clássicas.

Deve ser esclarecido que se a DRAM estivesse mais próxima do processador, como uma configuração 3DIC a coloca logo acima dela, então o nível de latência em relação à memória HBM seria menor e, portanto, a velocidade de acesso maior, devido ao fato de os elétrons possuírem para viajar uma distância mais curta.

Nós realmente usamos a memória HBM para dar uma ideia, mas qualquer tipo de memória em uma configuração 2.5DIC funciona como um exemplo.

Mas um mediador padrão não é suficiente

O próximo problema é que um cache não funciona da mesma forma que uma memória RAM, pois o que o sistema de busca de dados do processador não copia as linhas de instrução da RAM uma a uma, mas sim o sistema de memória. O que o cache faz é copiar o fragmento de memória onde a linha de código atual está localizada no último nível do cache.

O último nível armazena o cache de um processador é compartilhado por todos os núcleos, mas à medida que nos aproximamos do primeiro nível, eles se tornam mais privados. Deve ser esclarecido que em ordem decrescente cada nível de cache contém um fragmento do cache anterior. Quando um processador procura dados, o que ele faz é procurá-los em ordem crescente de níveis de cache, onde cada nível tem mais capacidade do que o anterior.

Mas, para que a memória HBM se comporte como um cache, precisamos que o elemento que comunica o processador com a referida memória, o interposer, tenha os circuitos necessários para se comportar como uma memória cache. Portanto, um mediador convencional não pode ser usado e é necessário adicionar circuitos adicionais no mediador que permite que a memória HBM se comporte como um cache de memória adicional.