Algumas semanas atrás, ARM introduziu a nona geração do conjunto de registradores e instruções usados em processadores com o ISA de mesmo nome. ARMv9 é o nome com o qual a nova versão deste ISA foi batizada, que será usado em futuros SoCs para dispositivos PostPC. O que é ARMv9 e o que há de novo nas versões anteriores, como serão as futuras CPUs ARM?

Um ISA nada mais é do que a linguagem compreendida pelos diferentes processadores e, portanto, marca o que o conjunto de uns e zeros significam no código que executam. O binário para um x86 CPU não tem o mesmo significado que o binário para uma CPU ARM, por exemplo.

No entanto, o avanço da tecnologia torna necessário adicionar novas instruções às ISAs, o que lhes dá a capacidade de adicionar novas funcionalidades para aumentar seu desempenho, segurança no processamento de dados ou para enfrentar novos desafios que lhes são apresentados.

Neste artigo vamos falar sobre a nona geração do ISA ARM, que depois de anos voltada para CPUs e microcontroladores de baixo consumo, decidiu ser mais ambiciosa e entrar no mercado que exige o melhor desempenho, o de data centers e alto desempenho computação ou HPC.

Extensões Vetoriais Escaláveis 2

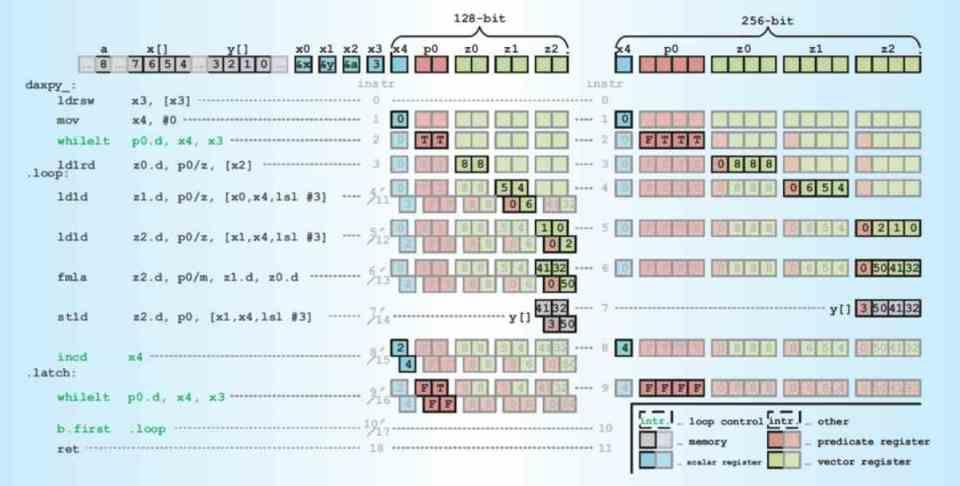

A Fujitsu japonesa criou para seu núcleo ARM uma série de extensões proprietárias chamadas SVE, que significa Scalable Vector Extensions. Pelo nome, você deve ter adivinhado que estamos falando de um conjunto de instruções SIMD. Não vamos esquecer que em CPUs com ISA ARM por anos as instruções Neon foram usadas. Que será substituído pelas instruções SVE2 em ARMv9.

SVE foi criado pela Fujitsu para seu supercomputador Fugaku, que faz uso de seus núcleos A64-FX. A intenção? Aproveite o paralelismo de dados exigido pela computação científica, que usa números de maior precisão. Isso se traduz em unidades SIMD muito maiores e, portanto, mais bits.

Já que o interesse da ARM é trazer seus núcleos para o mercado de computação de alto desempenho e servidores, eles decidiram adotar o SVE e fundi-lo com o Neon para criar o SVE2. A maior vantagem que o SVE adiciona ao Neon? Estas são instruções independentes de tamanho, portanto, não é necessário ter uma versão de cada instrução para tamanhos diferentes, como é o caso com as instruções AVX no x86.

Reinos de memória em ARMv9

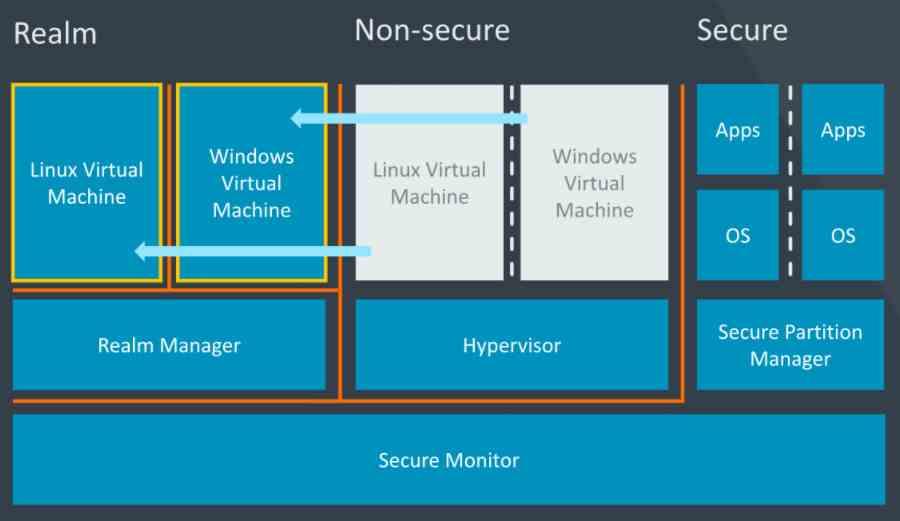

Um conceito interessante que o ISA ARMv9 agrega à equação é o conceito de reinos, que consiste em poder tomar parte do endereçamento da memória e fazer com que o código que nela se executa não afete o resto do sistema, portanto é totalmente isolado. O que é ideal para a implementação de máquinas virtuais onde um sistema operacional é executado ao mesmo tempo que outro na mesma CPU.

Normalmente, as CPUs têm diferentes níveis de privilégio, mas com o conceito de realms que foi adicionado no ARMv9, será possível executar mais facilmente máquinas virtuais em uma CPU com ARM ISA, mas as vantagens disso não se limitam apenas às máquinas virtuais, mas também pode ser usado em aplicações específicas.

Portanto, o ARMv9 parece ser uma extensão do ISA mais preparada para data centers e outros tipos de computadores onde a virtualização e a segurança são muito mais importantes do que outras funcionalidades. Não surpreendentemente, a ARM está travando uma guerra contra Intel e AMD no mercado de CPU para servidores, onde os processadores x86 dominavam o mercado até agora.

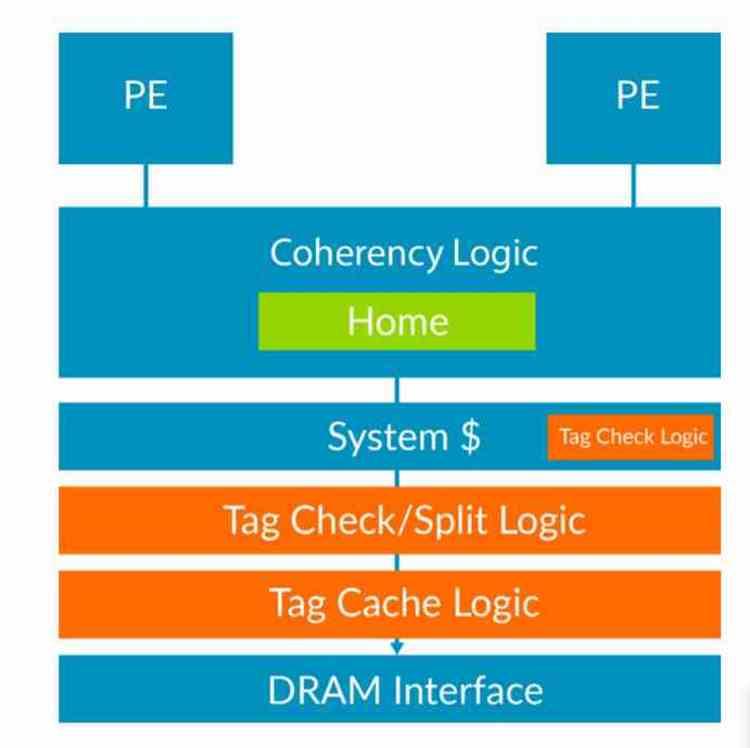

Extensões de marcação de memória

Eles não são novos no ARMv9, mas sim na versão 8.5. Sua utilidade? É um mecanismo encarregado de rastrear todos os acessos ilegais à memória feitos por programas. Um acesso ilegal nada mais é do que um acesso a um endereço de memória que o programa não tem permissão para acessar. Qual a utilidade disso? Pois serve para evitar o chamado buffer overflow, um problema de segurança comum em todos os processadores que ocorre quando a quantidade de dados copiados excede a reserva de memória, escrevendo códigos inesperados em endereços de memória vizinhos.

Se o estouro de memória for bem-sucedido, o código original será substituído por um novo código na memória, que será executado pela CPU assim que atingir a memória. Portanto, é importante evitar isso, especialmente se estivermos falando de data centers que tendem a servir milhões de usuários ao mesmo tempo e onde um estouro de buffer pode ser usado para roubar dados de usuários comprometidos.

O MTE não faz parte do próprio ISA, mas é um mecanismo implementado nas CPUs do Northbridge do ARMv9 que rastreia todos os acessos à memória e cuja funcionalidade é evitar overflows de forma transparente.

ARMv9 apenas para data centers e servidores?

As novidades do ISA ARMv9 que descrevemos nas seções anteriores têm um caráter específico marcado e nada têm a ver com o uso nos dispositivos clássicos em que o ISA ARM costuma ser visto. De todos eles, ele chama o SVE de forma poderosa, já que uma das razões pelas quais você não costuma ver grandes unidades SIMD em CPUs para dispositivos PostPC é o enorme consumo de energia que seu uso supõe.

No momento, os únicos dois núcleos anunciados pela ARM são dois da família Neoverse. Por um lado, o NeoVerse V1 com o codinome “Zeus” e, por outro, o Neoverse N2 com o codinome “Perseus”. Não são núcleos que você verá em um futuro smartphone, mas em data centers e servidores para computação de alto desempenho de empresas como Amazon AWS, Oracle, Tencent, Google, etc.

ARM ainda não anunciou nenhum kernel para dispositivos PostPC, como smartphones e tablets. Embora não possamos esquecer que o objetivo do ARM é deslocar o x86 em vários mercados, não só nos servidores, mas também no PC. A compra por NVIDIA e sua grande influência no mercado de videogames para PC pode trazer a chegada de PCs para jogos com ARMs e GPUs NVIDIA, embora seja um futuro que precisará de muito suporte dos desenvolvedores de videogames e não da própria NVIDIA-ARM.