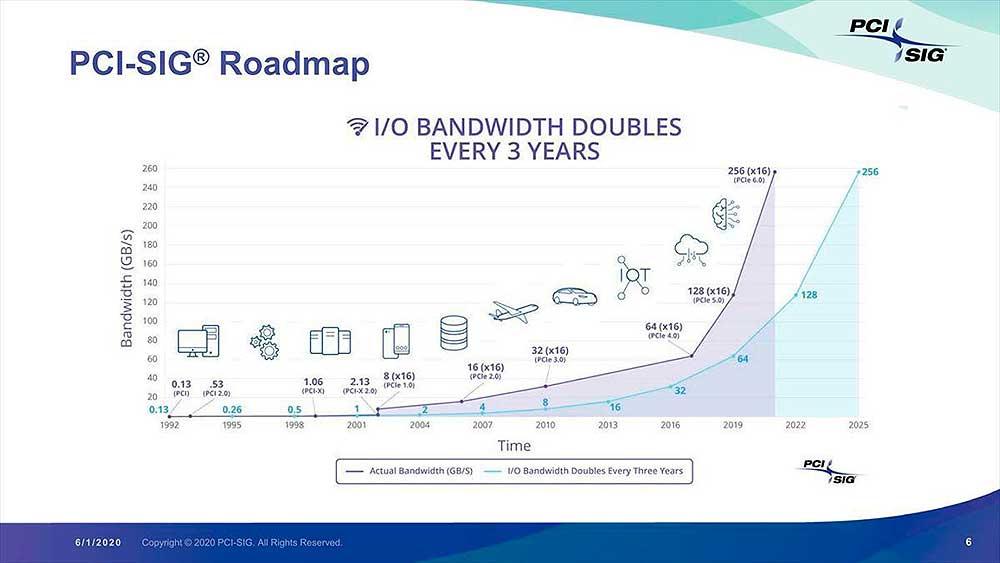

PCI Express technology has long been used to connect graphics cards and other peripherals such as NVMe SSDs. The implementation of the fifth generation of the interface occurs with the arrival of the Alder Lake processors from Intel and the Zen 4 processors from AMD. But the PCI Express 6.0 specification has been finalized and brings several improvements over the fifth generation.

The PCI Express 6.0 follows from the outset the same improvements as the previous generations of this interface, that is, it is based on doubling the bandwidth compared to the previous generation. However, in the case of PCI Express 6.0, profound changes have been needed in the development of the sixth generation of this interface.

The bandwidth of PCI Express 6.0 is 128 GB / s for a 16-line interface, an exaggeratedly high bandwidth for an I / O interface and that is a four-fold jump compared to the current PCI Express 4.0 that we are using for current graphics cards. The jump also means a jump from NVMe SSD flash controllers from 7-8 GB / s to 28 -32 GB / s with PCI Express 6.0.

Backward compatibility and the problem of signal instability

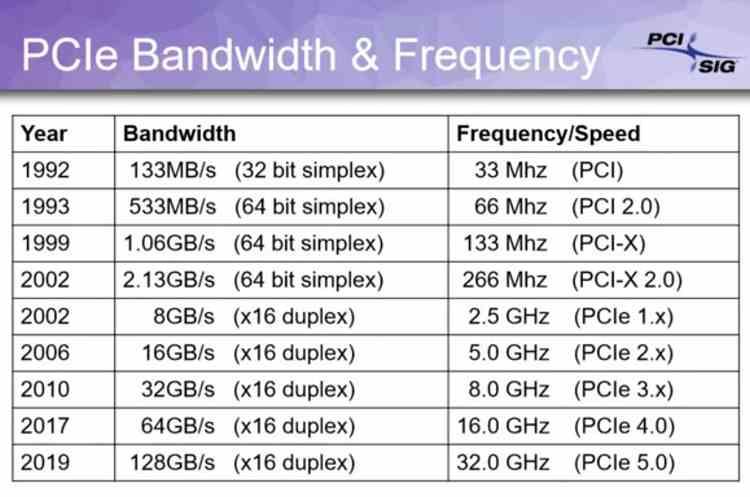

The PCI Express interface has always been backwards compatible with previous versions of the protocol, this means that we can plug a PCI Express 1.0 card into a PCI Express 6.0 slot and it will work because the pinage will be exactly the same. So it is not possible to increase the number of pins to increase the bandwidth without increasing the speed. The solution? Increase the clock speed at which the interface works.

The problem with PCI Express 6.0? As we increase the clock speed of an interface it becomes more unstable with distance and after six generations they have had to make changes to the interface due to the high speed at which the interface works in a traditional way. And if you look at the table that accompanies these lines we are talking about a theoretical speed of 64 GHz, which deforms the signal enough, even at the short distance both ends are in a PCI Express interface.

This has forced a series of measures to be adopted to make the leap to PCI Express 6.0 possible.

First of the improvements in PCI Express 6.0, use of PAM4

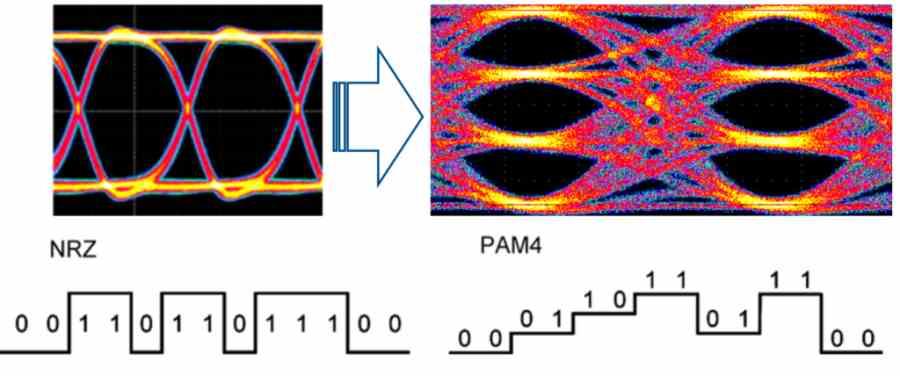

How does an external or internal interface of a chip know if the value is a 1 or a 0? Well, simple, depending on the voltage in which the information is transmitted. Binary systems are based on the use of two voltages with enough distance between them so that the voltage drop or rise makes the signal not confused. In analog systems a simple variation in the voltage supposes a change in the information. For this reason computers speak in binary.

What does this have to do with PCI Express 6.0? Since we cannot increase the bandwidth because the signal is distorted and neither the number of pins for backward compatibility, a solution has to be found and this goes through the use of PAM4 encoding or Pulse Amplitude Modulation, which we have already seen in the GDDR6X and is not based on the use of two voltage values but 4 voltage values for each pin. In this way we can encode the values 00, 01, 10 and 11 on each pin. Four values in total, instead of the two classic values that would be 0 or 1.

The solution avoids increasing the bandwidth and the pins, but it tells us that in PCI Express 7.0 it will no longer be possible from conventional methods. We may see the use of photonics and optical interfaces, but with the improvements to the PCI Express 6.0 fresh out of the oven, better be patient with its successor.

Changes in the package system

The jump to PAM-4 has changed the way in which the PCI Express 6.0 interface sends its packets, despite the fact that it is compatible with previous generations by communicating in the traditional PAM-2 or NRZ mode. The reality is that the PAM-4 format does not support the previous packet system and therefore the communication protocol has changed because of it.

The first change has been the so-called Forward Error Correction or FEC, which is the new protocol for correcting errors in sending data. The problem is that the bandwidth to be processed is so high that the FEC adds enormous latency when sending the data. To alleviate this, the PCI Express 6.0 standard uses a type of package called FLIT. A packet is nothing more than a set of bits with a specific destination. The send latency of each FLIT? It depends on the number of lines on the interface, but each packet has a latency of only 2 ns on a 16-line PCI Express 6.0, but goes up to 32 ns on a single-line interface.

The FEC only works with fixed sizes, that is why the FLIT has a size of 256 bytes per send. Each packet or TLP can have a size ranging from 0 bytes to 4096 bytes and therefore each packet can be made up of several FLITS.

Third upgrade to PCI Express 6.0, variable consumption

PCI Express 6.0 adds a new low-power state dubbed L0P. This mode allows the interface to cut its power consumption when the data flow being sent is lower than the interface can transmit. To do this, the clock speed at which the interface works at specific moments of data transmission varies, all without causing a stoppage that adds latency to the data transmission.

The problem is that this mechanism is associated with FLITS and FEC and therefore with PAM4, which means that it is only possible to use in PCI Express 6.0 mode and not in the other modes.