Et av de mest utbredte konseptene innen databehandling i dag er utvilsomt XMP. Enhver bruker som er moderat interessert i maskinvare vet at når vi snakker om minneoverklokkingsprofiler, Intel har tatt mål av AMD, som hele tiden prøver å tilpasse seg disse kravene gjennom sin AMP-teknologi. Med avgangen av Alder Lake-S som en revolusjonerende arkitektur, har Intel gått et skritt videre ved å presentere XMP 3.0 , men hvilke nyheter skjuler det?

Noen lurer på årsakene til Intels avgjørelser mht RAM og spesifikt XMP. Selv om vi aldri får vite det, er sannheten at overgangen fra DDR4 til DDR5 var en ideell tid fra overklokkings perspektiv for å implementere endringer og forbedringer, siden som vi ser 4,800 MHz av JEDEC de blir liggende igjen bare dager etter at Core 12 CPUer vil bli introdusert.

Derfor, og gitt hvor raskt produsenter akselererer og oppdaterer modulene sine med økende seriehastigheter, gjenstår det bare å lure på, har Intel tatt hensyn til dette? Er XMP 3.0 oppdatert med hva som kreves av det?

Intel XMP 3.0, en nødvendig vri

eXtreme Memory Profile eller XMP har vært med oss siden 2007 og i denne tredje versjonen ser vi tilbake og etter 14 år er det normalt for den blå giganten å lansere en ny revisjon med nyheter. Hvorfor? For endringene som DDR5 antar med hensyn til DDR4. Vi vil ikke gå inn på dette emnet siden vi allerede har behandlet det i forlengelse, men hvis det er noe å si om XMP 3.0 er det at det er eksklusivt for DDR5 som sådan.

Begrepet profil av navnet kommer til fingeren for å forklare det første av punktene der Intel har gitt produsentene, siden som vi godt vet er denne teknologien basert på gjenkjennelse av en serie konfigurasjonstabeller som hver produsent integrerer for å smake etter modell , brikke og minneversjon for å få IMC til å gjenkjenne og bruke disse innstillingene gjennom fastvaren.

Hva er nytt i Intel XMP 3.0

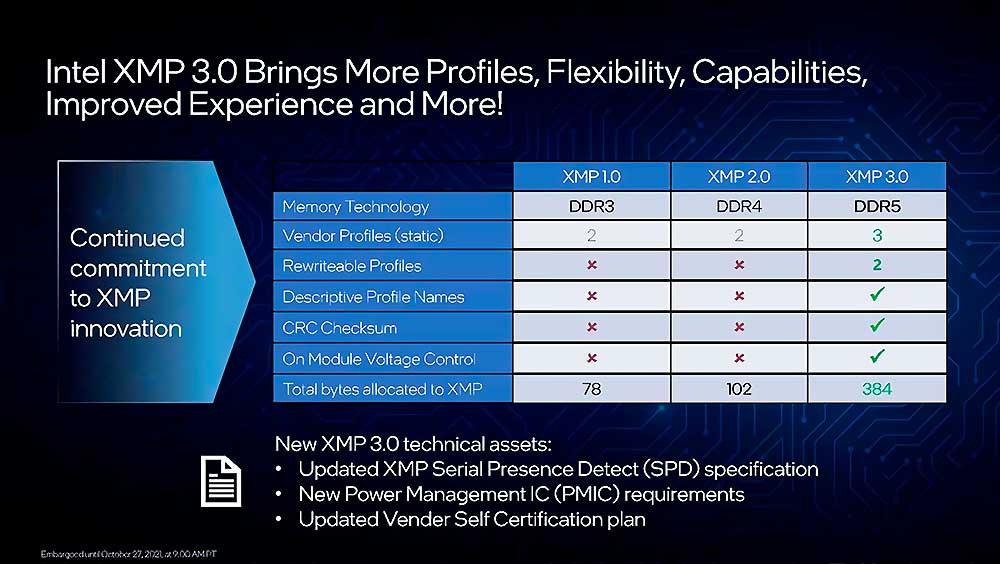

Disse tabellene inkluderer hastigheter i MHz, klokker og tider for primær, sekundær og tertiær tilgang som er logisk raskere i noen tilfeller eller langsommere i andre, men som i alle tilfeller øker den generelle ytelsen til minnet og med det systemet. I den første versjonen kalt med sitt eget navn, XMP, klarte Intel å inkludere inkluderingen av å lese en profil i minnet pluss den til JEDEC (teknisk sett er det én profil, men de regnes som to)

XMP 2.0 hevet nivået til to leseprofiler, der produsenter kunne fastslå om de ønsket to forskjellige verdier og tabeller, tilpasse brukeropplevelsen og favorisere forskjellige ytelser (tre virkelige teller JEDEC). Med XMP 3.0 kan produsenter nå ha to eller tre profiler å inkludere, og kunne velge to tilpasset av brukeren.

SPD-oppdatering

Et av nøkkelpunktene for XMP-profilen er nettopp SPD eller Serial Presence Detect-spesifikasjon . Dette har ført til flere hodepine for produsenter og brukere, hovedsakelig fordi de kan skrives fra EEPROM og derfor blir ødelagt. Det er noen programmer som kan gjøre det, og selvfølgelig skaper det krasj i minnekontrolleren, siden den ikke kan lese verdiene riktig fra XMP og minnet er ubrukelig før en ny blinking skjer riktig.

Nå og med XMP 3.0 vil vi ha to oppdaterbare profiler, noe som hjelper slik at hvis den ene er ødelagt kan den andre la minnet fungere, SPD kan trekkes ut og senere kan det bli flashet modul for modul, og reparere minnet som om ingenting hadde gjort det. skjedde.

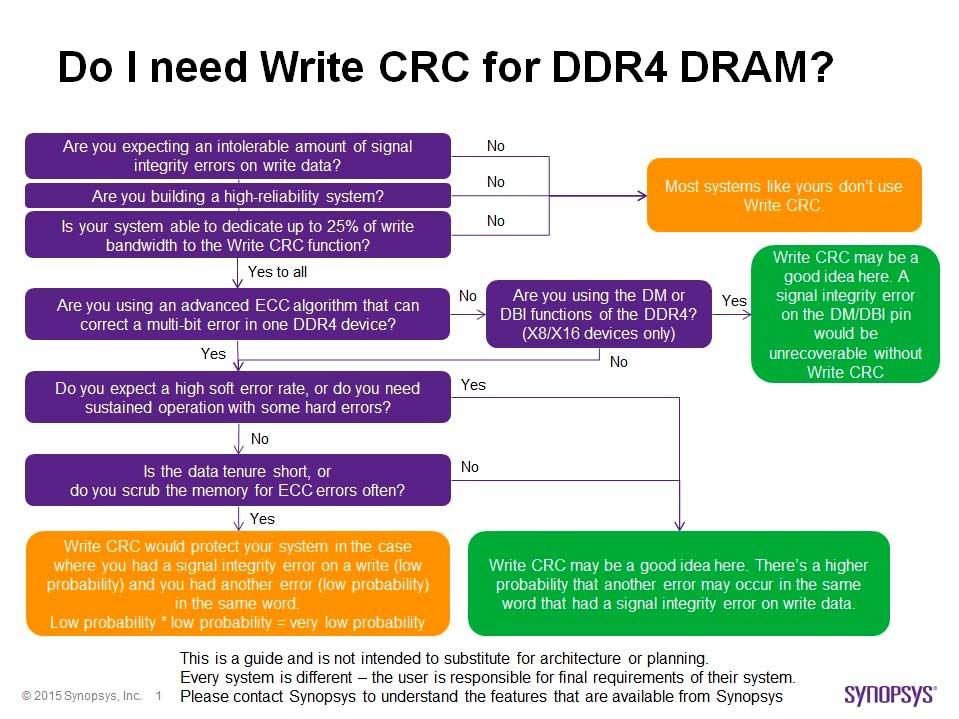

CRC-sjekksum

Merkelig nok og allerede forklart dette, hvorfor har ikke DDR4-moduler med XMP 2.0 CRC? Det er ikke akkurat slik, og logisk sett har det et hvorfor. CRC som sådan ble lagt til i sin Write-versjon i JEDEC-standarden for DDR4, men den sykliske redundanskoden har et problem: høyt båndbreddeforbruk. Dataene viser forbruk av 25 % av den totale skrivingen av systemet og selvfølgelig er det ikke akseptabelt å miste den mengden båndbredde med marginene og hastighetene vi beveger oss i dag.

Dette er ikke lenger et problem med DDR5, siden i tillegg til å inkludere PMIC i selve minnet, i modulen fysisk sett, er og blir hastighetene monstrøse sammenlignet med DDR4, spesielt hvis vi har dobbel båndbredde som integrerer denne typen minne . Derfor integrerer Intel med XMP 3.0 den ettertraktede CRC Checksum som vil beskytte dataene og integriteten til SPD så vel som prosessor minnekontroller.

Større plassøkning for XMP 3.0

Et av nøkkelaspektene og allerede å forstå alt vi har sagt om den nye XMP 3.0 er at vi logisk nok trenger mer plass til å huse alt dette. Derfor har Intel gått fra 78 byte per modul for XMP 1.0, til 102 for XMP 2.0 og hever den nå til 384 byte med kontroll for XMP 3.0.

Dette er det som gjør at forhåndsinnstilte minneprofiler som SPD kan velges fra hovedkort BIOS / UEFI. Spørsmålet vi har da er oppførselen til BMI-en til de nye Alder Lake- og Meteor Lake-prosessorene (et betydelig frekvenshopp forventes) med de forskjellige hastighetene som vi kommer til å se fra produsentene og brikkene.

Kommer vi til å se XMP 3.0-profiler over 6000 MHz? Kan BMI-en til CPU-ene støtte dem uten å renne over spenningen og med det forbruket og degraderingen? For øyeblikket vet vi at det er merker som jobber med profiler for DDR5-7000, så det ser ut til at enten disse nye minnene og brikkene klarer å utvikle seg mye raskere enn CPU-er og deres BMI, eller det betyr at potensialet for opplasting og støtte / utholdenheten til de integrerte minnekontrollerne er større enn vi kanskje tror.

Det må tas i betraktning at selv om XMP 3.0 når svært høye hastigheter i enkelte moduler, er det IMC som avgjør om den er i stand til å støtte nevnte hastighet og dens spenning, som er logisk uavhengig av selve RAM-en.

Når dette er sagt og avklart, kan vi bare si at Intel har tatt et veldig stort skritt fremover, det største siden de lanserte XMP i 2007, og som sådan er det nå AMD som må tilpasse sin teknologi og IMC til disse nye krav med Zen. Fire.