I går snakket vi om fordelene som Intel hadde over AMD, hvor en av seksjonene nettopp var den for innovasjon. Bevis på dette er det som ble presentert av Intel for sin 3D-stablingsteknologi, som vil danne fremtidens høyytelsesbrikker, ikke uten problemer selvfølgelig. Det ser ut til at selskapet har funnet løsningen på nesten alle problemene som denne teknologien medfører gjennom det de har kalt Intel ODI.

Før vi går inn på å forklare hva denne teknologien består av, må vi forstå hva som har vært årsakene til at Intel har utviklet den, hva har vært problemene og hvor var begrensningene.

Bare på denne måten kan vi forstå kompleksiteten i hele denne saken og hvordan selskapet har klart å løse disse problemene på en veldig intelligent måte.

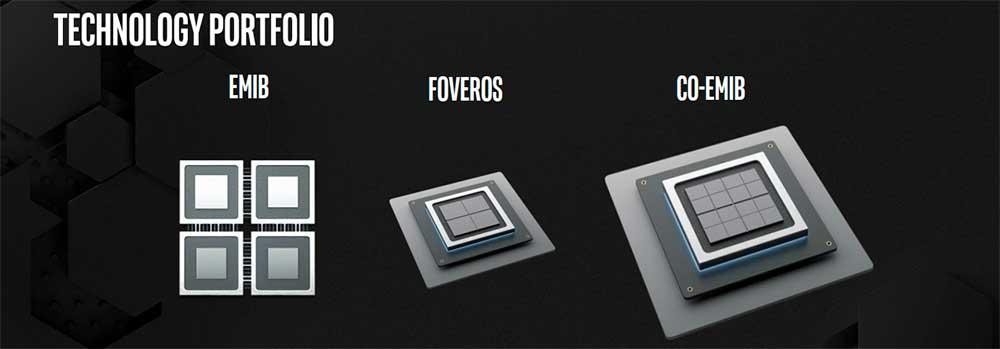

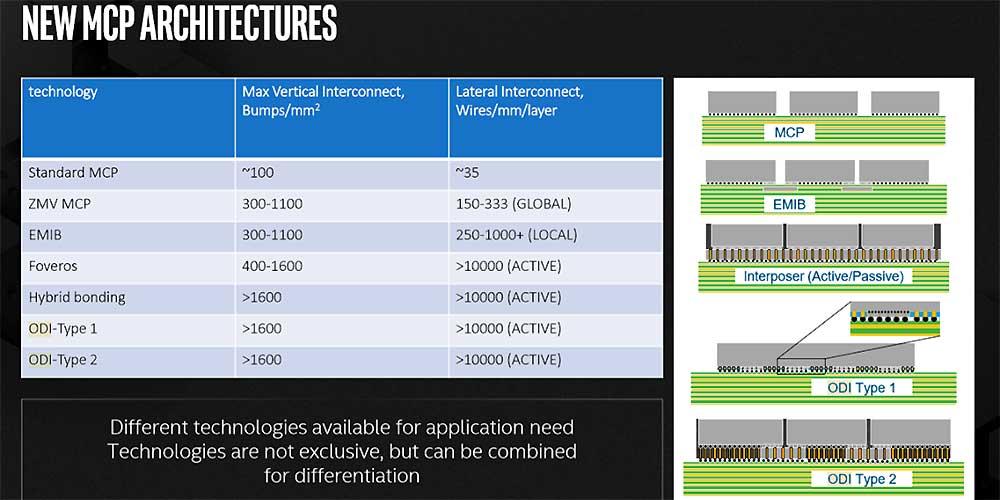

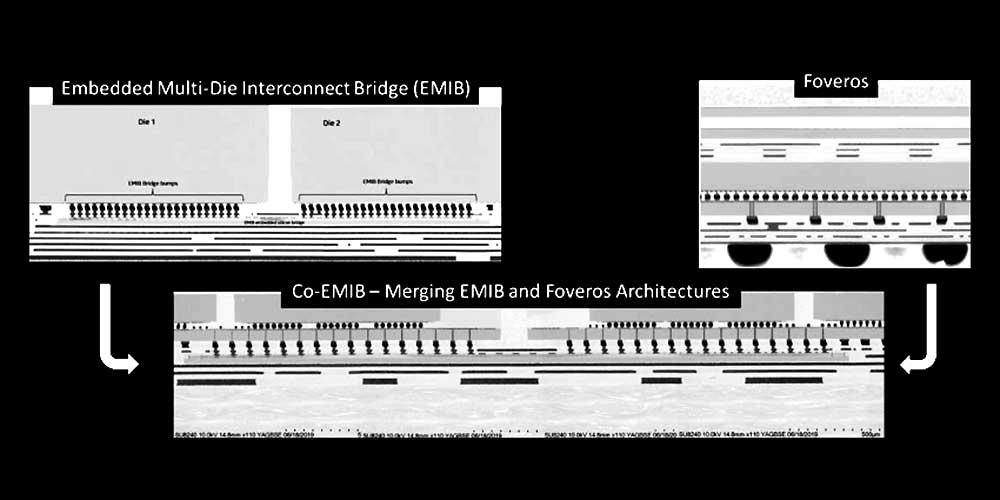

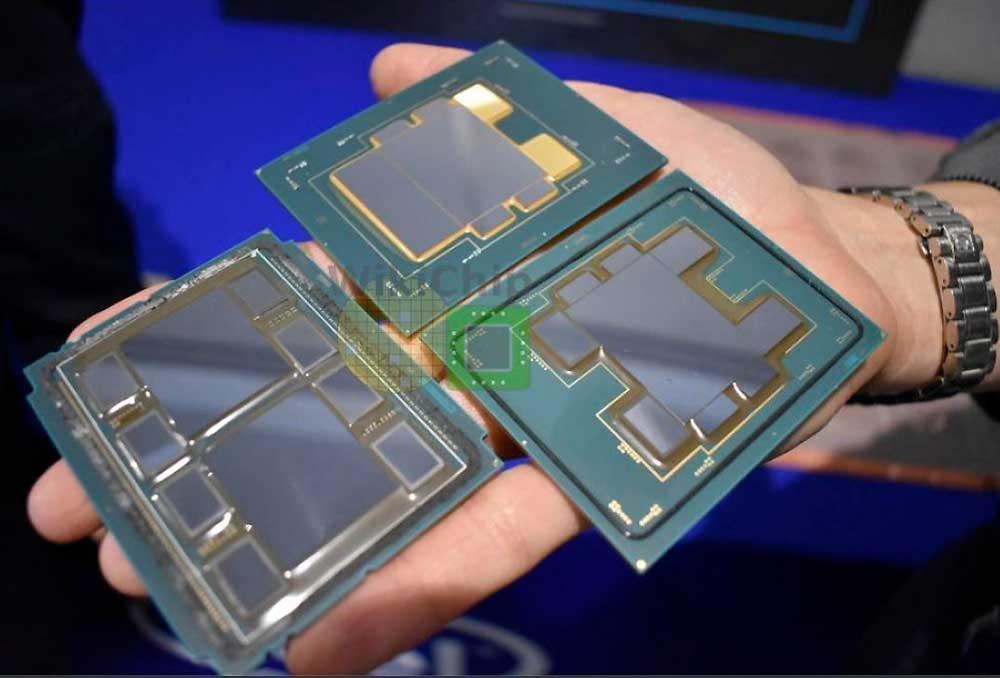

For det første, og for å lage et mentalt opplegg, jobber Intel for tiden med tre forskjellige stablingsteknologier som spenner fra minst til mest komplekse: EMIB, Foveros og CO-EMIB.

Den første er den såkalte 2.5D-teknologien, den andre er den første virkelige 3D-generasjonen, mens den siste kombinerer begge for å tilby mye mer komplekse produkter. Selv om vi allerede har sett dem hver for seg, vil vi gjøre en rask gjennomgang av dem alle for å plassere oss selv igjen.

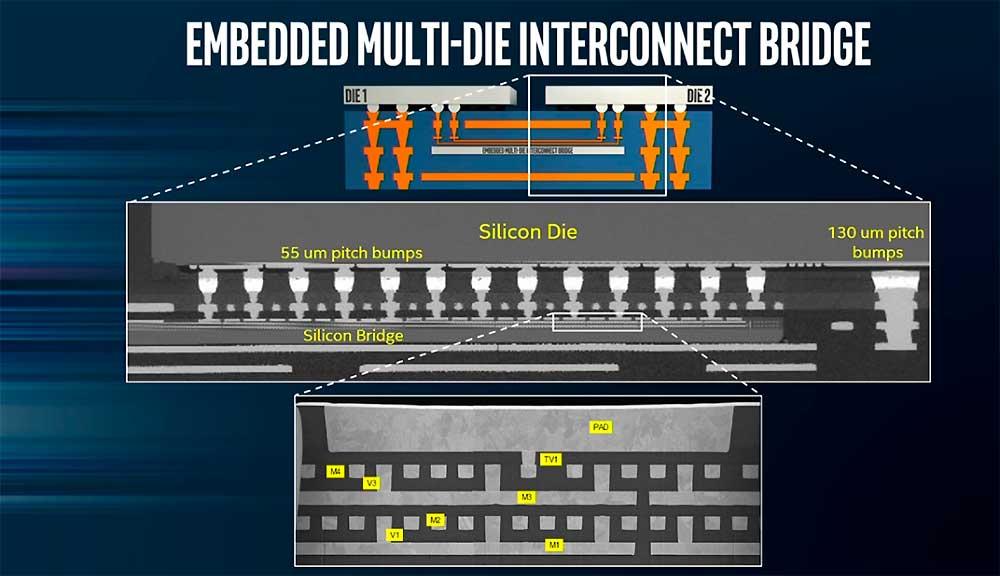

Intel EMIB

Forkortelse for Embedded MultiInterconnect Bridge, det er et 2.5D-system som allerede er kjent for oss, siden det debuterte med Kaby Lake G og inkluderte en Intel die med tilhørende kjerner, cache, registre osv ..., en die som tilhører AMD gjennom en RX Vega M og en 4 GB HBM2-stabel, alt i en enkelt interposer som ble loddet til bærbare hovedkort.

EMIB er derfor en mellomstor teknologi for sammenkobling som lar deg hente ut full ytelse til hver brikke som er inkludert i interposeren.

Intel Foveros

Det er det første trinnet i revolusjonen som vi vil være vitne til, ekte 3D-stabling. Dette er ikke annet enn å sammenkoble forskjellige dyse vertikalt, den ene på toppen av den andre, i stedet for horisontalt slik det er gjort til nå.

Det er det Intel kaller Ansikt til ansikt og representerer en serie ganske interessante og samtidig noe logiske problemer. Det første er et elektrisk problem, siden det er nødvendig å bringe nok energi til den øvre dysen, og for å gjøre dette, er det nødvendig å gå gjennom den / de mellomliggende ene. Dette ble delvis løst med TSV-samtalene, men disse er motvillige til å levere store mengder spenning, og selv om du kan legge til mer dette kan løses, er det problemet at den dyreste av en 3D-brikke for tiden nettopp er å legge til TSV av kvalitet og volum.

Til slutt står Intel overfor et temperaturproblem. Den øvre matrisen kan kjøles, men samtidig representerer den en termisk motstand for de nedre, ettersom den øvre matrisen hindrer overføring av varme og genererer et kjedeproblem ved hver vertikalform.

Intel CO-EMIB

Det er i utgangspunktet en sammenslåing, å kalle det på en eller annen måte, mellom EMIB og Foveros. Det er en 3D-stabling der den horisontale lengden brukes og lindrer derfor på noen måte problemene til begge deler, men løser dem ikke.

Så Intel måtte komme med en ny teknologi som var kompatibel med alle tre emballasjemodellene sine, og som samtidig gjorde slutt på alle problemene vi har snakket om, og det er nettopp her ODI kommer inn.

Intel ODI

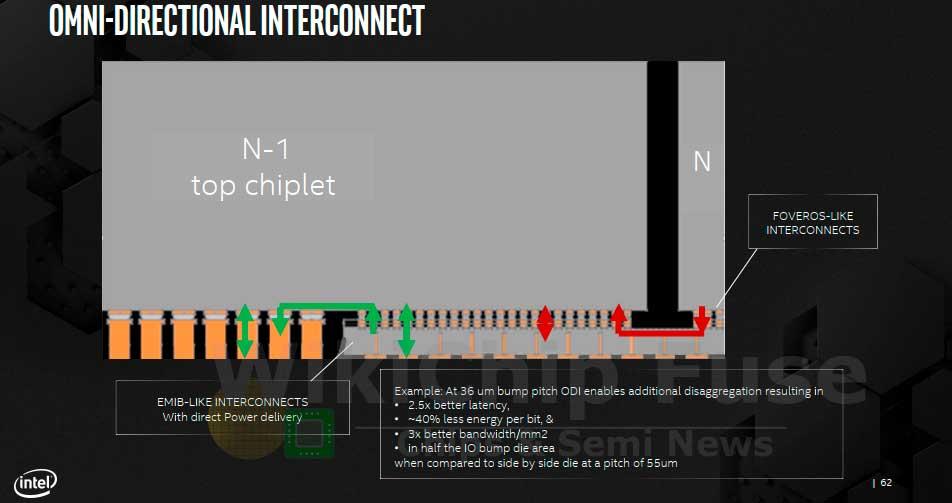

ODI er forkortelsen for Omni-Directional Interconnect og det er ikke en teknologi i seg selv, men en gruppe av dem, det vil si, ODI omfatter en serie spesifikke løsninger som kan øke over tid eller utvikle seg som sådan.

Hovedfunksjonen er basert på kraftlevering og tar sikte på å avslutte problemene til EMIB og Foveros, siden å gjøre dette som standard ender problemene med CO-EMIB.

Alt er basert på hva Intel kaller 3D-emballasje Flows , som ikke er noe annet enn interne samtrafikkveier for å forbedre ankomsten av energi og samtidig forbedre varmespredningen med en enkelt type teknologi.

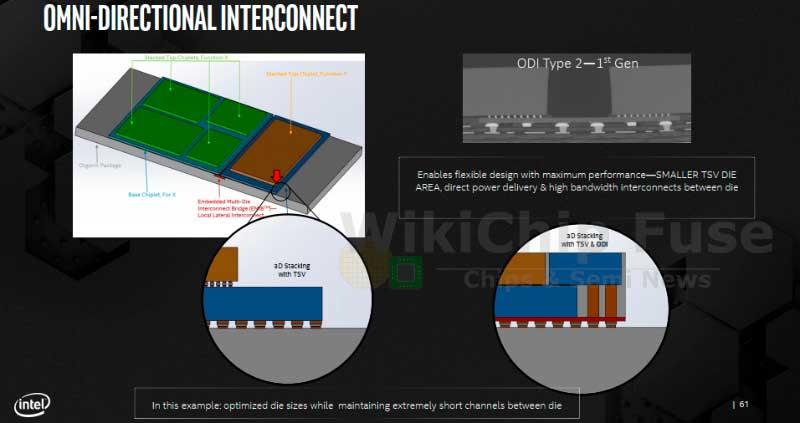

For øyeblikket er Intel ODI delt inn i to generelle typer og disse blir til to komplementære teknologier, og utgjør totalt fire varianter. Type 1-varianten fokuserer på problemer mellom den nedre og den øvre dysen, mens Type 2 gjør det mellom de nedre dyser som vertikalt sett er helt under en øvre dyse.

Det vil si en Foveros-pakke og en CO-EMIB-pakke, der Intel EMIB logisk går inn. Forklaret dette går vi med de forskjellige typene mer i dybden.

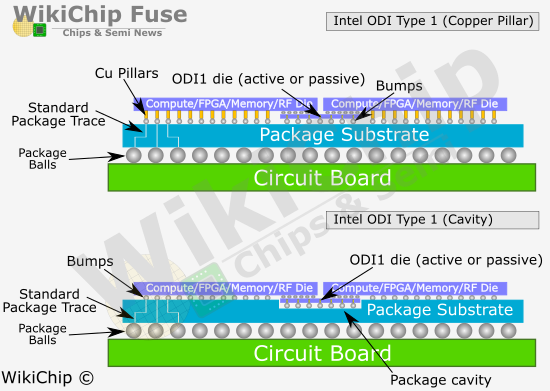

Intel ODI Type 1

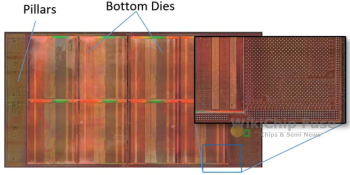

Det første vi må forestille oss er at matrisen vi skal snakke om er i forskjellige størrelser, noe som er viktig fordi måten å sammenkoble dem varierer på grunn av deres dimensjoner. Med dette i bakhodet må vi forestille oss en større dyse som er under to mindre øvre dyser, eller i det mest ekstreme tilfelle er det en større dyse som er under en annen mindre dyse som logisk nok ikke dekker hele det nedre området.

For å gi en mer eller mindre enkel likhet er det en pyramideeffekt: den nedre basen har alltid større areal enn den øvre, med forskjellen at her er det bare en matrice og på toppen kan den ha en mindre eller flere, men de blir aldri så store som den nederste.

Fordelen med dette er at Intel har designet systemet slik at bunnformen bare dekker den delen av toppstykket der det er behov for liming mellom dem. Årsaken til dette har sin logikk: du eliminerer ulempene med TSVer og beholder alle Foveros. Siden bare den delen av forbundet mellom dysene brukes, kan Intel lage en aktiv eller passiv ODI av type 1.

Dette betyr at i tilfelle av å være passiv er det bare begrenset til foreningen mellom begge dørene, men hvis den er aktiv, fungerer den som en sammenkoblingsdatasender, noe som er veldig nyttig hvis du vil legge til fra HBM stabler til ekstern cache eller en iGPU . Derfor og hvis vi går tilbake til den mentale ordningen, hvis flere dør i forskjellige størrelser blir brukt ved hjelp av ODI 1, har de alle lov til å ha tilgang til bedre varmeavledning, der IHS i noen tilfeller må være spesifikk, men tilgang oppnås. direkte til det og derfor er temperaturproblemene løst.

Dette er viktig fordi hvis vi så på begge dørene fra en toppsynsvisning, ville det bare være en del av dem som ville være koblet sammen, den essensielle, mens resten av matrisen er uavhengig og forblir i luften i hvert tilfelle, med to forskjellige høyder selvfølgelig, og det er nettopp dette som skiller det fra EMIB som teknologi.

For ikke å nevne at foreningen mellom begge dørene må gjøres med termisk komprimering, blant annet.

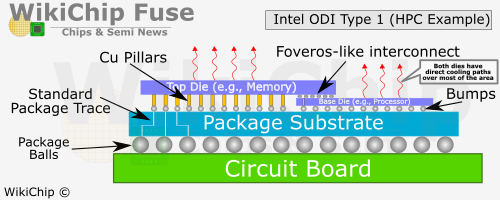

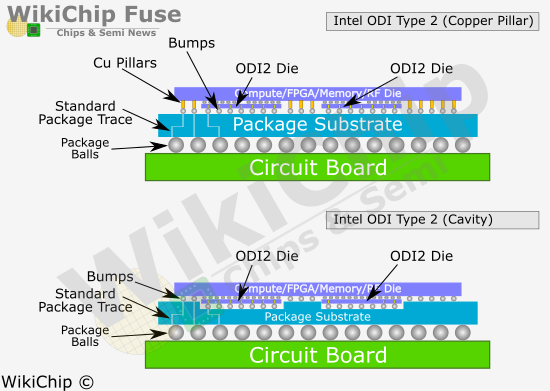

Intel ODI Type 2

Her øker problemet, siden den nedre dyse alltid er under den øvre dysen, det vil si at det ikke er noen del av matrisen som er under som stikker ut fra den som er over. Dette bringer ulempen med varme, men samtidig har den en klarere fordel: den nedre dysen kan plasseres nøyaktig der det er nødvendig sammenlignet med den øvre dysen, og antall tilkoblinger kan være mye høyere.

Denne teknologien er fokusert på å lindre ytelse og tilkoblingsproblemer mellom matriser, der overordnede ytelser alltid maksimeres, for eksempel bedre inngangs- og utgangsforbindelser, mer hastighet i hurtigbufrene, outsourcing dem uten straff og uendelig. av muligheter.

Du kan gjøre en Zen 2-stil I / O, og la cachene ligge utenfor kjernene i forskjellige matriser, lage intakte kjerner og i tre forskjellige nivåer uten tap av ytelse, fordi de er direkte koblet til hverandre gjennom fysiske fagforeninger med TSV. Fordelene med dette er så tydelige at det er absurd å til og med kommentere dem.

Her er problemet temperaturen, men med ODI Type 2 er det ment å plassere matrisen med det laveste energiforbruket i den nedre delen og å skalere vertikalt til plassering av matriser som genererer mer varme i det øvre sjiktet, for å kunne være nedkjølt med IHS, noe som gir noen virkelig fantastiske prosessor konfigurasjonsalternativer og muliggjør segregering for inkluderende effektivitet.

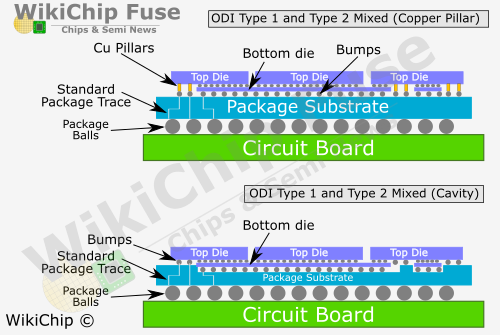

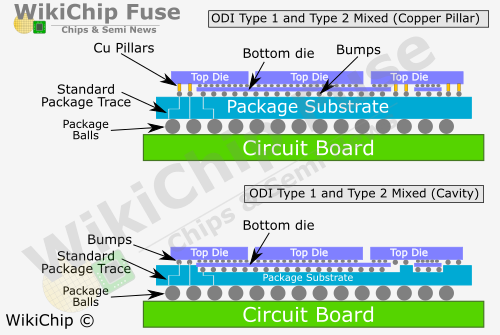

Som vi har sagt, har ODI Type 1 og Type 2 to forskjellige versjoner: Kobbersøyle og hulrom , hvor i den første en kobberpilarer ville bli brukt for å kompensere for den større høyden, mens i den andre underlaget ville støpe seg til den nedre dysen, slik at det ble brukt støt i stedet for søyler.

Intel ODI kan blande begge typene for å tilby mer komplekse prosessorer

En annen fordel med ODI som teknologi er at den ikke er eksklusiv, det vil si at begge typene kan brukes med sine to versjoner på samme CPU. derfor modularitet at vi kommer til å kunne se i fremtidens CPUer er av et slikt kaliber at kompleksiteten i designen vil være hovedutfordringen for Intel.

Det mest åpenbare spørsmålet er samtidig det mest relevante: når vil vi se disse CPUene på markedet? Et virkelig vanskelig spørsmål å svare på. Husk at ODI som teknologi bare er noen måneder gammel, den implementeres for øyeblikket og den må forbedres når det gjelder å forenkle prosessen, men Intel har våget å tilby omtrentlige datoer: 2022 eller 2023.

ODI som teknologi vil klare å forkorte fristene, siden den løser de to hovedproblemene til de tre Intel-teknologiene, slik at de første prosessorene (de trenger ikke å være til skrivebordet tydeligvis) kunne sees i produksjonen i 2024, for å være veldig optimistiske , siden Som ofte er tilfelle, slippes mindre kraftige versjoner først, og når både prosess og produksjon blir polert og forbedret, tilbys høyytelsesversjonen.

I alle fall er dette ikke science fiction, dette er en realitet, følbar, som allerede har vært på markedet med Kaby Lake G og Stratix 10 og som utvilsomt er fremtiden til prosessorer, som er en mye større revolusjon enn Multi die eller MCM på grunn av dens kompleksitet, er det definitive skrittet for å kunne pallere veggen som vi vil finne med de litografiske prosessene tilbake i 2030 og den kan uten tvil være det forrige trinnet til mer komplekse teknologier som etterlater det vi for tiden har i bleier i markedet.