Intel og AMD har kunngjort bruken av 3DIC-teknologier av alle slag for å bygge fremtidige prosessorer, en trend som vil vokse i de kommende årene. Men hvordan kunne fremtidige Intel- og AMD-prosessorer bygget med denne teknologien? I denne artikkelen vil vi prøve å belyse hvordan disse fremtidens prosessorer kan være.

Ettersom nye produksjonsnoder brukes, kan det sees hvordan kostnadene vokser mer og mer, dette tvinger ikke bare til å ta nye strategier når det gjelder design av nye prosessorer, men også nye måter å bygge dem på.

Hva forstår vi som 3DIC?

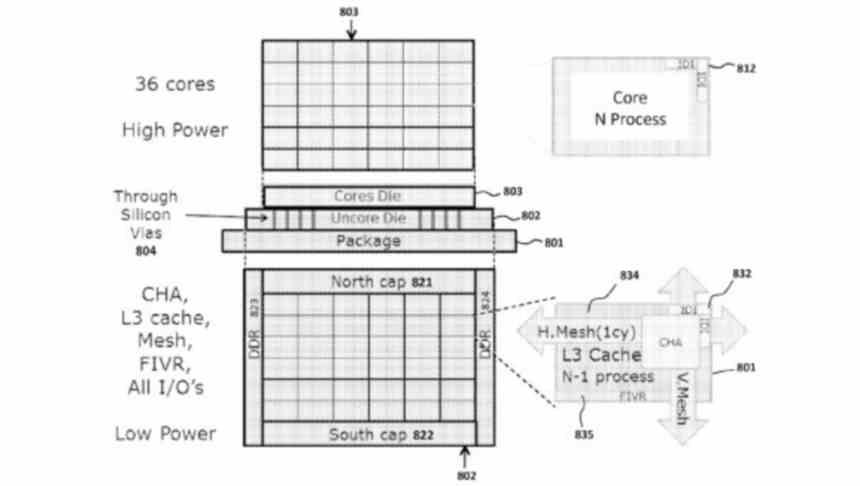

3DIC er akronymet for en tredimensjonal integrert krets, som er navnet gitt til alle prosessorer eller sett av det samme som består av flere forskjellige sjetonger som er sammenkoblet med hverandre ved hjelp av vias gjennom silisium eller TSV. Så langt i PC-maskinvarekomponentmarkedet har vi sett 3D-NAND-minnet fra forskjellige merker, så vel som de forskjellige generasjonene av HBM-minne som bare demonstrasjoner

En av fordelene med 3DIC er at vi kan bruke flere brikker med forskjellige produksjonsnoder på en kombinert måte, dette er en fordel fordi ikke alle elementene i en prosessor trenger å skaleres til en ny produksjonsnode, siden de ikke gir en høyere ytelse for dem.

Direkte dø til dø eller hvordan du bygger en kompleks prosessor ved hjelp av 3DIC

Ideen om å koble to logiske sjetonger en-til-en i en 3DIC-struktur, ved hjelp av en vertikal TSV-sammenkobling, har potensial til å forandre alle sektorer i prosessorindustrien. Fra de veldig lave SoC-ene som fungerer som den sentrale prosessoren i telefonen din til high-end sjetonger som er spesialisert i datasentre.

Ideen om å skille en prosessor i to eller flere vertikalt justerte deler er noe vi allerede har sett i Intel Lakefield, der prosessor kjerner og Northbridge er skilt fra Southbridge på forskjellige chips og bruker produksjonsnoder. forskjellig. Men vi bør begynne å se på noen modeller av SoC og til og med CPUer.

Men Intel-arkitektur er ikke den eneste måten å bygge en moderne CPU ved hjelp av 3DIC-teknologi, men det er også en annen type konfigurasjon der CPU-kjernene og "uncore" av den samme prosessoren er skilt i to eller flere forskjellige brikker sammenkoblet via TSV.

Den største utfordringen CPU-arkitekter for øyeblikket står overfor er energikostnadene ved dataoverføring i prosessoren, som i en konfigurasjon vi snakker om er sterkt redusert, og dermed blir 3DIC ikke bare fremtidens innsats for Intel og AMD, men det er også noe vi skal se i ARM verden.

En mulig fremtidig 3DIC-prosessor av Intel eller AMD

For vårt eksempel vil vi ta et eksempel på stasjonære prosessorer basert på Zen 2 og Zen 3, som deler kjernene til uncore, et element som også er kjent som Northbridge, selv om AMD kaller det Scalable Data Fabric. Vi skal bruke denne arkitekturen fordi den har en veldig klar inndeling av komponentene.

AMD, eller Intel, kan gi ut en fremtidig prosessor der vi tilsynelatende ser en monolitisk konfigurasjon, men egentlig for å være en 3DIC-prosessor der uncore er på en annen chip i bunken enn de forskjellige kjernene.

Dette vil bety at tilkoblingen mellom CCD og Chiplets med SDF ikke bare vil være mer direkte og derfor med mindre ventetid, men også forbruke mindre, takket være det faktum at det ville være mulig for AMD eller Intel å bruke et større antall pinner med lavere hastighet, men uten å miste båndbredde for å kommunisere de forskjellige kjernene med resten av prosessoren, som igjen vil tillate å øke ytelsen pr. watt for de forskjellige CPUene betraktelig.

Ideen om å skille prosessorene i flere nivåer vil tillate ting som å bygge flerkjernesystemer som går utover åtte kjerner på samme brikke og kommunisere alle sammen med tilstrekkelig hastighet, med god ventetid og forbruker veldig lite energi sammenlignet med dagens modeller.

Hvilke handicap får Intel og AMD når de distribuerer 3DIC?

Den største avveien er de enorme kostnadene ved å lage en 3DIC-prosessor, som krever ytterligere produksjonstrinn, men den største avveien er det som kalles termisk stalling, som oppstår når to komponenter er så nær at temperaturen på en. det påvirker ytelsen til en annen, og lar ikke komponentene nå klokkehastighetene de kan oppnå separat og til og med i en 3DIC-konfigurasjon.

Dette gjør at disse konfigurasjonene også krever mye mer komplekse og dyre kjølesystemer, som til sammen tar dem bort fra hjemmesystemer og gjør dem ideelle for servere av alle slag, men paradoksalt nok er de også fremtiden for SoCs for PostPC-enheter. De er begrenset i størrelse og kan ikke utvide seg mer horisontalt, så de kan bare gjøre det vertikalt.

Årsaken til dette er at med hver ny node øker ikke bare kostnaden for hver oblatmillimeter i kvadrat, men det blir også stadig vanskeligere å bygge større og større prosessorer uten en farlig feilrate. Alt dette vil tvinge de fleste design til å gå fra å være en enorm monolitisk chip til å bestå av flere vertikale chips, bare fordi kostnaden per wafer vil være så høy at selv de høye kostnadene ved 3DIC-produksjon ikke vil være en hindring.