Terwijl chipknooppunttechnologieën en Wet van Moore zijn volledig en schijnbaar vertraagd, chipfabrikanten en ontwerpers blijven zoeken naar creatieve nieuwe oplossingen om de schaalbaarheid van apparaten mogelijk te maken en de prestaties te blijven verbeteren. Geavanceerde inkapselingstechnologieën zijn een van die gebieden die we hebben gezien geweldige innovaties in de afgelopen jaren, zoals de introductie van silicium tussenpersonen , de integratie van HBM-geheugen op de chip zelf, of de verschuiving naar modularisatie met chiplets. Vandaag gaan we het er met je over hebben TSMC's LSI-technologie , waarmee ze in de toekomst hun chips willen bouwen en die de manier waarop deze industrie werkt, ten goede kunnen veranderen.

Silicium tussenstukken kostenuitdagingen omdat ze erg duur zijn en een vrij grote hoeveelheid silicium vereisen, terwijl chipletontwerpen die conventionele verpakkingen op organische substraten gebruiken, worden beperkt door input / output-bandbreedte en energie-efficiëntie. Een oplossing voor dit probleem was de introductie in de industrie van tussenliggende siliciummatrices die twee logica-chips met elkaar verbinden, maar alleen in een beperkte reikwijdte en zonder dezelfde footprint te gebruiken als een volledige silicium tussenlaag. Intelis EMIB (Embedded Die Interconnect Bridge) is de laatste tijd de meest besproken implementatie van deze technologie.

TMSC LSI, wordt het de toekomst van de industriechips?

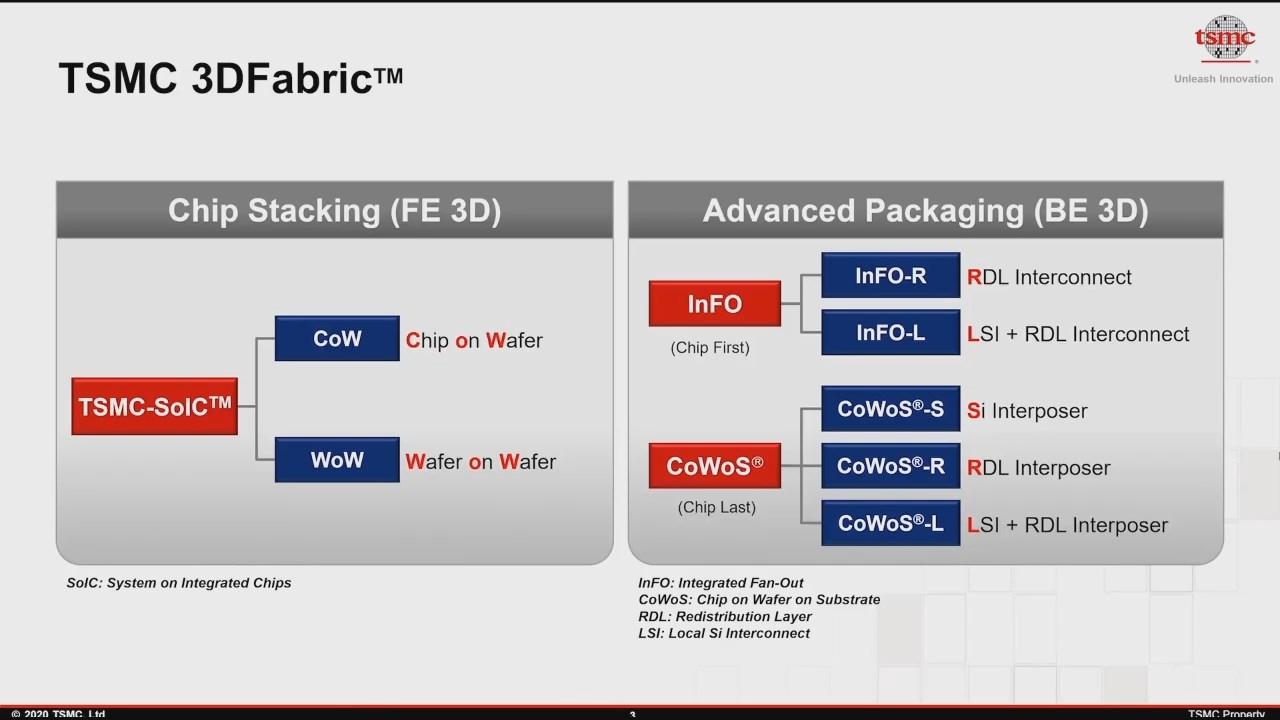

Tijdens TSMC's 2020 Technology Symposium heeft de Taiwanese fabrikant zijn eigen variant van dergelijke technologie uitgewerkt, genaamd Local Si Interconnect (LSI), die zal worden aangeboden voor InFO- en CoWoS-inkapselingstechnologieën in de vorm van InFO-L en CoWoS-L.

De nieuwe verbeteringen maken deel uit van wat TSMC nu zijn 3D stof verpakkingstechnologie, die een vrij veelzijdig repertoire van inkapselings- en integratie-opties biedt, waaronder natuurlijk SoIC, InFO en CoWoS.

Een korte uitleg voor onze lezers die niet bekend zijn met deze termen: SoIC (System on Chip Integrated) is TSMC's hybride bonding- en chipstacking-integratietechnologie, waarmee meerdere chip-arrays op elkaar kunnen worden gestapeld, waardoor de bandbreedte extreem hoog is en een overgang heeft tussen matrijzen van laag verbruik silicium. Momenteel is deze technologie ongeëvenaard in de branche.

InFO is TSMC's ventilatorverpakkings- of inkapselingstechnologie, waarbij een matrijs van een siliciumwafel wordt verwijderd en op een andere dragerwafel wordt geplaatst, waarop grotere structuren zoals koperen RDL worden gebouwd. (herverdelingslaag) en vervolgens het dragersubstraat.

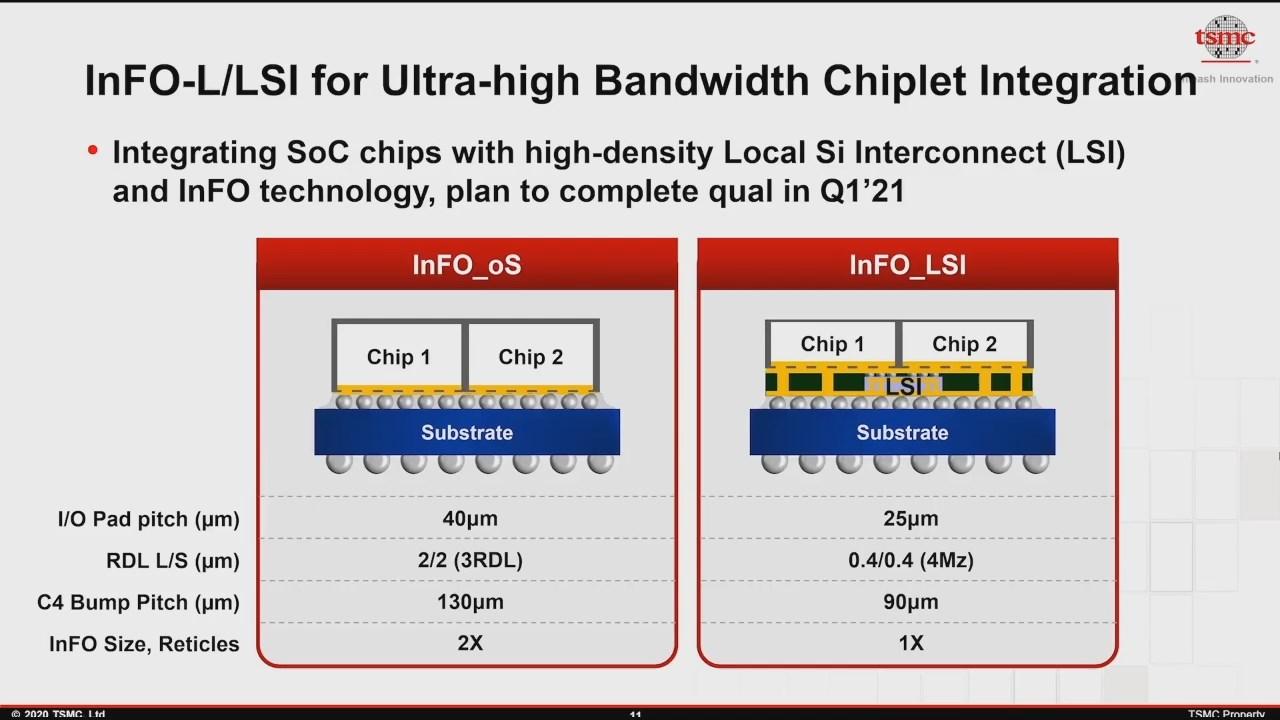

De TSMC-variant van InFO met LSI-integratie wordt InFO-L of InFO-LSI genoemd en volgt een vergelijkbare structuur met de nieuwe toevoeging van deze lokale silicium interconnect-tussenchip voor communicatie tussen beide chips.

TSMC's CoWoS (Chip-on-Wafer-on-Substrate) werd oorspronkelijk beschreven als de 2.5D silicium interposer-verpakkingstechnologie van het bedrijf, die momenteel nog steeds onder de CoWoS-S-specificatie valt, maar ondertussen ook andere inkapselingstechnologieën omvat. Zoals de beschrijving zegt, wordt de RDL eerst op het basissubstraat gebouwd en pas als laatste stap wordt de siliciumchip aan de set toegevoegd.

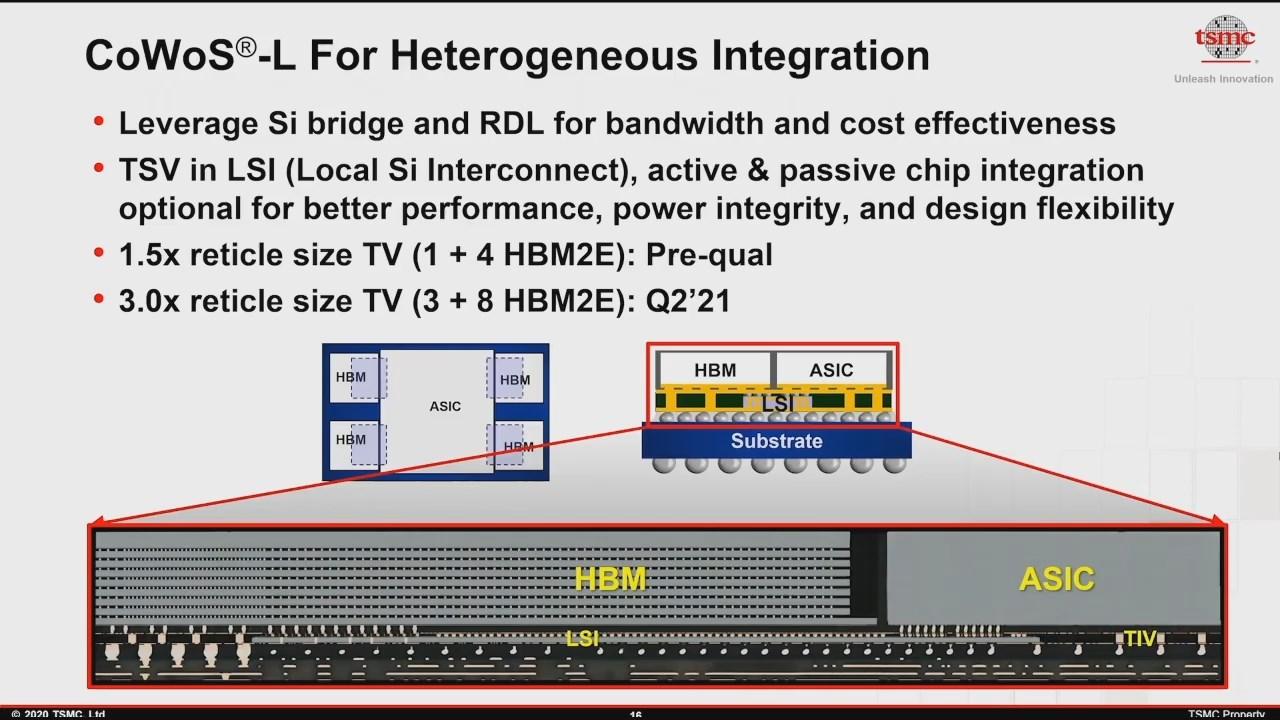

CoWoS-L is de nieuwe variant van TSMC's chipverpakkingstechnologie, waarbij lokale siliciumverbinding wordt toegevoegd die wordt gebruikt in combinatie met een koperen RDL om een hogere bandbreedte te bereiken dan bij het gebruik van een RDL-verpakkingsimplementatie. (CoWoS-R), en heeft ook lagere kosten dan wanneer een volledige silicium interposer (CoWoS-S) zou worden gebruikt. Met andere woorden, met deze inkapselingstechnologie krijgt u betere prestaties tegen lagere kosten .

TSMC beschrijft LSI als een actieve of passieve chip (afhankelijk van de behoeften van de chipontwerpers en hun budget). De TSMC-smelter verwacht de InFO-L-kwalificatie in het eerste kwartaal van 2021 af te ronden, terwijl CoWoS-L momenteel in een prekwalificatieproces zit. Silicon bridge interconnect-technologieën zoals LSI en EMIB zullen naar verwachting hoogwaardige chipontwerpen opleveren tegen lagere kosten voor zowel de ontwerper als de consument.

Kortom: chips met hogere prestaties en goedkoper, iets dat (voor de gebruiker) moet vertalen naar krachtigere en goedkopere processors .