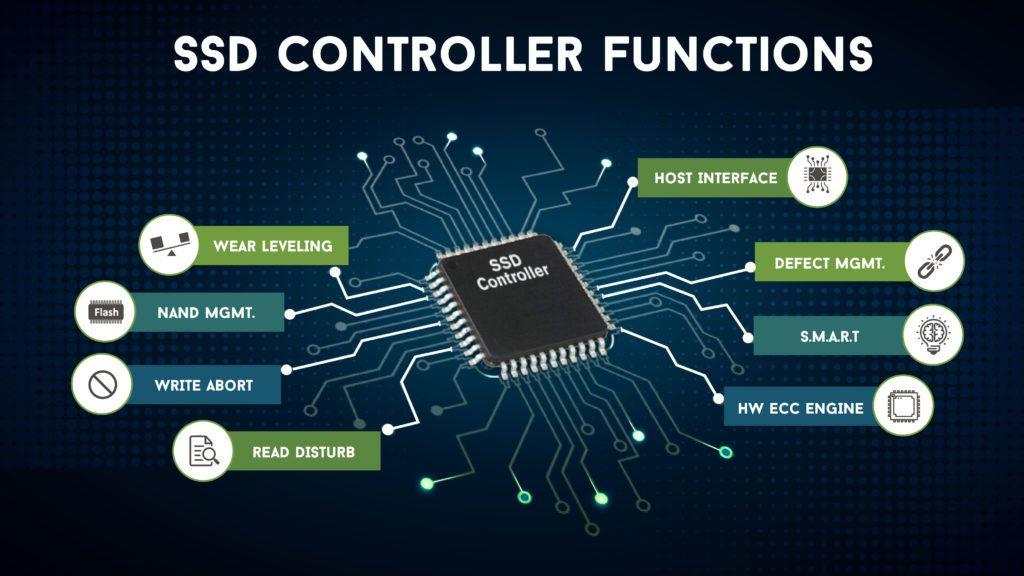

Je hebt vast wel gehoord of gelezen over de ECC-foutcorrectiecode in veel hardwarecomponenten, allemaal gerelateerd aan geheugen (ofwel RAM of opslag), hoewel zeer weinigen het belang ervan inzien. Om deze reden gaan we in dit artikel uitleggen hoe het ECC werkt in een SSD controleur , en hoe dankzij het mogelijk is om de levensduur te verlengen en een groot verschil te maken in de levensduur van SSD's .

Elk apparaat dat NAND Flash-geheugen gebruikt, heeft een willekeurige bitfoutcorrectiecode nodig (bekend als een "zachte" fout). Dit komt omdat veel elektrische ruis wordt geproduceerd in een NAND-chip en de signaalniveaus van de bits die door een reeks NAND-chips gaan, zijn erg zwak.

Een van de manieren waarop NAND-geheugen geworden de goedkoopste dit komt vooral omdat het vereist dat foutcorrectie wordt uitgevoerd vanaf een element buiten de NAND-chip zelf; In het geval van SSD's, de ECC wordt uitgevoerd op de controller .

Hoe de ECC werkt op een SSD-controller

Deze zelfde foutcorrectie helpt ook bij het corrigeren van bitfouten als gevolg van slijtage aan de geheugen cellen zelf . Uitputting kan ervoor zorgen dat bits in een of andere staat "vastlopen" (bekend als een "harde" fout of harde fout) en kan de frequentie van "zachte" fouten verhogen.

Hoewel het geen overdreven breed concept is, is de flash-geheugenweerstand een maat voor hoeveel wis- / schrijfcycli een flitsblok kan weerstaan voordat er "harde" fouten optreden. Heel vaak zijn deze fouten alleen in individuele bits en het komt zeer zelden voor dat het hele blok faalt. Met een voldoende hoog wis / schrijfnummer, neemt het "zachte" foutenpercentage ook toe door een aantal andere mechanismen in de SSD zelf.

If ECC kan zijn gebruikt om deze "harde" fouten te corrigeren en de "zachte" fouten niet te vergroten, wordt de levensduur van het gehele blok aanzienlijk verlengd, ver voorbij de weerstand die door de fabrikant is gespecificeerd.

Laten we een voorbeeld nemen: laten we zeggen dat een ongebruikte NAND-chip voldoende "zachte" fouten heeft om 8 bits ECC te vereisen, dat wil zeggen dat elke gelezen pagina maximaal 8 bits kan bevatten die willekeurig zijn beschadigd (meestal vanwege de elektrische ruis die we we praten over). aanvankelijk). De ECC die in deze chip wordt gebruikt, kan 12-bits fouten corrigeren, zodat de ECC kon dit probleem niet oplossen we zouden 8 "zachte" fouten moeten vinden in verband met elektrische ruis plus nog eens 5 "zachte" als gevolg van slijtage.

Nu garanderen fabrikanten van flash-geheugen dat de eerste van die 5 storingen ergens na de sterkte-specificatie van de SSD zal optreden. Dit betekent dat geen enkele bit zal falen door slijtage totdat de door de fabrikant gespecificeerde wis- / schrijfcycli worden overschreden. Houd er nu rekening mee dat de specificaties niet nauwkeurig genoeg zijn om te voorspellen wanneer het volgende bit zal mislukken, en het kan enkele duizenden wis- / schrijfcycli boven de specificatie duren voordat dit kan gebeuren; onthoud dat de fabrikant garandeert dat het niet zal gebeuren vóór X cycli, maar niet wanneer het zal gebeuren zodra ze worden overschreden.

Dit betekent dat het lang kan duren een blok wordt zo corrupt dat het uit dienst moet worden genomen (en ook hiervoor heeft de SSD meestal "extra" blokken om de corrupte te vervangen), wat op zijn beurt betekent dat de weerstand van de fout gecorrigeerd blok kan vele malen groter zijn dan de gespecificeerde weerstand, afhankelijk van het aantal overtollige fouten dat de ECC moet corrigeren.

Welke impact heeft de foutcorrectiecode op een SSD?

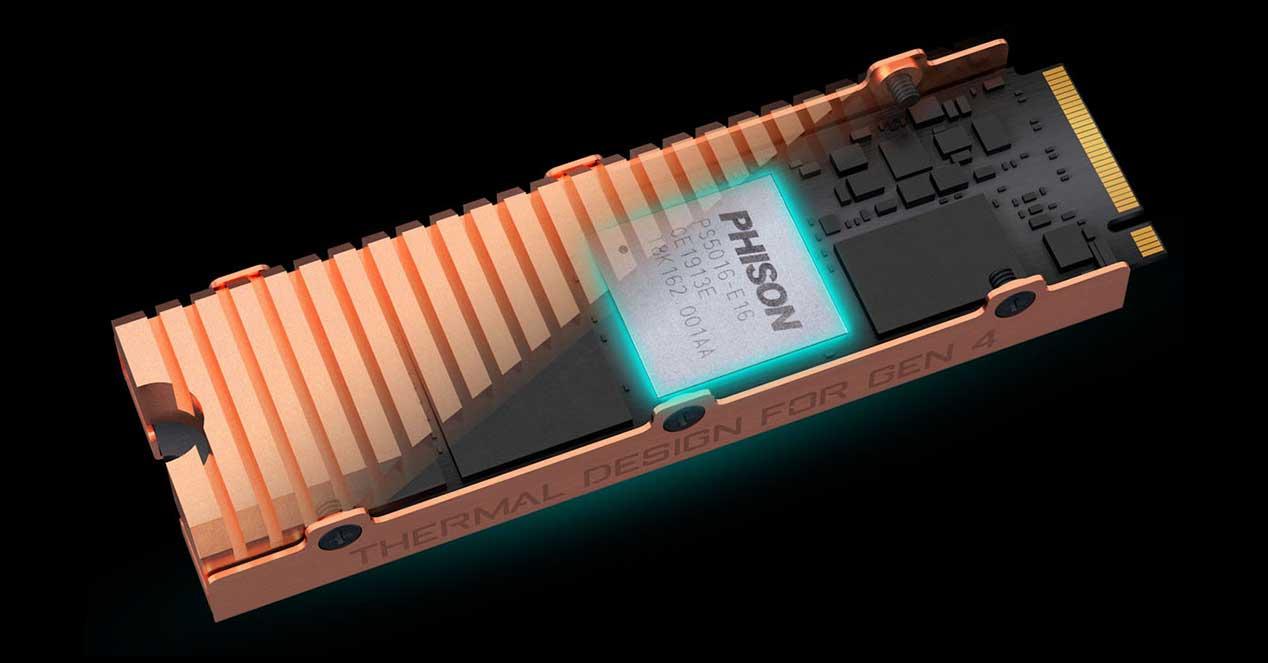

Zoals we eerder hebben uitgelegd, is flash-geheugen zo goedkoop omdat het de ECC niet in de chips zelf bevat, maar is geïntegreerd in andere hardware die daarbuiten is, en zoals je zult veronderstellen heeft dit een prijs. Een meer geavanceerde ECC vereist meer rekenkracht op de controller en kan langzamer zijn als de algoritmen niet erg modern zijn. Ook hangt het aantal fouten dat kan worden gecorrigeerd af van hoe groot de geheugensector wordt gecorrigeerd, dus een SSD-controller met een geavanceerd ECC-algoritme zal waarschijnlijk veel bronnen gebruiken, vermindering algehele SSD prestatie . Deze verbeteringen maken ook de controller duurder .

ECC-algoritmen hebben hun eigen wiskundige toestand, afhankelijk van de controller (met andere woorden, er is geen standaard), en zelfs de meest elementaire ECC-coderingen (Reed-Solomon en LDPC) zijn behoorlijk ingewikkeld om te begrijpen. Wanneer iemand het heeft over de Shannon-limiet (het maximale aantal bits dat kan worden gecorrigeerd), is het een hoeveelheid die, zoals je niet weet van de fabrikant in de technische specificaties, uiterst moeilijk te berekenen is.

Blijf er gewoon bij: meer correctiebits leiden tot een langere levensduur van de SSD, maar het heeft ook enige invloed op de prestaties of zelfs de productprijs door een krachtigere controller nodig te hebben.