Als we kijken naar de specificaties van een processor, valt een van de dingen op die het cachegeheugen hebben, dat niet alleen op alle CPU's, maar ook op alle GPU's terug te vinden is. In dit artikel leggen we uit wat cachegeheugen is in duidelijke en toegankelijke taal, zodat je weet waar dit type geheugen op je pc voor is.

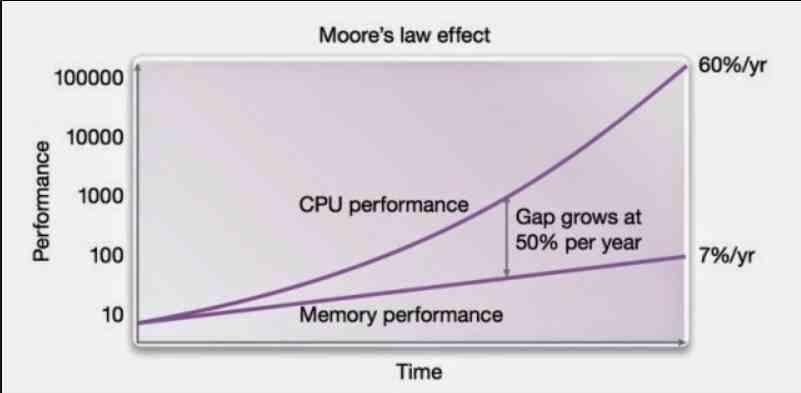

Cachegeheugen werd voor het eerst geïmplementeerd in het Intel 80486, maar de oorsprong ervan gaat terug tot de IBM S / 360, waar het idee van cachegeheugen voor het eerst werd geïmplementeerd. Vandaag vanwege de kloof tussen de CPU, GPU en andere processors met geheugen, is het een onmisbaar onderdeel geworden van elke processor.

Waarom is de cache nodig?

Cachegeheugen is nodig vanwege het feit dat RAM geheugen is te traag voor een CPU om zijn instructies met voldoende snelheid uit te voeren en we kunnen het niet meer versnellen. De oplossing? Voeg een intern geheugen goed toe in de processor waarmee je inzoomt op de laatste data en instructies.

Het probleem is dat dit buitengewoon complex is, omdat het de programma's zelf dwingt om het te doen, waardoor CPU-cycli worden verlengd. De oplossing? Creëer een geheugen met een mechanisme dat de gegevens en instructies kopieert die het dichtst in de buurt komen van wat momenteel wordt uitgevoerd.

Omdat de cache zich in de processor bevindt, voert de CPU deze, zodra hij de gegevens erin vindt, veel sneller uit dan wanneer hij natuurlijke toegang tot RAM had.

Hoe werkt de cache?

Allereerst moeten we in gedachten houden dat de cache geen deel uitmaakt van het RAM-geheugen en ook niet als zodanig werkt, bovendien kan het niet worden bestuurd als RAM, waar programma's geheugen kunnen innemen en vrijmaken wanneer ze het nodig hebben . De reden? Cache werkt volledig gescheiden van RAM.

De taak van de cache is om de gegevens van het geheugen naar de processor te verplaatsen. Het gebruikelijke in een programma is dat de code in volgorde wordt uitgevoerd, dat wil zeggen dat als de huidige instructie in regel 1000 staat, de volgende in 1001 staat, tenzij het een springinstructie is. Het idee van caches? Breng een deel van de gegevens en instructies over naar een intern geheugen van de processor.

Wanneer de CPU of GPU naar gegevens of een instructie zoekt, kijkt hij eerst naar de cache die zich het dichtst bij de processor bevindt en dus naar degene met het laagste niveau om te verhogen totdat de verwachte gegevens zijn bereikt. Het idee is dat u geen toegang hoeft te hebben tot het geheugen.

Cacheniveaus op CPU en GPU

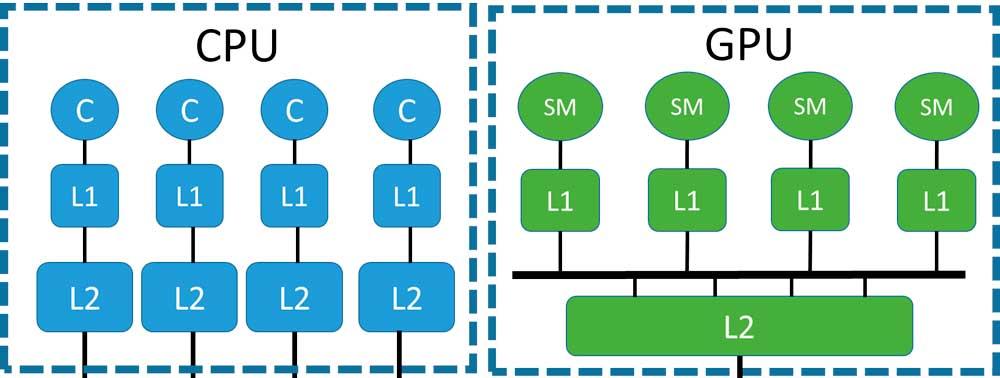

In een multicore-systeem waar we twee of meer kernen hebben, merken we dat ze allemaal goed toegang hebben tot hetzelfde RAM-geheugen, dat er een enkele interface is voor geheugen en dat verschillende processors vechten om toegang ertoe. Op dit punt is het nodig om een extra cacheniveau te creëren, dat communiceert met de geheugencontroller en dit met de hogere cacheniveaus.

Normaal gesproken hebben multicore-CPU's meestal twee cacheniveaus, maar in sommige ontwerpen hebben we clusters, die zijn gebaseerd op groepen van verschillende CPU's met een gedeelde L2-cache, maar die de ruimte delen met andere clusters, wat soms de opname van een cache op het derde niveau.

Hoewel niet gebruikelijk, verschijnen caches van niveau 3 zodra de geheugeninterface een voldoende groot knelpunt is dat het toevoegen van een extra niveau in de hiërarchie de prestaties ten goede komt.

De geheugenhiërarchie

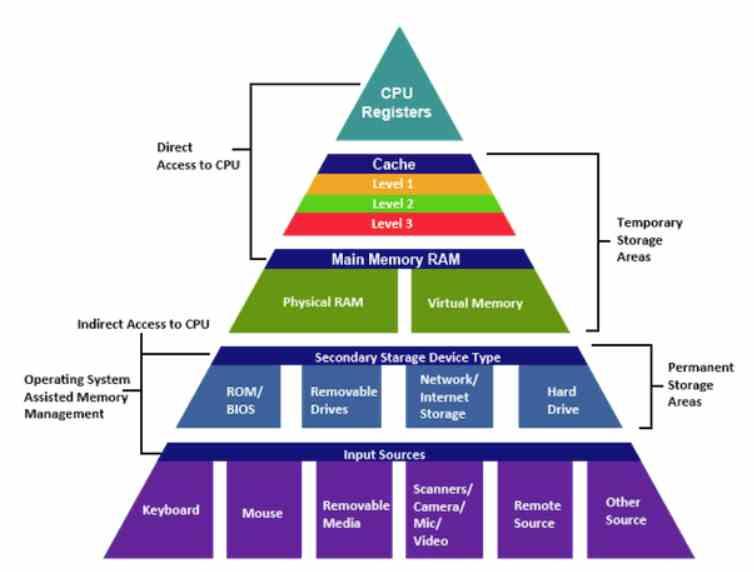

De regels van de geheugenhiërarchie zijn heel duidelijk, het begint bij de processorregisters en eindigt in het langzaamste geheugen daarvan en volgt altijd dezelfde regels:

- Het huidige niveau van de hiërarchie heeft meer capaciteit dan het vorige, maar minder dan het volgende.

- Als we weggaan van de CPU, neemt de latentie van de instructies toe.

- Als we weggaan van de CPU, neemt de bandbreedte met de gegevens af.

In het specifieke geval van cacheniveaus slaan ze steeds kleinere stukjes informatie op, maar bevatten ze altijd een fragment van het volgende niveau. De L1-cache is dus een subset van de L2-cachegegevens die op zijn beurt een superset is van de L1-cachegegevens en een subset van de L3-cachegegevens, indien aanwezig.

De cache van het laatste niveau, de cache die zich het dichtst bij het geheugen bevindt, is echter geen subset van RAM, maar slechts een kopie van de geheugenpagina of set daarvan die zich het dichtst bij de processor bevindt.

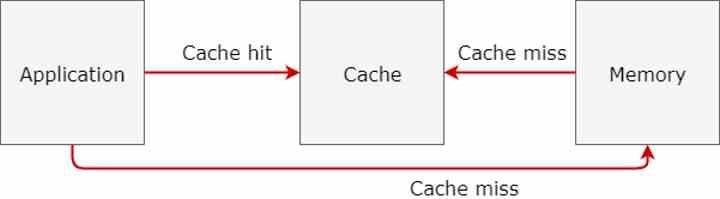

Cache Miss of wanneer gegevens niet worden gevonden

Een van de grootste prestatieproblemen is wanneer er een Miss Cache optreedt die optreedt wanneer gegevens niet op cacheniveau worden gevonden. Dit is buitengewoon gevaarlijk voor de prestaties van een defecte CPU, aangezien het gevolg is dat veel processorcycli verloren gaan, maar het is niet minder gevaarlijk voor een defecte CPU.

Voor het ontwerp van een CPU is het feit dat de som van de zoektijd van alle Cache Miss gecombineerd met de zoektijd groter is dan het zoeken naar de gegevens rechtstreeks in de cache, een mislukking. Veel CPU-ontwerpen moesten terug naar de ontwerptabel vanwege het feit dat de zoektijd langer is dan de toegang tot RAM.

Dat is de reden waarom architecten erg terughoudend zijn om extra niveaus in een architectuur toe te voegen, want ja, het moet worden gerechtvaardigd in het licht van verbeterde prestaties.

Samenhang met geheugen

Omdat de cache kopieën van gegevens uit de RAM heeft, maar het is niet de RAM zelf, bestaat het gevaar dat de gegevens niet overeenkomen, niet alleen tussen de cache en de RAM, maar ook tussen de verschillende cache-niveaus, waarvan sommige gescheiden zijn. .

Daarom zijn mechanismen nodig die verantwoordelijk zijn voor het handhaven van de samenhang van de gegevens op alle niveaus met elkaar. Iets dat veronderstelt de implementatie van een uiterst complex systeem dat toeneemt met het aantal processorkernen.