PCI Express 기술은 그래픽 카드 및 NVMe SSD와 같은 기타 주변 장치를 연결하는 데 오랫동안 사용되어 왔습니다. XNUMX세대 인터페이스의 구현은 Alder Lake 프로세서의 도착과 함께 발생합니다. 인텔 그리고 Zen 4 프로세서는 AMD. 그러나 PCI Express 6.0 사양이 완성되었으며 XNUMX세대에 비해 몇 가지 개선 사항이 있습니다.

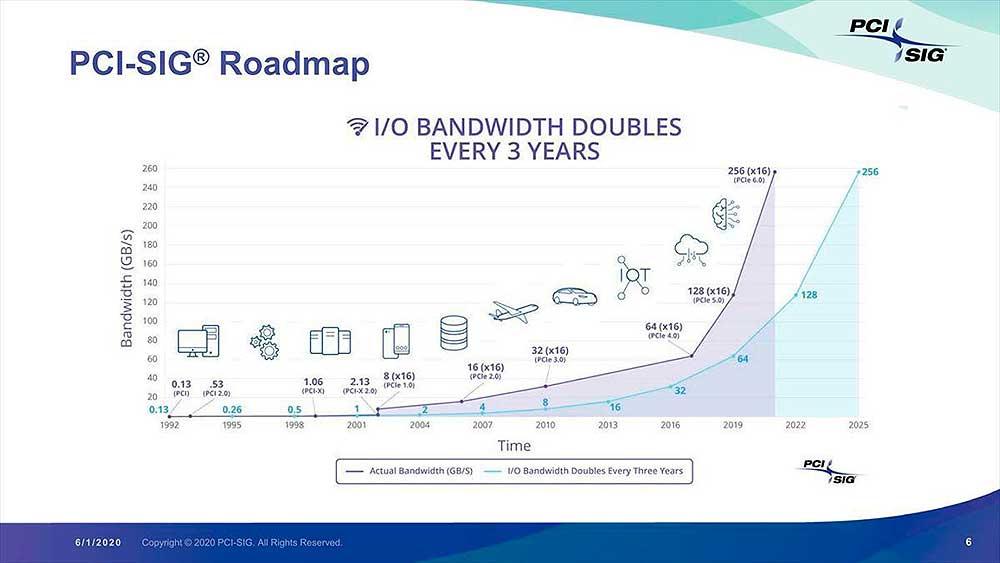

PCI Express 6.0은 처음부터 이 인터페이스의 이전 세대와 동일한 개선 사항을 따릅니다. 즉, 이전 세대에 비해 두 배의 대역폭을 기반으로 합니다. 그러나 PCI Express 6.0의 경우 이 인터페이스의 XNUMX세대 개발에 큰 변화가 필요했습니다.

PCI Express 6.0의 대역폭은 128라인 인터페이스의 경우 16GB/s, I/O 인터페이스의 경우 지나치게 높은 대역폭으로 현재 그래픽에 사용하고 있는 현재 PCI Express 4.0에 비해 XNUMX배나 뛰어납니다. 카드. 점프는 또한 NVMe에서 점프를 의미합니다. SSD PCI Express 7을 사용하는 8-28GB/s ~ 32-6.0GB/s의 플래시 컨트롤러.

하위 호환성 및 신호 불안정성 문제

PCI Express 인터페이스는 항상 이전 버전의 프로토콜과 역호환되었습니다. 즉, PCI Express 1.0 카드를 PCI Express 6.0 슬롯에 연결할 수 있으며 pinage가 정확히 동일하기 때문에 작동합니다. 따라서 속도를 높이지 않고 대역폭을 늘리기 위해 핀 수를 늘릴 수 없습니다. 해결책? 인터페이스가 작동하는 클럭 속도를 높입니다.

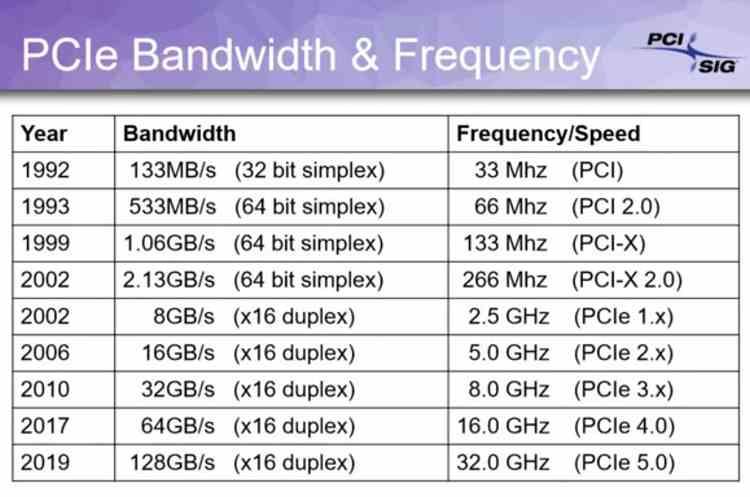

PCI Express 6.0에 문제가 있습니까? 인터페이스의 클럭 속도를 높이면 거리에 따라 더 불안정해지며 64세대 이후에는 인터페이스가 기존 방식으로 작동하는 고속으로 인해 인터페이스를 변경해야 했습니다. 그리고 이 줄과 함께 제공되는 표를 보면 XNUMXGHz의 이론적인 속도에 대해 이야기하고 있으며, 이는 짧은 거리에서도 양쪽 끝이 PCI Express 인터페이스에 있는 경우에도 신호를 충분히 변형시킵니다.

이로 인해 PCI Express 6.0으로의 도약을 가능하게 하기 위해 일련의 조치가 취해졌습니다.

PCI Express 6.0의 첫 번째 개선 사항, PAM4 사용

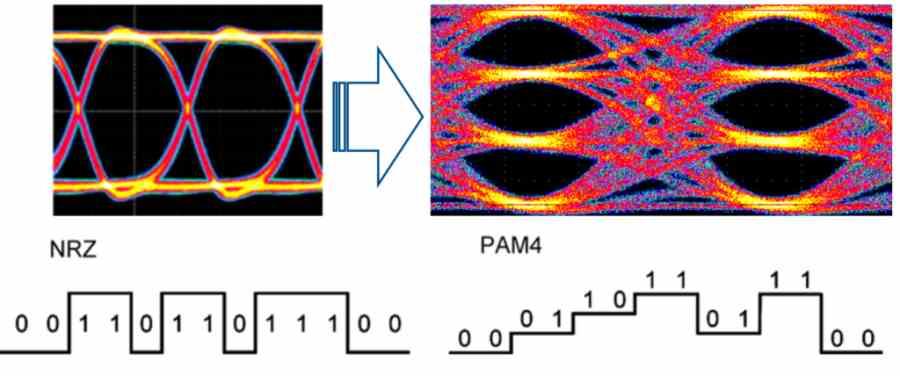

칩의 외부 또는 내부 인터페이스는 값이 1인지 0인지 어떻게 알 수 있습니까? 정보가 전송되는 전압에 따라 간단합니다. 바이너리 시스템은 전압 강하 또는 상승이 신호를 혼동하지 않도록 두 전압 사이에 충분한 거리를 두고 사용하는 것을 기반으로 합니다. 아날로그 시스템에서 전압의 단순한 변화는 정보의 변화를 가정합니다. 이러한 이유로 컴퓨터는 이진법으로 말합니다.

이것이 PCI Express 6.0과 어떤 관련이 있습니까? 신호가 왜곡되고 이전 버전과의 호환성을 위한 핀 수도 없기 때문에 대역폭을 늘릴 수 없기 때문에 솔루션을 찾아야 하며 이는 PAM4 인코딩 또는 펄스 진폭 변조의 사용을 통해 진행됩니다. 6개의 전압 값을 사용하는 것이 아니라 각 핀에 대해 4개의 전압 값을 사용합니다. 이런 식으로 각 핀의 값 00, 01, 10 및 11을 인코딩할 수 있습니다. 0 또는 1인 두 개의 기본 값 대신 총 XNUMX개의 값.

이 솔루션은 대역폭과 핀을 늘리는 것을 방지하지만 PCI Express 7.0에서는 더 이상 기존 방법으로는 불가능할 것이라고 말합니다. 우리는 포토닉스와 광학 인터페이스의 사용을 볼 수 있지만 PCI Express 6.0의 개선으로 오븐에서 갓 나온 것이므로 후속 제품에 대해 인내심을 갖는 것이 좋습니다.

패키지 시스템의 변화

PAM-4로의 점프는 PCI Express 6.0 인터페이스가 기존 PAM-2 또는 NRZ 모드에서 통신하여 이전 세대와 호환된다는 사실에도 불구하고 패킷을 보내는 방식을 변경했습니다. PAM-4 형식은 기존 패킷 시스템을 지원하지 않아 통신 프로토콜이 변경된 것이 현실이다.

첫 번째 변경 사항은 데이터 전송 오류를 수정하기 위한 새로운 프로토콜인 소위 정방향 오류 수정(FEC)입니다. 문제는 처리할 대역폭이 너무 높아 FEC가 데이터를 보낼 때 엄청난 대기 시간을 추가한다는 것입니다. 이를 완화하기 위해 PCI Express 6.0 표준은 FLIT라는 패키지 유형을 사용합니다. 패킷은 특정 목적지가 있는 비트 집합에 불과합니다. 각 FLIT의 전송 대기 시간은? 인터페이스의 라인 수에 따라 다르지만 각 패킷의 대기 시간은 2라인 PCI Express 16에서 6.0ns에 불과하지만 단일 라인 인터페이스에서는 최대 32ns입니다.

FEC는 고정된 크기에서만 작동하므로 FLIT의 크기는 전송당 256바이트입니다. 각 패킷 또는 TLP는 0바이트에서 4096바이트 사이의 크기를 가질 수 있으므로 각 패킷은 여러 FLITS로 구성될 수 있습니다.

PCI Express 6.0으로 세 번째 업그레이드, 가변 소비

PCI Express 6.0은 L0P라는 새로운 저전력 상태를 추가합니다. 이 모드를 사용하면 전송 중인 데이터 흐름이 인터페이스에서 전송할 수 있는 것보다 낮을 때 인터페이스에서 전력 소비를 줄일 수 있습니다. 이를 위해 데이터 전송의 특정 순간에 인터페이스가 작동하는 클럭 속도가 달라집니다. 모두 데이터 전송에 대기 시간을 추가하는 중단을 일으키지 않습니다.

문제는 이 메커니즘이 FLITS 및 FEC 및 PAM4와 연관되어 있다는 것입니다. 즉, PCI Express 6.0 모드에서만 사용할 수 있고 다른 모드에서는 사용할 수 없습니다.