チップ製造ノード技術と ムーアの法則 完全に明らかに減速しているため、チップメーカーと設計者は、デバイスのスケーリングとパフォーマンスを継続的に向上させるための創造的な新しいソリューションを探し続けています。 高度なカプセル化技術は、私たちが目にした分野のXNUMXつです。 素晴らしいイノベーション 近年、シリコンの導入など インターポーザー 、チップ自体へのHBMメモリの統合、またはチップレットによるモジュール化への移行。 今日はあなたに話します TSMCのLSIテクノロジー 、将来的にチップを構築する予定であり、この業界の仕組みをより良く変えることができます。

シリコンインターポーザー 有機基板上に従来のパッケージを使用するチップレット設計は、入力/出力帯域幅とエネルギー効率によって制限される一方で、非常に高価でかなり大量のシリコンを必要とするため、コストの問題が発生します。 この問題のXNUMXつの解決策は、XNUMXつの論理チップを相互に接続する中間シリコンマトリックスの業界への導入でしたが、範囲が限定されており、完全なシリコンインターポーザーと同じフットプリントを使用していません。 インテルのEMIB (Embedded Die Interconnect Bridge)は、このテクノロジーの実装について最近最も話題になっています。

TMSC LSI、それは業界チップの未来になるのでしょうか?

TSMCの2020年技術シンポジウムで、台湾の製造業者は、ローカルSi相互接続(LSI)と呼ばれるそのような技術の独自の変種について詳しく説明しました。これは、InFO-LおよびCoWoS-Lの形式でInFOおよびCoWoSカプセル化技術に提供されます。

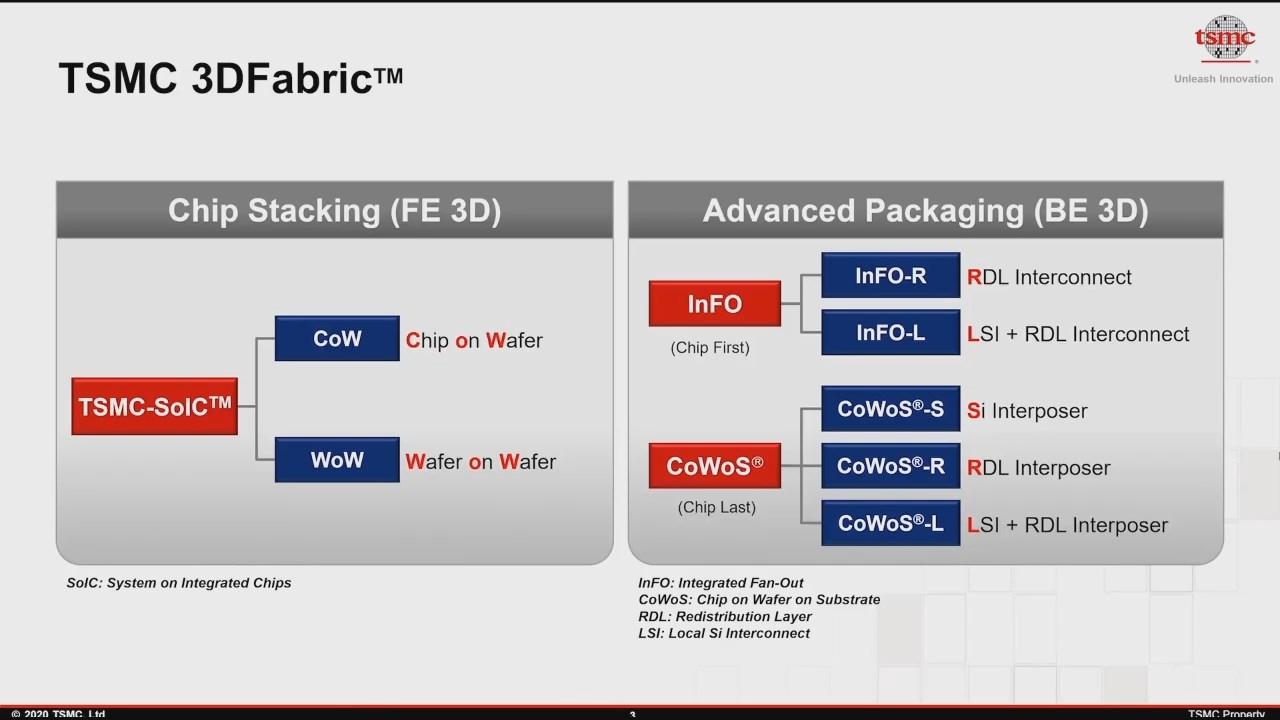

新しい進歩は、TSMCが現在そのと呼んでいるものの一部です 3Dファブリック パッケージングテクノロジー。もちろん、SoIC、InFO、CoWoSなど、カプセル化と統合のオプションのかなり用途の広いレパートリーを提供します。

これらの用語に精通していない読者のための簡単な説明: SoIC (System on Chip Integrated)は、TSMCのハイブリッドボンディングおよびチップスタッキング統合テクノロジーであり、複数のチップアレイを積み重ねることができるため、帯域幅が非常に広くなり、低消費シリコンのダイ間に接合部があります。 現在、このテクノロジーは業界で比類のないものです。

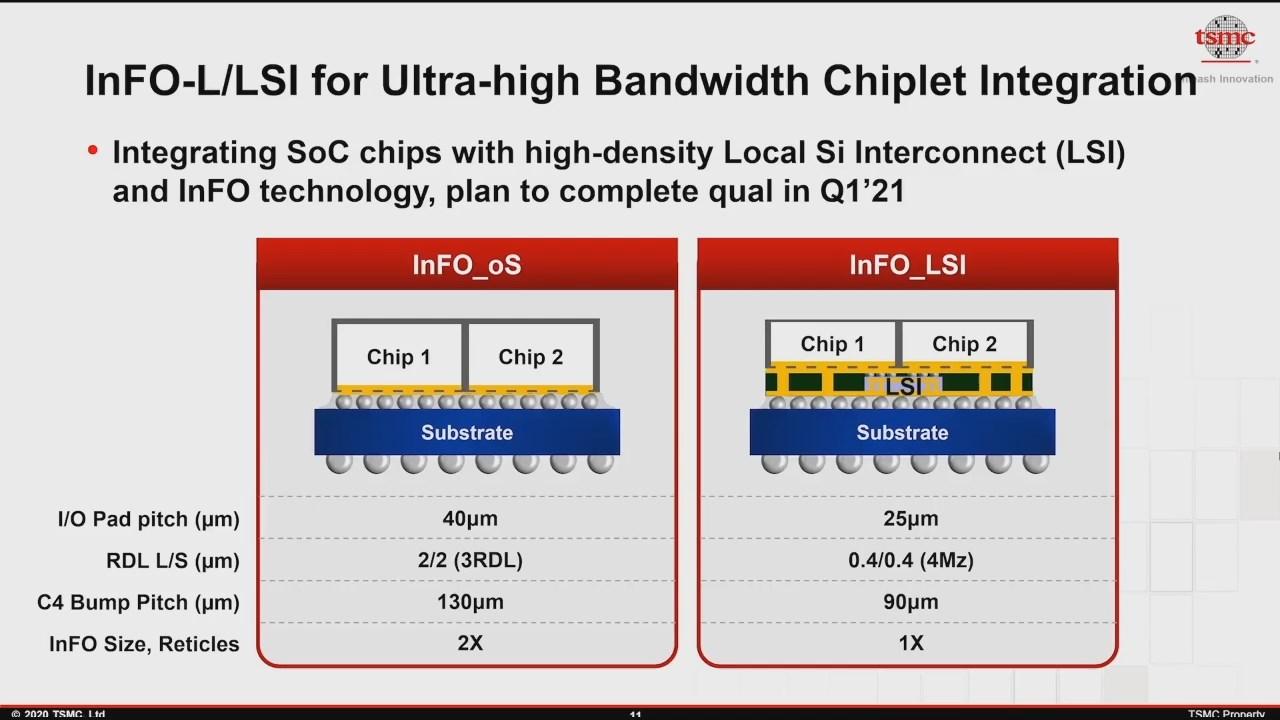

InFOは、TSMCのファンパッケージングまたはカプセル化技術であり、ダイをシリコンウェーハから取り外して別のキャリアウェーハに配置し、その上に銅RDLなどのより大きな構造を構築します。 (再分配層)そして続いてキャリア基板。

LSI統合を備えたInFOのTSMCバリアントは、InFO-LまたはInFO-LSIと呼ばれ、両方のチップ間の通信用にこのローカルシリコンインターコネクトミドルマンチップが新たに追加された同様の構造に従います。

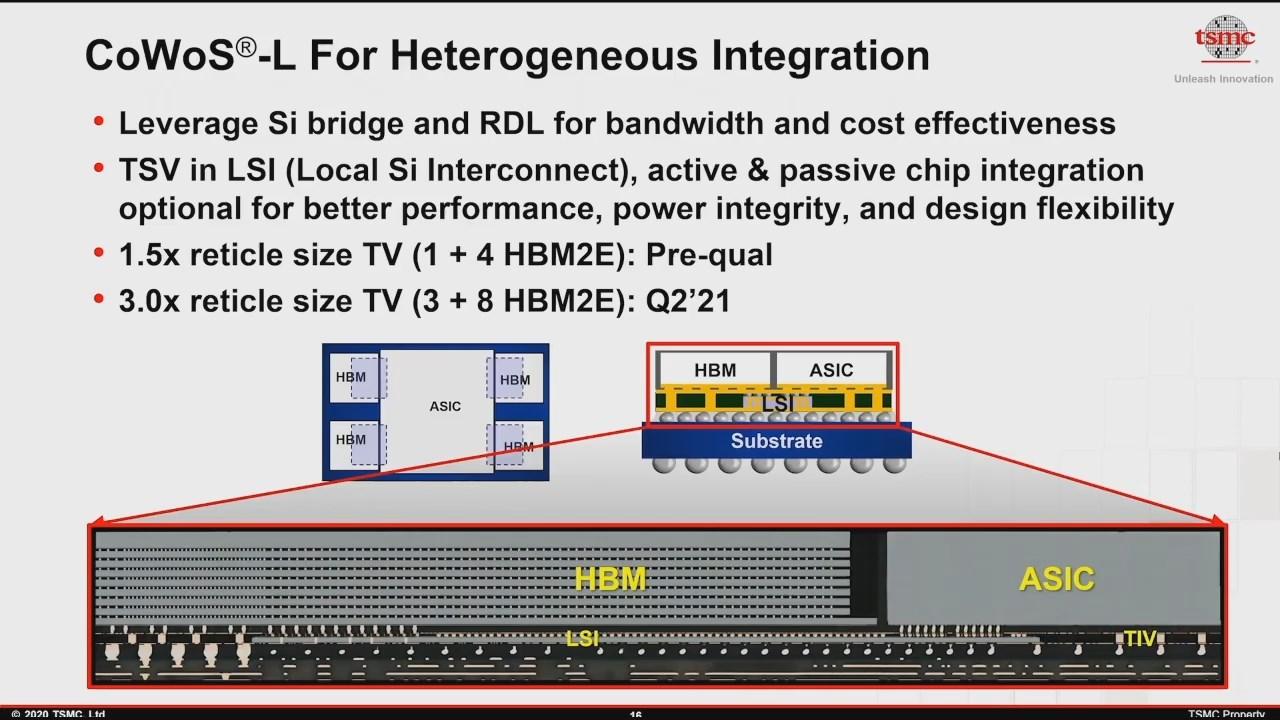

TSMCのCoWoS(Chip-on-Wafer-on-Substrate)は、当初は同社の2.5Dシリコンインターポーザーパッケージングテクノロジーとして説明されていました。現在もCoWoS-S仕様に準拠していますが、他のカプセル化テクノロジーもカバーしています。 その説明が示すように、RDLは最初にベース基板上に構築され、最後のステップとしてのみシリコンチップがセットに追加されます。

CoWoS-Lは、TSMCのチップパッケージングテクノロジの新しいバリアントであり、銅線RDLと組み合わせて使用されるローカルシリコンインターコネクトを追加して、RDLパッケージング実装を使用するよりも高い帯域幅を実現します。 (CoWoS-R)であり、フルシリコンインターポーザー(CoWoS-S)を使用した場合よりも低コストです。 言い換えれば、このカプセル化テクノロジーを使用すると、 低コストでより良いパフォーマンス .

TSMCは、LSIをアクティブまたはパッシブチップとして説明しています(チップ設計者のニーズとその予算に応じて)。 TSMC製錬所は、2021年の第XNUMX四半期にInFO-L認定を完了する予定ですが、CoWoS-Lは現在事前認定プロセスにあります。 LSIやEMIBなどのシリコンブリッジ相互接続技術は、設計者と消費者の両方に低コストで高性能チップ設計を提供することが期待されています。

要するに:より高性能でより安価なチップ、(ユーザーにとって)次のように変換する必要があるもの より強力で安価なプロセッサ .