というカンファレンスで インテル 同社が中国に持っている研究センターの社長は、2030年に向けて彼らが持っている目標について話し、それはHPチップをますます小型化し、消費量を毎回少なくすることに要約することができます. これは、より多くのトランジスタとより優れたエネルギー効率につながります . 彼らはそれをどのように達成するつもりですか?

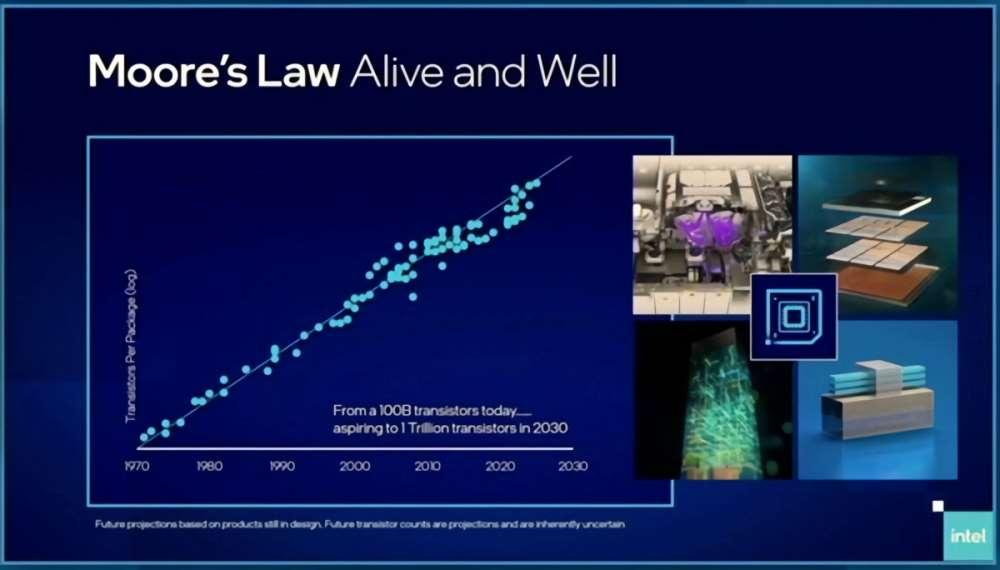

ムーアの法則は、Intel の創設者によって考案されたもので、法則とも言えず、観察でもありますが、概念が混同されることが多いため、誤解されることがよくあります。 いずれにせよ、それはチップの経済性やそのパワーを指しているのではなく、特定のスペース内のトランジスタの密度が頻繁に倍増することを指していることを明確にする必要があります。 これは時間の経過とともに減速してきましたが、現実には、今日でも有効です.

Intel から 2030 年までに XNUMX 兆個のトランジスタ チップ

チップ、つまり半導体の世界の進歩を追っている私たちにとって、トランジスタの密度を時々倍増できるようにするためには、将来的には新しい製造技術の。 と設計、特に分裂したチップなどの概念、および XNUMX 次元構造の使用、つまり、チップを上下に積み重ね、これらすべてを使用して、 最大で 10 倍の効率が得られ、内部に最大 XNUMX 兆個を収容できます。 トランジスタの。

現在、PC で使用されている最も複雑なチップは NVIDIAの中心と考えているAD102 GPU その目標と比較して密度が 4090% の RTX 7.6 について話しているので、Intel がその目標を達成するのに非常に長い時間がかかります。コア CPU でそうするか、逆に ARC GPU でそうするかを知っています。 いわゆる分散型マイクロプロセッサ、またはチップレットにより、ウェーハの格子限界を破り、モノリシックチップよりも多くのトランジスタを備えた構成を作成できることを忘れないでください。

いずれにせよ、単一ピースのチップが出荷されると、パノラマが完全に変わることを心に留めておく必要があります。チップ製造ノード。

エネルギー効率の桁違いの改善

すでにエネルギー効率について話している場合、考慮しなければならないのは、これらの言葉は、二酸化炭素排出量の削減などの称賛に値する目標であるにもかかわらず. 彼らがこのパラメータとハードウェアのタイプを測定しようとしている能力を知らないことを忘れることはできません.毎秒、浮動小数点数など。

これは簡単には達成できない目標であり、いくつかのテクノロジの開発実装が必要になります。それらの多くはまだ開発中であり、他のテクノロジは間もなく展開されます。 2ナノメートル以下の密度のRibbonFETタイプのトランジスタ、Power VIA電源、現在前例のない高度なリソグラフィシステムの使用、Foverosに似た新しいチップパッケージングシステムなどについて話しています.