Se segui da tempo il mondo dei microprocessori, la cosa più sicura è che avrai familiarità con le sigle RISC e CISC, che altro non sono che una definizione della struttura del set di istruzioni che gestisce un processore. Ebbene, negli ultimi anni è apparso un nuovo paradigma che è stato soprannominato VISC. In cosa consiste?

La maggior parte dei processori sul mercato sono diventati noiosi, poiché portano poco sul tavolo. Si basano sul miglioramento delle prestazioni regolando piccole parti in modo che il tutto funzioni meglio di prima, ma negli ultimi anni non c'è stata una rivoluzione come quella avvenuta con l'esecuzione fuori servizio a metà degli anni '90, tuttavia questo potrebbe cambiare grazie alle architetture VISC, che rappresentano un nuovo paradigma.

VISC è un insieme di istruzioni?

La prima cosa che può venire in mente leggendo questi acronimi e per la loro somiglianza sono le parole RISC e CISC, che si riferiscono alla natura dell'insieme di registri e istruzioni del processore, che non è oggetto di questo articolo, poiché sotto il concetto di VISC non ci riferiamo a un nuovo modo di categorizzare le istruzioni, ma a qualcosa di totalmente diverso.

Per capire come funziona il paradigma VISC, dobbiamo prendere in considerazione due diversi concetti riguardanti CPU prestazione. Il primo di questi è il fatto che oggi le CPU dei PC hanno un set di istruzioni interno ancora più piccolo di RISC, poiché ciò che fanno è trasferire ciascuna istruzione in microistruzioni più piccole internamente durante il processo. fase di decodifica. Se siamo puristi, la conclusione oggi che tutti i processori non sono RISC, ma che hanno un set di istruzioni molto ridotto che funziona internamente e che serve a costruire il resto delle istruzioni. Cioè, non appena un'istruzione raggiunge l'unità di controllo della CPU, viene suddivisa in un elenco di istruzioni.

Quindi la guerra tra RISC e CISC è stata vinta dal primo, ma con la trappola che x86, l'architettura CISC più diffusa, ha fatto la trappola di comportarsi internamente come un RISC. Fino ad oggi, eccetto per ARM, il resto dell'ISA RISC è disperso o sull'orlo della scomparsa. Inoltre, anche ARM ha adottato il concetto di suddividere le istruzioni in istruzioni più semplici, quindi entrambi i paradigmi al di fuori della definizione dell'ISA comune di una famiglia sono già estinti.

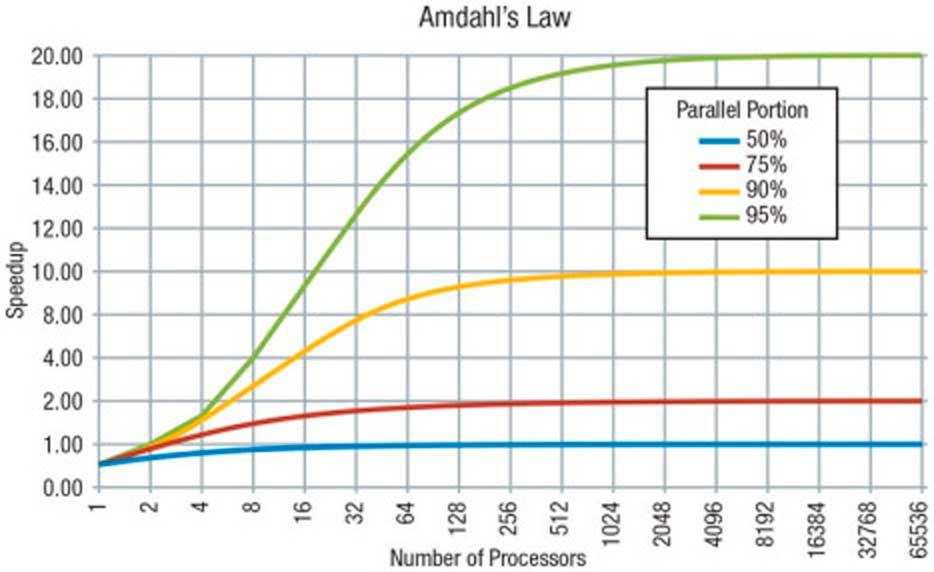

Legge di Amdahl

Per capire un programma dobbiamo capire che un programma ha due parti differenti:

- Quello che può essere eseguito solo in serie e, quindi, può essere risolto solo da un singolo kernel eseguendo un kernel di esecuzione solo.

- Quella parte del codice che può essere eseguita in parallelo, il che significa che può essere risolta da più core contemporaneamente e più ne sono presenti nel processore, più velocemente questa parte verrà risolta.

Se teniamo conto di quanto spiegato nella sezione precedente, concluderete che alcune delle istruzioni del processore che diventano microcodice diventano una successione di istruzioni che possono funzionare in serie o in parallelo tra più core, sebbene il solito sia che la maggior parte delle istruzioni viene eseguita in un unico kernel e che è da elementi condivisi che il codice viene eseguito in parallelo.

Pertanto, il fatto che una parte del codice venga eseguita da più core dipende esclusivamente dallo sviluppatore del programma, che deve programmarlo esplicitamente in modo che alcune parti funzionino in parallelo.

VISC e core virtuali

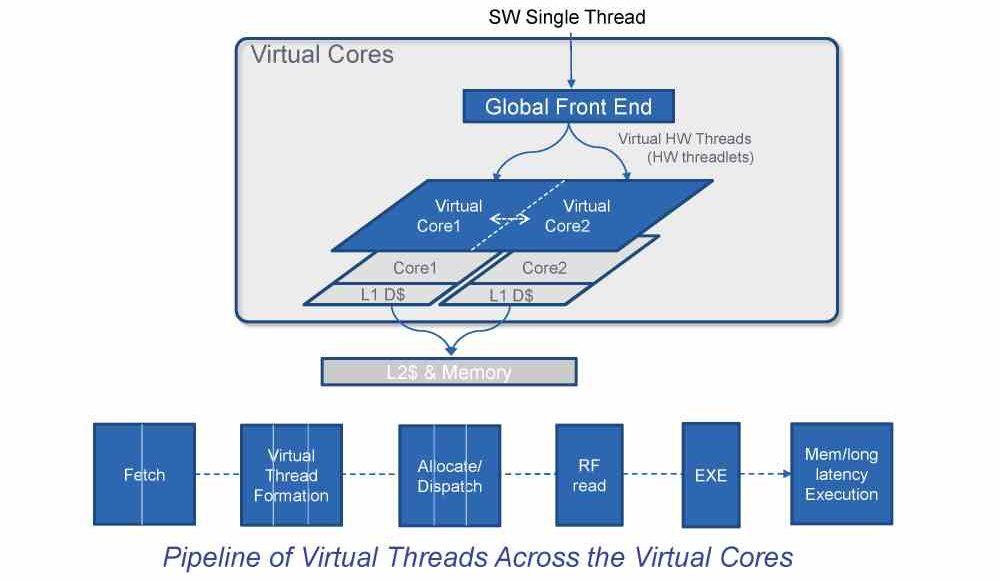

Una volta spiegato tutto quanto sopra, allora possiamo spiegare cosa significa l'acronimo VISC, la cui definizione è la risposta diretta alla seguente domanda: Quando si generano le microistruzioni in fase di decodifica, non possono funzionare? in parallelo con più core invece di farlo in un unico idem?

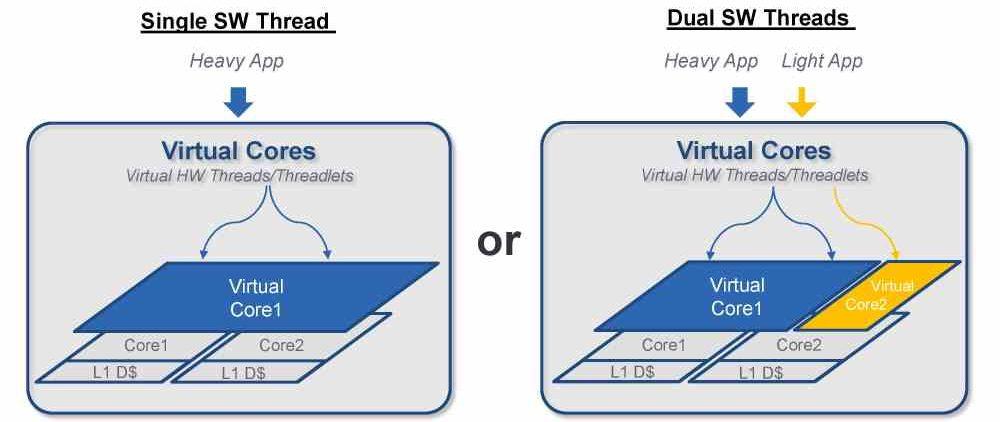

Bene, la risposta alla domanda sull'architettura VISC, che è stata sollevata per la prima volta da una società chiamata Soft Machines nel 2015 come concetto per migliorare le prestazioni della CPU. Questa piccola startup è stata acquistata da Intel nel 2016 e da allora hanno lavorato allo sviluppo di un'architettura VISC. Come funziona? Ebbene, si può definire molto facilmente: un singolo thread di esecuzione viene inviato al Global Front End del processore, che viene convertito in più thread che svolgono la stessa funzione e che lavorano in parallelo e girano in core virtuali. Il processo di conversione viene eseguito a livello software tramite un layer di traduzione, ma dobbiamo tenere presente che può essere qualcosa di semplice come un microcontrollore che esegue il trasferimento delle istruzioni.

Contrariamente a quanto accade nella distribuzione dei compiti in un processore multicore convenzionale, in un'architettura VISC non si intende che un core sia libero di eseguire un'istruzione, ma che gli elementi per eseguirla siano disponibili all'interno del processore per eseguirla. Ad esempio, può accadere che in un kernel convenzionale non venga utilizzata l'unità vettoriale, ma in questo paradigma può essere utilizzata per formare una delle istruzioni.

VISC e prestazioni

Quando si adotta un nuovo paradigma in termini di architettura, la prima cosa da considerare è come influisce sulle prestazioni, poiché non vale la pena cambiare il paradigma attuale se non comporta un aumento delle prestazioni complessive del processore. Il modo più classico per aumentare le prestazioni di un processore è aumentare il numero di istruzioni che vengono risolte per ciclo di clock, questo significa rendere l'hardware sempre più complesso, in quanto con l'aggiunta dei core dobbiamo contare tutta l'infrastruttura che li circonda che diventa lo stesso o più complesso.

Ciò che differenzia VISC dal resto non è altro che la distribuzione delle risorse del processore per l'esecuzione delle diverse istruzioni che viene eseguita in pochi cicli di clock, tra 1 e 4 core. In questo modo, se ci sono due istruzioni che competono per altre risorse in un core, allora possono essere riassegnate molto rapidamente a un'altra parte del processore dove sono disponibili quelle stesse risorse.

Il paradigma attuale, che è l'esecuzione fuori ordine, ciò che fa è riordinare l'esecuzione delle istruzioni in base alle risorse libere in ogni momento e quindi riordinare l'output dei dati già elaborati. La limitazione? L'allocazione delle risorse viene eseguita a livello single-core anziché multi-core e questa è la chiave per prestazioni più elevate per le architetture VISC.

Esistono oggi questi processori?

Sebbene il concetto sia molto buono sulla carta, nessuno ha ancora presentato un processore che funzioni sotto questo paradigma, ma visto che ci stiamo gradualmente avvicinando ai limiti del paradigma attuale, è importante tenere presente che ci sono soluzioni che possono servire per migliorare le prestazioni della CPU dei nostri PC per il futuro.

Avere un processore più potente non è solo averne uno più veloce o con più core, ma si basa sul saper sfruttare le risorse disponibili. L'esecuzione fuori servizio è stato il primo passo in tal senso, tuttavia da allora, al di fuori del multicore, le modifiche sono state generalmente minori. VISC è ancora un concetto, tuttavia non è impossibile ed è un modo per sfruttare le risorse disponibili nel processore in modo molto più efficiente.

Finora sappiamo che il concetto è possibile in una CPU poiché Soft Machines ne ha progettata e costruita una con questo paradigma, quindi sebbene fosse a livello sperimentale sappiamo che è possibile realizzare un tale progetto. Altra cosa diversa è la difficoltà di portare l'intero set di istruzioni e registri x86 a questo paradigma, per sua natura estremamente complesso.