Il mercato punta ai chiplet, o almeno così sembra. AMD è stato con il suo accordo basato su MCM da alcuni anni e Intel sta per fare il passo successivo con tecnologie come Foveros, ma è una mossa da non perdere? Conosciamo già i suoi vantaggi e i suoi svantaggi? Oggi vedremo il buono e il cattivo dei chiplet e perché l'industria non vede questo modo di creare CPU così chiaramente.

Tutti i principali inclusi AMD, Intel, TSMC e Marvell stanno lavorando su approcci diversi al mondo dei chiplet, diverse alternative stanno cercando di sviluppare progetti più avanzati. Sebbene negli articoli precedenti abbiamo trattato questo argomento specifico, ci sono alcuni punti che lasciamo per questa occasione, poiché l'industria non è così sicura che i chiplet siano la strada da percorrere.

Mancanza di ecosistemi, standard, tempi e costi di sviluppo

Non tutto ciò che luccica è l'oro e sebbene AMD sia uno dei pochi a lanciare sul mercato prodotti reali basati su chiplet, non è esattamente facile farlo. Il problema è che non esiste un ecosistema, non esistono standard fissi che l'industria può seguire per ridurre i tempi di creazione e i costi di sviluppo.

Ogni azienda sta affrontando, più o meno, i loro problemi individualmente, unitariamente, ma nessuno di essi ha separatamente tutti i pezzi per formare il puzzle. Invece, e abbastanza curiosamente, affrontano quasi tutti gli stessi problemi:

- Tentano di offrire chiplet ottimali e con connessioni migliori e più veloci che possono adattarsi a prodotti diversi.

- Hanno bisogno di tecnologie di terzi in misura maggiore o minore.

- Mancanza di supporto nella progettazione degli schemi di interconnessione tra gli stampi.

- Hanno bisogno di IP corretti con capacità di produzione.

Ciò sta causando, ad esempio, che Intel segua il suo percorso basato sul monodie per le sue CPU, cosa che vedremo da diversi anni. AMD è stato un pioniere, ma sta pagando grandi costi perché dipende da terze parti e queste, a loro volta, aziende specializzate per determinate tecniche che devono essere sviluppate esclusivamente, aumentando i costi complessivi.

Gli strumenti EDA sono necessari per unire tutti questi pezzi, poiché sono architetture e prodotti diversi, interfacce fisiche e logiche per unire e classificare le informazioni di varie aziende per lanciare un singolo prodotto. Inoltre, alcuni componenti chiave potrebbero non essere disponibili come tali, aggravando il problema.

L'industria deve condividere IP diversi se vuole andare avanti con i chiplet

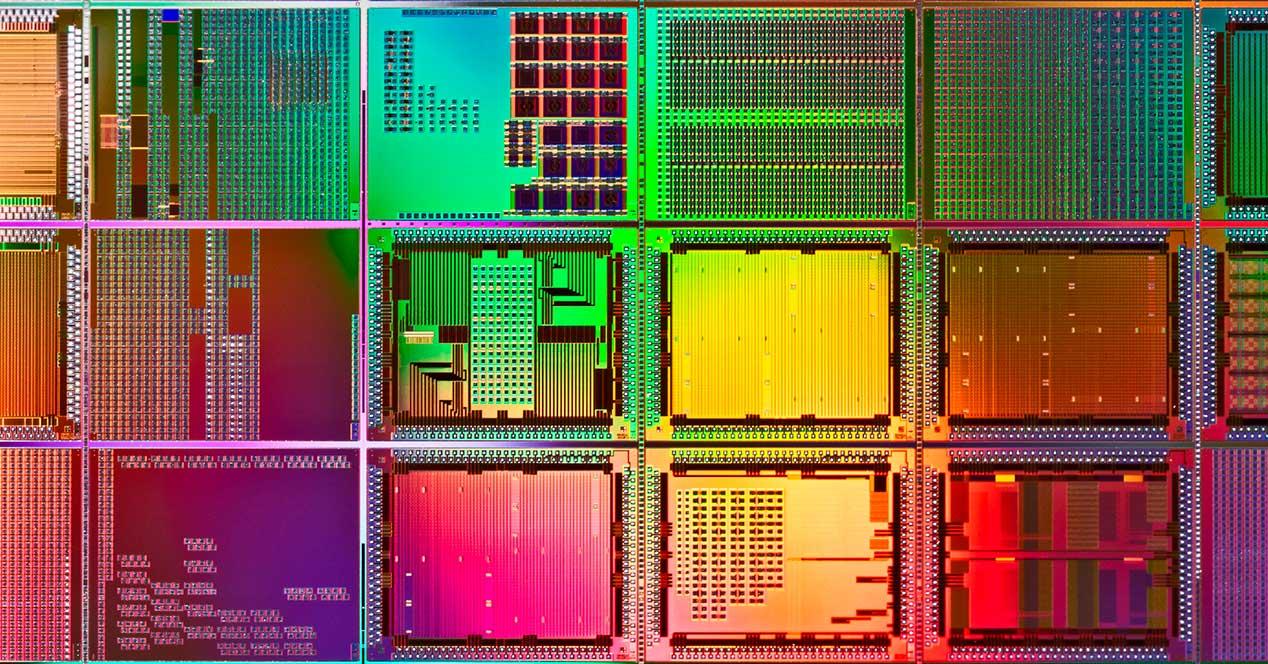

![]()

Non c'è più cieco di chi non vuole vedere. Un detto che sembra non gradire alcuni settori della produzione IP per le grandi aziende. L'investimento è fatto e la strada deve essere quella di condividere almeno una serie di interfacce standard per l'integrazione del chiplet, cosa che li danneggerà gravemente economicamente.

L'esempio da seguire è semplice: NVMe, SSD SATA o DRAM stessa. Usano la stessa interfaccia, in modo che le diverse parti non abbiano bisogno di conoscere i dettagli degli altri poiché sanno cosa aderire e come devono essere il design dei PCB, i collegamenti e i chip.

Risparmiano costi, tempo, ottimizzano i saldi finanziari, producono molto di più e meglio, ma la cosa più importante è che tutte le aziende competano alle stesse condizioni, promuovendo la competitività del settore.

A questo proposito, e come potrebbe essere altrimenti di fronte a tale caos, le grandi aziende stanno sviluppando la base di questi standard tanto necessari, le tecnologie di interconnessione con interfacce aperte affinché le aziende possano unirsi alla loro causa.

Tanto che attualmente la disputa sarà tra quattro contendenti per il titolo: AIB, BoW, OpenHBI e XRS , dove inoltre, il ODSA sta sviluppando da parte sua il cosiddetto Chiplet Design Exchange o CDX , un formato aperto per lo scambio sicuro di informazioni mantiene la riservatezza e mantiene i flussi di lavoro e le informazioni per i prototipi.

Pensando a lui, cerchiamo di organizzare le diverse interfacce per iniziare a creare un sistema confidenziale eterogeneo che progetta gradualmente i chiplet più facilmente e in base allo standard che finisce per essere imposto. Può darsi che non vi sia un solo vincitore, poiché l'industria deve innovare in almeno due modi, ma almeno sarebbe il primo passo per avere un obiettivo comune per tutti.

La creazione dei chip e delle loro interconnessioni richiede anche l'unificazione dei criteri

Se il puzzle era già difficile da risolvere, tenere presente che anche i disegni delle interconnessioni (ovvero sporgenze o microbump) non sono definiti standard. Ogni azienda crea i suoi dossi e il suo packaging, quindi poiché non vi è alcuna standardizzazione in questo, sono necessari strumenti specifici per la verifica, la creazione e la supervisione dei wafer, sia per i chip che per gli interposer.

I passaggi sono quasi tutti automatizzati, in cui i wafer passano diverse ore di test, test e monitoraggio con contenuti elettrici, fisici e visivi. Come previsto, interconnessioni tramite microbops sono molto più grandi in dimensioni fisiche in trucioli che in matrici monolitiche, dove possono raggiungere da 25 micron a 40 micron.

Per avere un'idea e prendere un tipico wafer da 300 mm, controllare ogni connessione dei microbump è come posizionare la testa di uno spillo su un campo da calcio, secondo il vicepresidente di FormFactor. La precisione è incredibile e questo significa che senza uno standard i costi continueranno a crescere per tutti, dal momento che il nuovo approccio microbumps si avvicina 10 micrometri e i test non smetteranno di aumentare di prezzo a causa dell'immensa precisione di cui hanno bisogno per i test corrispondenti.

Quindi e in sintesi, è un vantaggio o uno svantaggio seguire il percorso dei chiplet? È molto bello che vediamo il mare dalla riva e siamo colpiti da ogni lancio o tecnologia progettata da Intel e AMD. Ma sott'acqua il settore non è così chiaro e sebbene siano stati definiti i passi da seguire, quelli di Swan, ad esempio, non lasceranno da parte le CPU monolitiche fino a quando l'intero settore non potrà avere una serie di standard da seguire.

AMD dovrà sostenere il peso di tutto ciò che è stato detto e nelle mani di TSMC, dove come abbiamo già commentato più di una volta, i prezzi dei suoi processori dovranno aumentare prima o poi per rimanere redditizi e, soprattutto, aumentare il margine di profitto. Non sarà un lisciare viaggio per uno dei due giganti, Intel ha EMIB, Foveros, AIB e Co-EMIB , TSMC in sviluppo con Sistema su chip integrato (SoIC) e AMD cerca di quadrare i pezzi per le sue nuove architetture basate su varie aziende che forniscono ciò che è necessario per questi chiplet.

Se qualcuno pensava che fosse cucito e cantato, si sbagliavano molto. Il futuro non è nero, ma richiede accordi e perdite a lungo termine che tutti dovranno sostenere.