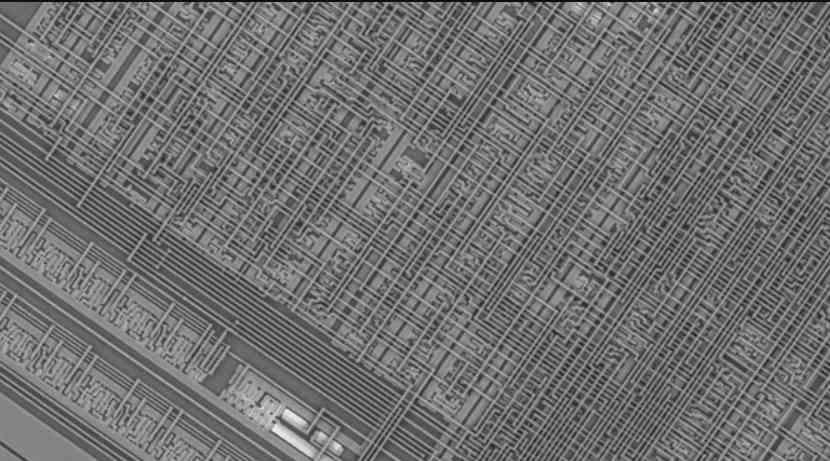

AMD a récemment présenté la première maison Processeur avec cache vertical, qui consiste en l'utilisation de la technologie 3DIC pour connecter un module SRAM au-dessus d'un Zen 3 CCD. Qu'est-ce que le cache vertical peut contribuer aux performances des CPU, GPU et autres ? des processeurs et des composants d'un PC ? C'est ce que nous allons essayer d'expliquer dans cet article.

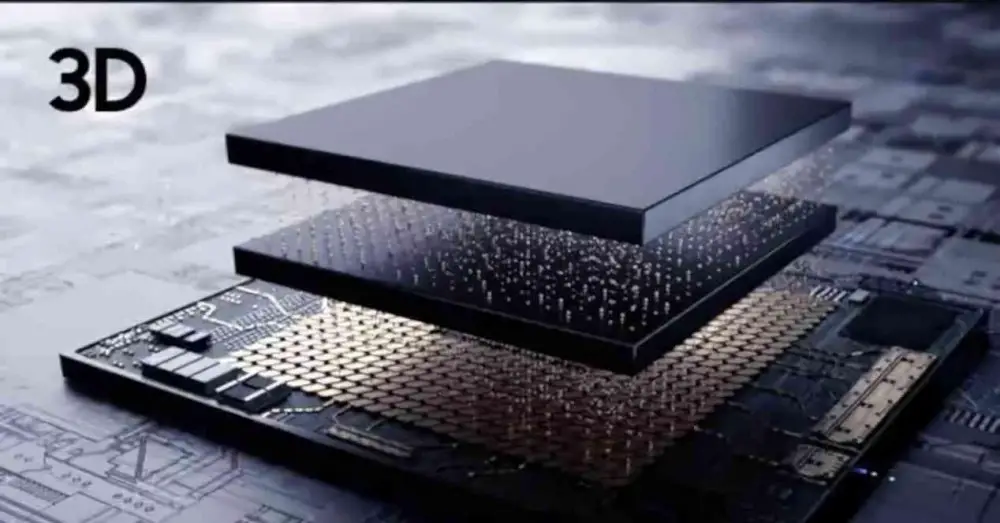

L'ajout du "V-Cache" d'AMD dans certains des futurs processeurs AMD basés sur Zen 3 a posé la question suivante : est-il judicieux d'étendre le cache d'un processeur à des niveaux stratosphériques afin de gagner en performances ? ? De toute évidence, l'idée d'appliquer une mémoire cache supplémentaire verticalement n'est pas quelque chose que AMD peut faire exclusivement et les systèmes d'interconnexion verticale entre les puces permettent de connecter une puce de mémoire SRAM juste au-dessus d'un APU, d'un CPU ou d'un GPU sans problème.

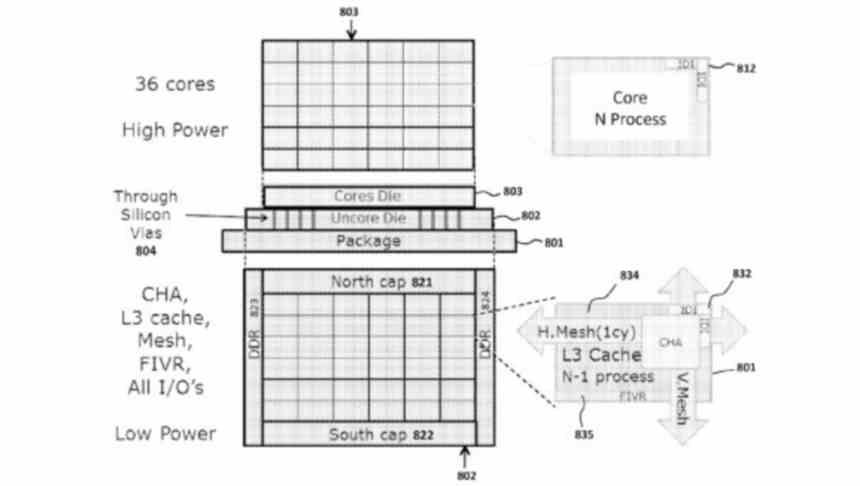

Donc ce qu'AMD a fait en arrière-plan n'a rien de spécial, il est vrai qu'ils ont été des pionniers dans l'application d'un système SRAM 3D afin d'étendre la mémoire cache totale dans les Chiplets CCD, il faut noter que la SRAM verticale comme cache sera toujours le cache de dernier niveau ou LLC d'un processeur et donc son implémentation changera en fonction du type de processeur dont nous parlons.

Cache vertical uniquement au dernier niveau

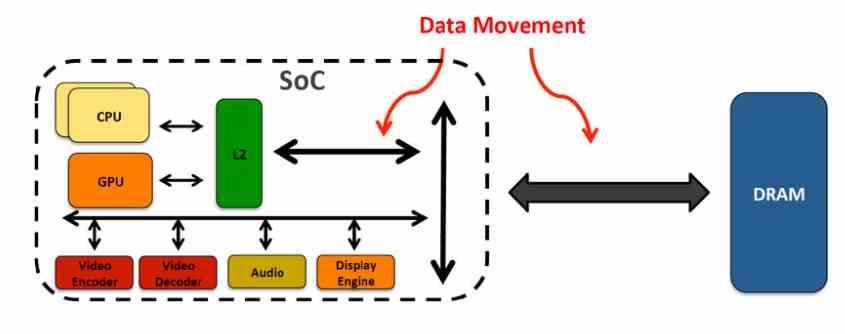

La réalité est qu'aujourd'hui de manière générale, tous les processeurs sont des SoC, au sens où ils utilisent plusieurs éléments de traitement qui peuvent être homogènes au sens d'utiliser tous les mêmes cœurs ou hétérogènes en même temps. temps d'avoir différents types de noyaux. Ce qu'ils ont en commun, c'est le pont nord, qui Intel appelle « Uncore » et AMD appelle « Data Fabric ». Quel que soit le nom, nous parlons vraiment du même concept.

Qu'est-ce que cela a à voir avec le cache vertical? Eh bien, le cache vertical de par sa position sur la puce dans un SoC ne peut jamais être placé avant le contrôleur mémoire dans la hiérarchie. Dans les puces Zen 3 CCD, il n'y a pas de contrôleur de mémoire car il est situé dans l'IOD, qui est situé dans une autre puce, mais dans un APU hypothétique, le cache vertical serait situé au-dessus du contrôleur de mémoire, bien que juste plus tôt dans la hiérarchie que RAM, mais après le niveau de cache supérieur du CPU ou du GPU.

Cache vertical au lieu de mémoire verticale

Dans ce postulat, l'idéal serait que la RAM soit aussi proche que possible du processeur. Que diriez-vous de mettre une RAM complète sur le processeur dans une interface 3D ? Cela ne nous conviendrait pas du tout en raison de la capacité élevée en dizaines de gigaoctets requise par la RAM actuelle. Mais que diriez-vous de mettre de plus en plus d'étages de mémoire sur le processeur ? Après tout, cela peut être fait aujourd'hui.

Cela semble être une excellente idée et il est possible de le faire, mais cela cesse de l'être lorsque l'on considère qu'à chaque nouvel étage de mémoire, le nombre d'ensembles complets entre le processeur et la mémoire au-dessus d'eux diminue. Ensuite, on ne peut pas oublier le phénomène de chaleur, chaque nouvel étage oblige à baisser la vitesse d'horloge à la fois de la mémoire et du processeur. Du coup, ce qui semblait être une bonne idée ne l'est plus, nous avons entre nos mains un processeur très coûteux à fabriquer, en quelques unités et avec des performances pires qu'avec les éléments séparément.

Il est donc préférable de placer un seul étage au dessus du processeur, la mémoire n'ayant pas assez de capacité pour fonctionner aujourd'hui comme de la RAM, mais comme un cache de dernier niveau.

Performances du cache vertical sur les processeurs

Le seul objectif du cache de chaque processeur est de réduire le temps d'accès du CPU à la mémoire RAM, mais ces derniers temps, la transmission de données dans les quantités nécessaires est devenue un coût énergétique énorme lorsque les architectes doivent chercher le chemin de réduire le nombre d'accès dans lesquels le CPU ou le GPU fera un accès à sa mémoire correspondante. Pourquoi un grand cache de niveau supérieur est important ici.

Le cache vertical n'a donc pas vocation à augmenter la capacité de traitement d'un CPU, mais ses performances. Nous devons comprendre que dans un système, nous n'atteignons jamais 100% de performances et il y a toujours des pertes. Dans le cas d'un processeur, une partie importante de la perte de performances est en communication avec la hiérarchie de la mémoire, qui comprend les caches.

Le cache vertical étant le dernier niveau, il inclura toutes les données nécessaires aux caches précédents et avec sa taille énorme, il réduira la quantité d'accès du processeur à la RAM, mais son efficacité ne sera jamais de 100%, même avec un très grand cache, le programme peut faire une requête à une adresse mémoire qui n'a pas été copiée dans le cache de dernier niveau, forçant le processeur à accéder à la RAM qui lui est affectée.

Comment les performances d'un cache sont-elles mesurées ?

Lorsque le CPU recherche une donnée ou une instruction dans la hiérarchie du cache système, il commence par ceux qui sont les plus proches du CPU lui-même, s'il trouve les données alors c'est ce que nous appelons un "hit", en référence à ce que le CPU a ciblé dans le cache et atteint la cible. Mais si vous ne trouvez pas les données à ce niveau de cache, c'est un échec et vous devez regarder les niveaux inférieurs. Nous appelons cela un "manque" dans le sens où le CPU n'a eu aucun but pour trouver les données et / ou les instructions nécessaires, pendant ce temps le CPU a un arrêt ou un "décrochage", puisque le CPU ou le GPU il n'a pas de données procéder.

Dans le cas du cache vertical, puisqu'il ne ferait pas partie des premiers niveaux de cache, alors son existence ne peut empêcher le passage des niveaux inférieurs du cache lui-même. Nous avons déjà dit qu'il est impossible de convertir les premiers niveaux de cache en un cache vertical, surtout dans un monde où les processeurs sont multi-cœurs depuis un certain temps et les niveaux de cache supplémentaires sont utilisés pour communiquer des groupes de cœurs entre eux. et même de nature différente dans certains cas.

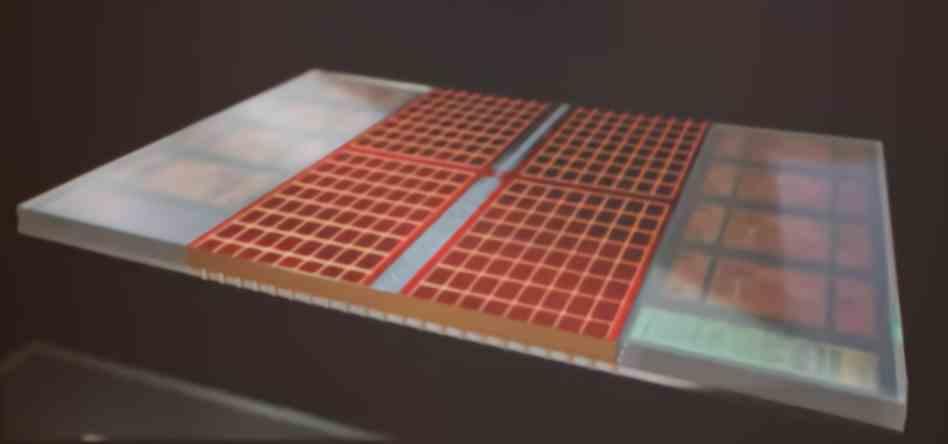

Performances sur les GPU et autres types de processeurs

Dans les GPU, nous avons vu la mise en œuvre de l'AMD Cache infini, qui est un type de grand cache qui pourrait être déplacé vers la partie supérieure du GPU et séparé du cœur principal. Pour le moment, cela ne donne pas d'augmentations de performances considérables, mais un GPU à cache vertical aurait une capacité bien supérieure aux 128 Mo du GPU Navi 21, ajoutez cela à un nœud de fabrication plus avancé et n'étant pas limité en termes de surface et de la quantité de cache de dernier niveau peut aller jusqu'à 512 Mo et même 1 Go.

Quelle serait la particularité d'un GPU avec un cache de 1 Go ? Concernant le Ray Tracing, des tests ont été réalisés et il a été montré que la localisation proche de certaines données par rapport au GPU augmente fortement les performances de ceux-ci lors du traitement de scènes avec le ray tracing. Il est donc possible que les futurs GPU de NVIDIA, Intel et AMD mettront en œuvre un cache vertical pour augmenter leurs performances dans les scènes avec le Ray Tracing, qui sera de plus en plus courant.

Un autre marché important est celui des contrôleurs de mémoire flash, qui utilisent aujourd'hui des puces mémoire DDR4 ou LPDDR4 comme cache. La mise en œuvre d'un cache vertical dans ces processeurs suffirait à supprimer la DRAM et à rendre les SSD NVMe moins chers, car le cache ne nécessitera pas l'utilisation de mémoire DRAM.