L'un des points les plus importants lors de la conception d'un nouveau processeur, quelle que soit sa fonction, est sa consommation énergétique et donc son organisation pour tirer le meilleur parti de l'énergie qui lui est fournie. C'est là que l'on appelle le Power Delivery Réseau ou PDN entre en jeu. Qu'est-ce que c'est et pourquoi est-ce important dans la conception d'un nouveau processeur ?

Il existe un mythe, ancré dans l'esprit de nombreuses personnes, selon lequel la consommation électrique d'un processeur est quelque chose que les fabricants découvrent soudainement lorsqu'ils passent de la phase de conception à la phase de pré-production. La réalité est bien différente, après tout, un processeur n'est rien de plus qu'un circuit électrique à très, très petite échelle. Nous parlons donc de la façon dont la façon dont les électrons se déplacent dans le circuit est cruciale et fait partie de la conception initiale du processeur dès le départ.

Comment la consommation d'énergie d'un processeur est-elle mesurée ?

On ne peut pas savoir quelle est la consommation énergétique exacte d'un processeur, car une série de phénomènes physiques peuvent se produire qui font varier le résultat et ne sont connus qu'une fois le design réalisé et donc on passe du conceptuel au réel. Une approximation est donc faite, ce qui aide les ingénieurs à se faire une idée approximative de ce que sera la consommation d'énergie.

La formule générale est la suivante :

Puissance (watt) = nombre de portes logiques * capacité * fréquence d'horloge * tension au carré.

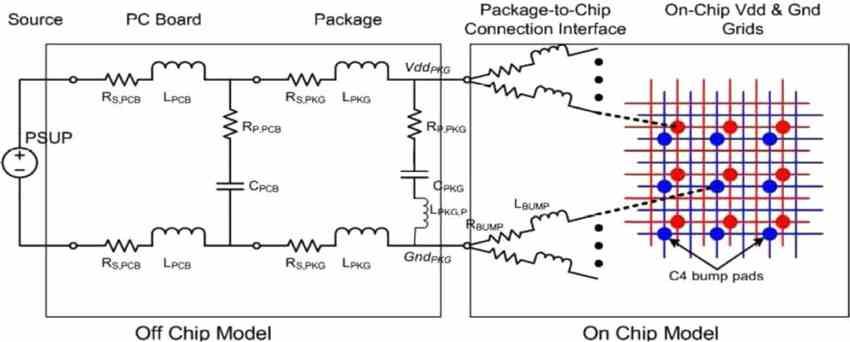

Mais ça est une estimation très générique , au sein d'un même processeur, les concepteurs peuvent utiliser différents types de portes logiques même au sein d'un même type et avec des niveaux de consommation différents. Mais surtout cela dépend de la manière dont les différentes portes logiques qui composent les différents éléments du processeur sont connectées les unes aux autres. C'est là que nous entrons dans le Power Delivery Network ou PDN. Ce qui fait partie de la conception de chaque processeur et fait référence à la façon dont la puissance est répartie entre les différentes portes logiques.

Qu'est-ce que le réseau de distribution d'énergie ?

Lors de la conception d'un processeur, on arrive au point où il faut organiser les différents blocs qui le composent et les interconnecter entre eux pour la communication. Mais chaque élément nécessite un flux de courant électrique pour fonctionner. Car ce qui se passe lors de la construction d'un bâtiment dans lequel la distribution du réseau électrique doit être conçue, il en va de même lors de la conception d'un processeur.

Dans un Processeur, ce qui consomme le plus, ce sont les interconnexions, aujourd'hui entre les interconnexions internes et externes à l'intérieur, 3/4 de la consommation interne de celles-ci s'en vont et c'est l'un des plus grands défis pour les ingénieurs aujourd'hui. Ce qui en fait un challenge lors de la création de nouveaux processeurs avec de plus en plus de cœurs où non seulement l'interface de communication, mais aussi lors de l'alimentation des différents blocs du processeur.

Peu importe que nous soyons devant le processeur 1 W d'un smartphone, les 45 W d'un ordinateur portable gaming haut de gamme ou les 200 W d'un processeur serveur. Tous ont été conçus avec un Power Delivery Network spécifique. Ce qui implique que chacun des centaines de millions, mais des milliards, doit fonctionner à la bonne tension. Si, par exemple, la tension était trop basse, les données pourraient varier et le processeur fonctionnerait non seulement avec des données incorrectes, mais pourrait également affecter la stabilité du processeur.

Quels sont les défis actuels lors de la conception d'un PDN ?

Au fil du temps, la tension à laquelle fonctionnent à la fois les processeurs et les mémoires a diminué. Initialement, les conceptions d'un ordinateur complet ont été réalisées à l'aide de plusieurs puces interconnectées sous l'interface TTL, logique transistor à transistor, avec une tension de 5 V. Actuellement avec l'utilisation de transistors FinFet à 7 nm nous nous déplaçons autour de 0.5 V et 1 V. Ce qui représente un défi pour les concepteurs de systèmes.

Dans un processeur numérique, le signal est traité de manière binaire et donc la tension fluctue entre deux valeurs de tension, l'une active et l'autre avec le processeur éteint. Grâce à cela, les valeurs sont suffisamment séparées pour que les hauts et les bas de celles-ci ne finissent pas par perturber le signal envoyé. cependant, avec la tension de plus en plus basse vient un problème et c'est que pour alimenter les processeurs les plus puissants avec suffisamment de puissance, nous devons augmenter la quantité d'amplis qui l'alimentent. Étant donné que la consommation de tout circuit électronique est proportionnelle au carré de sa tension, la plupart des concepteurs se sont attachés à la maintenir aussi faible que possible dans les spécifications.

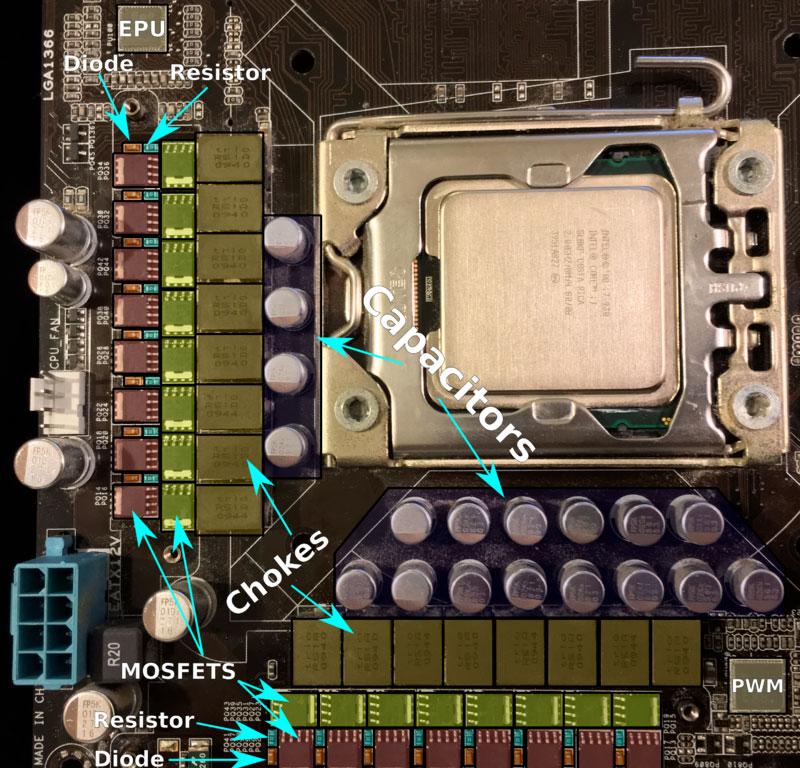

Le paradigme de basse tension et d'ampérage élevé est un défi parce que plus de câbles sont nécessaires pour transporter la plus grande quantité de courant nécessaire. Rendre le réseau de distribution d'énergie plus compliqué qu'il ne devrait l'être, non seulement au sein du processeur lui-même, mais également à l'extérieur. Lorsque l'organisation des VRM sur le carte mère ou la carte d'extension est importante dans le système électrique complexe.

Réseaux de distribution d'électricité aujourd'hui et à l'avenir

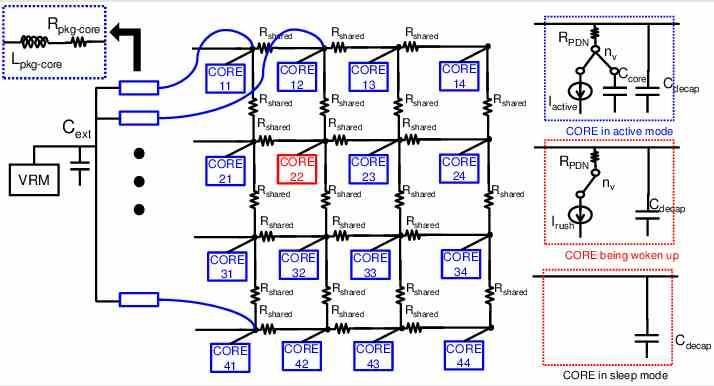

Ces dernières années, des mesures ont été prises pour économiser l'énergie et augmenter l'efficacité des processeurs. Ceux-ci incluent l'utilisation de réseaux de distribution d'énergie construits de manière modulaire. Qui sont conçus pour que certaines parties du processeur s'éteignent complètement lorsqu'elles ne sont pas utilisées pour consommer moins d'énergie. N'oublions pas non plus les mécanismes qui permettent de faire varier dynamiquement la tension d'un processeur afin de faire varier la vitesse d'horloge et la consommation d'énergie.

Un processeur fonctionnant à 1 GHz avec une tension de 1.2 V aura les mêmes performances qu'un processeur de 0.6 V à la même fréquence d'horloge, mais il consommera 4 fois plus pour le même travail. C'est pourquoi de nombreux processeurs et GPU modernes ont leurs réseaux de distribution d'énergie conçus pour abaisser la tension au minimum nécessaire lorsque la vitesse d'horloge est faible. Cela augmente le niveau de complexité du processeur, car il est nécessaire de concevoir le processeur de manière à ce qu'il puisse fonctionner avec différentes tensions dans sa conception.

Les processeurs d'aujourd'hui sont constitués de milliards de transistors qui forment des centaines de millions de portes logiques et avec eux des dizaines de millions de systèmes combinatoires et séquentiels. La conception du PDN est donc devenue extrêmement complexe au fil du temps et si nous ajoutons ce que nous avons mentionné il y a quelques lignes, il devient donc l'une des pièces les plus importantes dans la conception de tout processeur.

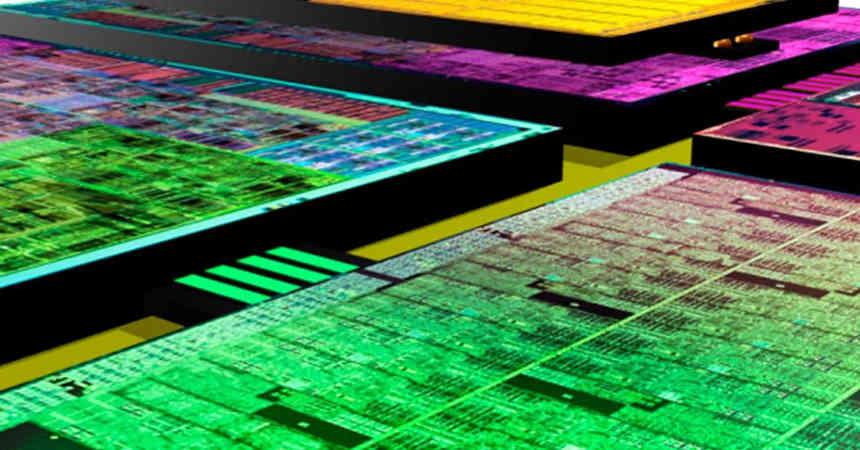

Les choses se compliquent avec les chiplets

L'adoption des chiplets signifie que le Power Delivery Network n'est pas seulement intégré dans chacun des chiplets, mais aussi dans l'interposeur qui les communique entre eux. Compte tenu du fait que l'interphone est le plus énergivore dans un processeur monolithique et que le câblage d'un système de puces augmente sa longueur entre les différentes puces, il s'avère que le plus grand défi réside dans la distribution de la puissance dans ces configurations.

La solution? Il est passé par l'utilisation d'interconnexions verticales, beaucoup plus courtes et plus nombreuses. Ce dernier leur permet de fonctionner à une vitesse d'horloge plus faible et donc à une tension plus faible. Quelque chose qui est crucial pour déplacer l'énorme quantité de données que nécessitent des applications telles que l'intelligence artificielle ou le rendu graphique. Mais en même temps cela pose une série de problèmes dans la conception des interposeurs, dont les services marketing ne parlent généralement pas en public, mais qui pour les ingénieurs deviennent un énorme casse-tête.

Dans tous les cas, dans le concept des puces, malgré le fait que nous ayons physiquement des différences de puces, son PDN est en fait conçu comme s'il s'agissait d'un seul processeur.