L'un des concepts les plus répandus en informatique aujourd'hui est sans aucun doute celui de XMP. Tout utilisateur modérément intéressé par le matériel sait que lorsque l'on parle de profils d'overclocking de la mémoire, Intel a pris la mesure de AMD, qui essaie constamment de s'adapter à ces exigences grâce à sa technologie AMP. Avec le départ d'Alder Lake-S en tant qu'architecture révolutionnaire, Intel est allé plus loin en présentant XMP3.0 , mais quelle nouvelle cache-t-il ?

Certains se demandent les raisons des décisions d'Intel concernant RAM et spécifiquement XMP. Bien que nous ne le sachions jamais, la vérité est que le passage de la DDR4 à la DDR5 était un moment idéal du point de vue de l'overclocking pour mettre en œuvre des changements et des améliorations, car comme nous le voyons, 4,800 XNUMX MHz du JEDEC ils sont laissés pour compte quelques jours seulement après l'introduction des processeurs Core 12.

Par conséquent, et compte tenu de la vitesse à laquelle les fabricants accélèrent et mettent à jour leurs modules avec des vitesses série croissantes, il ne reste plus qu'à se demander si Intel a pris cela en compte ? XMP 3.0 est-il à jour avec ce qui lui sera demandé ?

Intel XMP 3.0, un twist nécessaire

eXtreme Memory Profile ou XMP est avec nous depuis 2007 et dans cette troisième version avec le recul et après 14 ans, il est normal que le géant bleu lance une nouvelle révision avec des nouveautés. Pourquoi? Pour les changements que DDR5 suppose par rapport à DDR4. Nous n'entrerons pas dans ce sujet puisque nous l'avons déjà traité en extension, mais s'il y a quelque chose à dire sur XMP 3.0 c'est qu'il est exclusif à la DDR5 en tant que telle.

Le terme Profil de son nom vient au doigt pour expliquer le premier des points qu'Intel a donné aux constructeurs, puisque comme on le sait bien cette technologie repose sur la reconnaissance d'une série de tables de configuration que chaque constructeur intègre au goût par modèle , la version de la puce et de la mémoire pour que l'IMC reconnaisse et applique ces paramètres via le micrologiciel.

Quoi de neuf dans Intel XMP 3.0

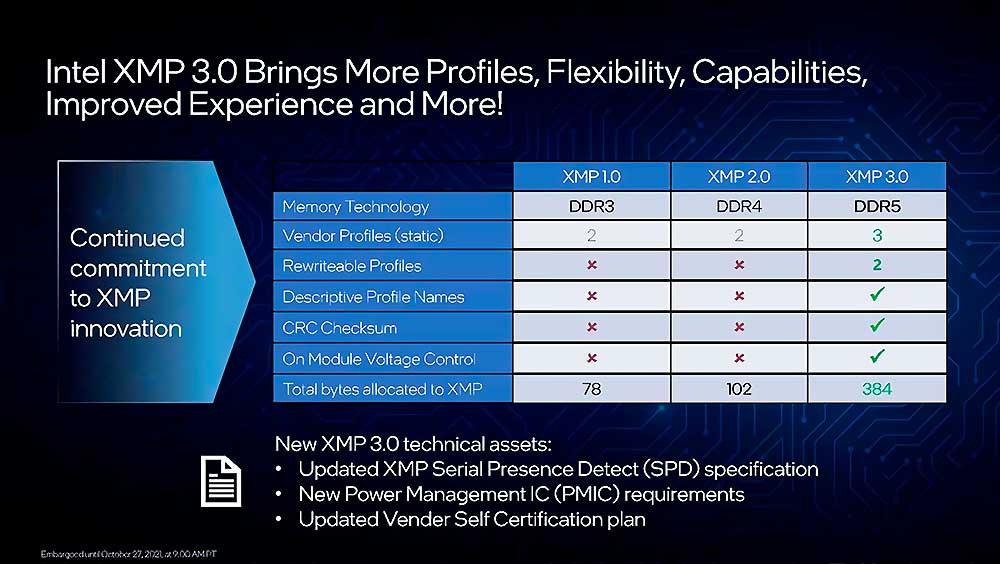

Ces tableaux comprennent des vitesses en MHz, des horloges et des temps d'accès primaire, secondaire et tertiaire qui sont logiquement plus rapides dans certains cas ou plus lents dans d'autres, mais qui augmentent dans tous les cas les performances générales de la mémoire et avec elle le système. Dans la première version appelée par son propre nom, XMP, Intel a réussi à y inclure l'inclusion de la lecture d'un profil en mémoire plus celle du JEDEC (techniquement c'est un profil, mais ils sont comptés comme deux)

XMP 2.0 a élevé le niveau à deux profils de lecture, où les constructeurs pouvaient établir s'ils voulaient deux valeurs et tableaux différents, personnalisant l'expérience utilisateur et privilégiant des performances différentes (trois réels comptant le JEDEC). Avec XMP 3.0, les fabricants peuvent désormais avoir deux ou trois profils à inclure, pouvant en sélectionner deux personnalisés par l'utilisateur.

Mise à jour SPD

L'un des points clés du profil XMP est précisément la Spécification SPD ou Serial Presence Detect . Cela a causé de nombreux maux de tête aux fabricants et aux utilisateurs, principalement parce qu'ils peuvent être écrits à partir de l'EEPROM et donc être corrompus. Certains programmes peuvent le faire et bien sûr, cela crée des plantages dans le contrôleur de mémoire, car il ne peut pas lire correctement les valeurs du XMP et la mémoire est inutilisable jusqu'à ce qu'un nouveau clignotement se produise correctement.

Maintenant et avec XMP 3.0, nous aurons deux profils pouvant être mis à jour, ce qui aide à ce que si l'un est corrompu, l'autre puisse laisser la mémoire fonctionner, son SPD peut être extrait et plus tard il peut être flashé module par module, en réparant la mémoire comme si rien n'avait été passé.

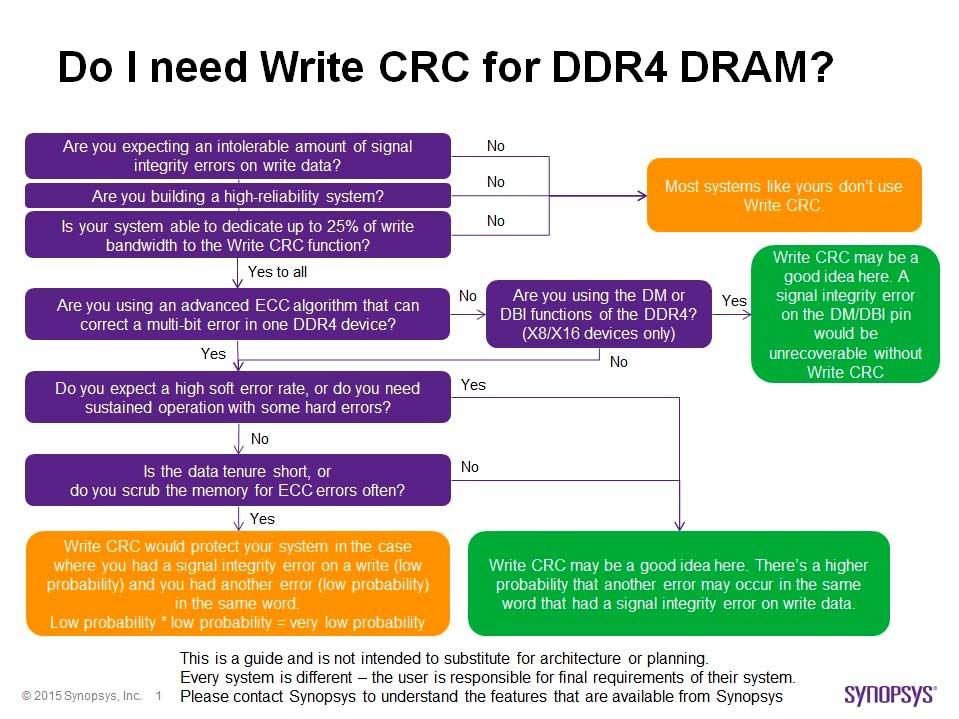

Somme de contrôle CRC

Curieusement et déjà expliqué, pourquoi les modules DDR4 avec XMP 2.0 n'ont-ils pas de CRC ? Ce n'est pas exactement comme ça et logiquement il y a un pourquoi. Le CRC en tant que tel a été ajouté dans sa version Write dans la norme JEDEC pour la DDR4, mais le code de redondance cyclique a un problème : une forte consommation de bande passante. Les données montrent la consommation de 25% de l'écriture totale du système et bien sûr, il n'est pas acceptable de perdre cette quantité de bande passante avec les marges et les vitesses que nous évoluons aujourd'hui.

Ce n'est plus un problème avec la DDR5, puisqu'en plus d'inclure le PMIC dans la mémoire elle-même, dans le module physiquement parlant, les débits sont et seront monstrueux par rapport à la DDR4, surtout si on a une double bande passante qui intègre ce type de mémoire . Par conséquent, Intel avec XMP 3.0 intègre la somme de contrôle CRC recherchée qui protégera les données et l'intégrité du SPD ainsi que le Processeur contrôleur de mémoire.

Plus grande augmentation de l'espace pour XMP 3.0

L'un des aspects clés et comprendre déjà tout ce que nous avons dit sur le nouveau XMP 3.0 est que, logiquement, nous avons besoin de plus d'espace pour abriter tout cela. Par conséquent, Intel est passé de 78 octets par module pour XMP 1.0 à 102 pour XMP 2.0 et l'élève désormais à 384 octets de contrôle pour XMP 3.0.

C'est ce qui permet de sélectionner des profils de mémoire prédéfinis comme SPD à partir du carte mère BIOS/UEFI. La question que l'on se pose alors est le comportement du BMI des nouveaux processeurs Alder Lake et Meteor Lake (un saut de fréquence important est à prévoir) avec les différentes vitesses que l'on va voir de la part des fabricants et des puces.

Allons-nous voir des profils XMP 3.0 au-dessus de 6000 MHz ? L'IMC des CPU peut-il les supporter sans déborder la tension et avec elle la consommation et la dégradation ? Pour le moment, nous savons qu'il existe des marques travaillant sur des profils pour la DDR5-7000, il semble donc que soit ces nouvelles mémoires et puces parviennent à évoluer beaucoup plus rapidement que les CPU et leur IMC, soit cela signifie que le potentiel de téléchargement et de support / l'endurance des contrôleurs de mémoire intégrés est supérieure à ce que l'on pourrait penser.

Il faut garder à l'esprit que bien que XMP 3.0 atteigne des vitesses très élevées dans certains modules, c'est l'IMC qui détermine s'il est capable de supporter ladite vitesse et sa tension, qui est logiquement indépendante de celle de la RAM elle-même.

Ceci dit et clarifié, on ne peut que dire qu'Intel a fait un très grand pas en avant, le plus grand depuis qu'il a lancé XMP en 2007 et à ce titre, c'est désormais AMD qui va devoir adapter sa technologie et IMC à ces nouveaux exigences avec Zen. Quatre.