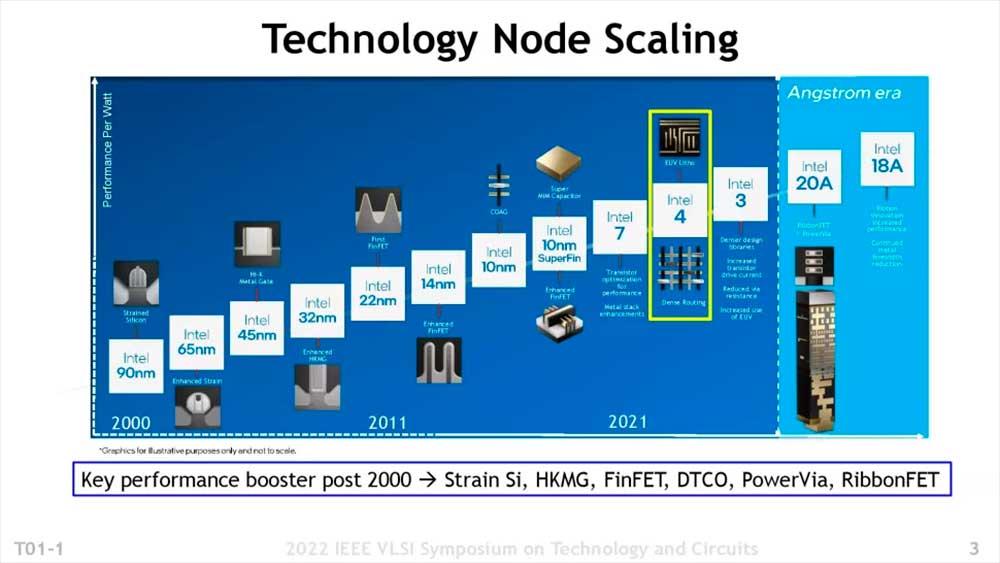

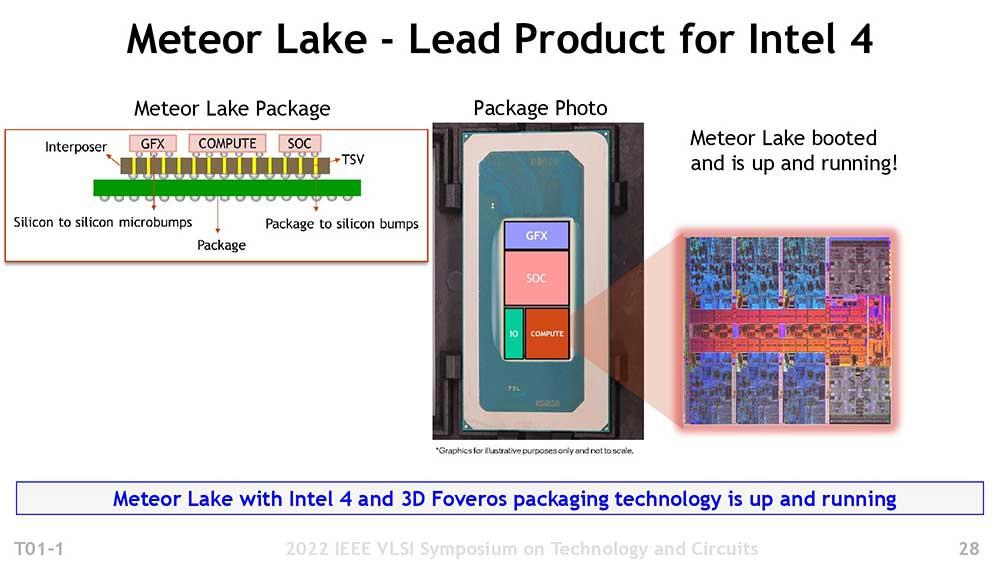

C'était au symposium IEEE VLSI cette année 2022 où Intel a dévoilé le premier procédé lithographique pour puces hautes performances fabriquées par sa société et grâce à des scanners ASML à technologie EUV. Bien que l'entreprise arrive dernière dans cette course, la réalité est qu'elle entre par la porte d'entrée et fait vraiment peur à ses rivaux, surtout si l'on tient compte du fait qu'elle tourne à plein régime. Ainsi est Intel 4 .

Les résultats sont vraiment impressionnants pour un saut de nœud unique et la preuve qu'Intel rivalise avec une réelle infériorité depuis de nombreuses années en raison de retards dans son nœud 10 nm, maintenant appelé Intel 7. De son côté, Intel 4 est un bond en avant. assez intéressant, qui appelle le pari (en retard, oui) et qui remet peu à peu l'entreprise au premier plan.

Cinq nœuds en 4 ans, le pari commence avec Intel 4

Intel 7 a été mis sur le marché davantage en raison de l'investissement réalisé par l'entreprise et du fait que les investisseurs l'avaient à l'œil qu'en raison de ses performances réelles. Il est vrai que cela a été un bond en avant, mais à un prix énorme à tous égards. La solution, tout d'abord du moins, c'est Intel 4 et… C'est très prometteur.

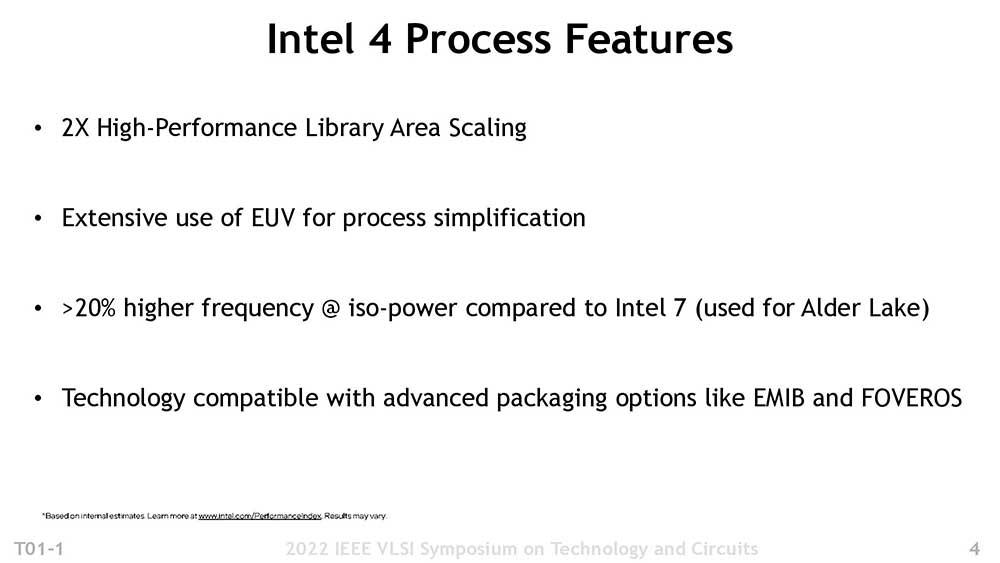

Les améliorations sont très intéressantes et rarement pouvons-nous dire des chiffres comme ceux-ci :

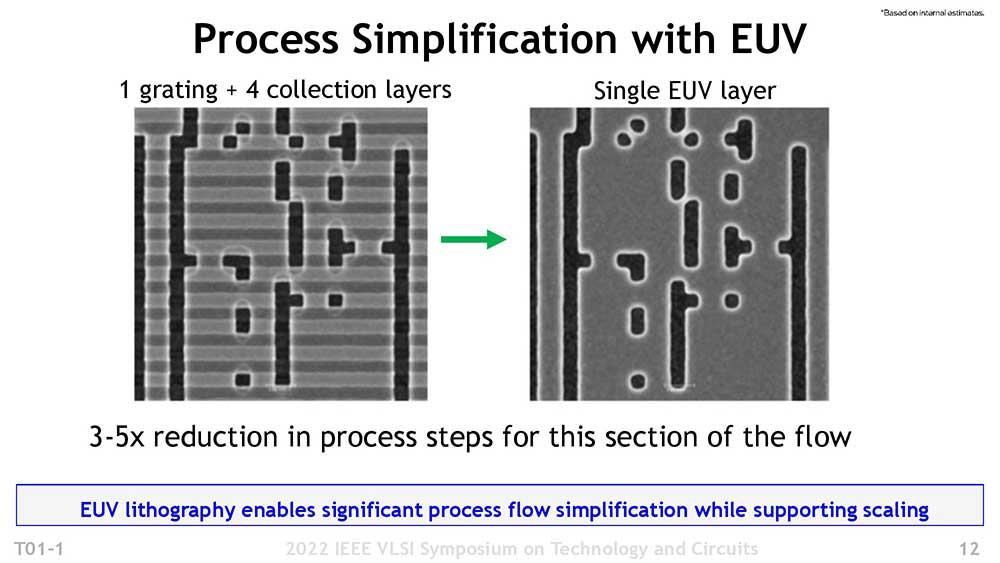

- Première génération Lithographie EUV .

- Saut de fréquence à la même puissance de 21.5% .

- A la même fréquence, la puissance est réduite de 40% .

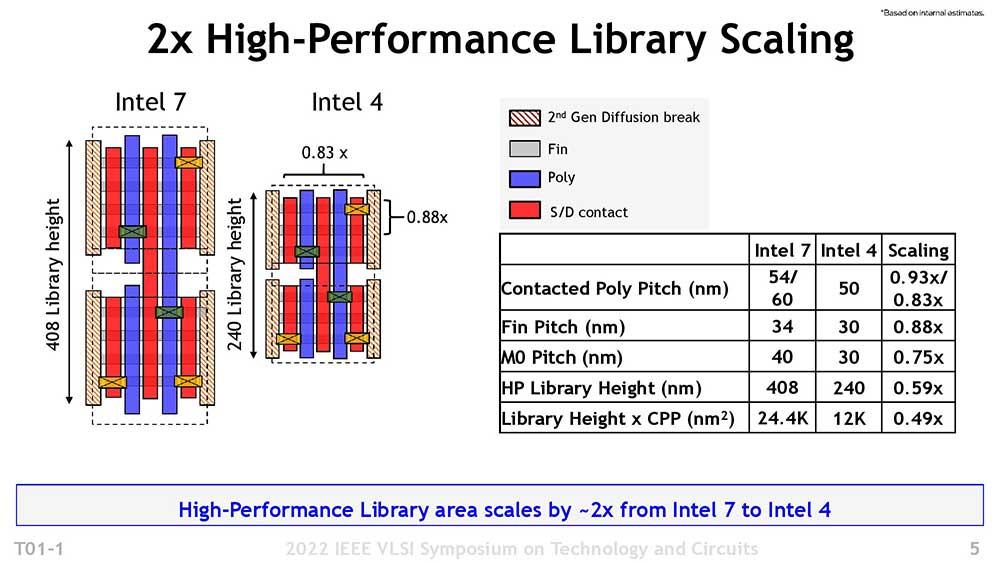

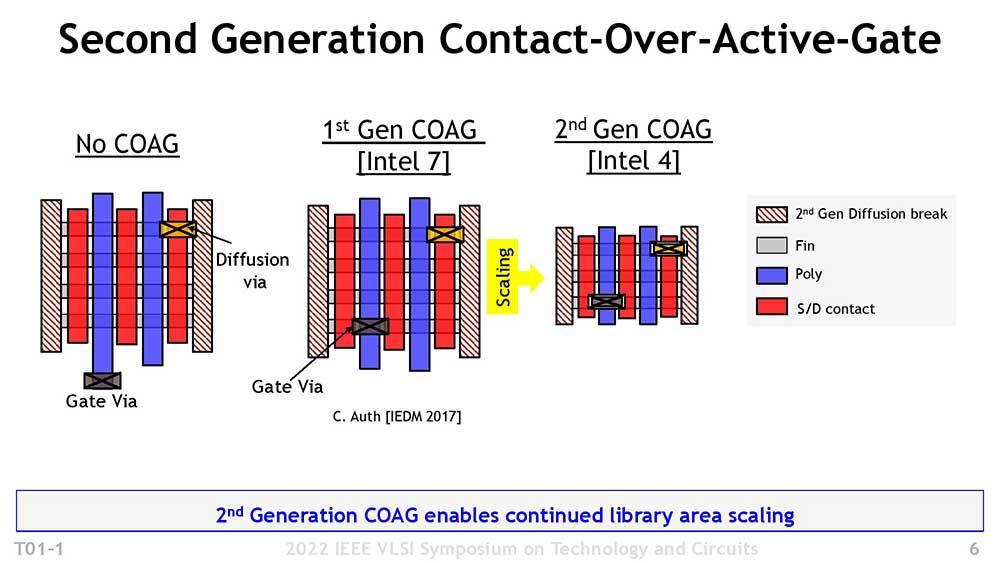

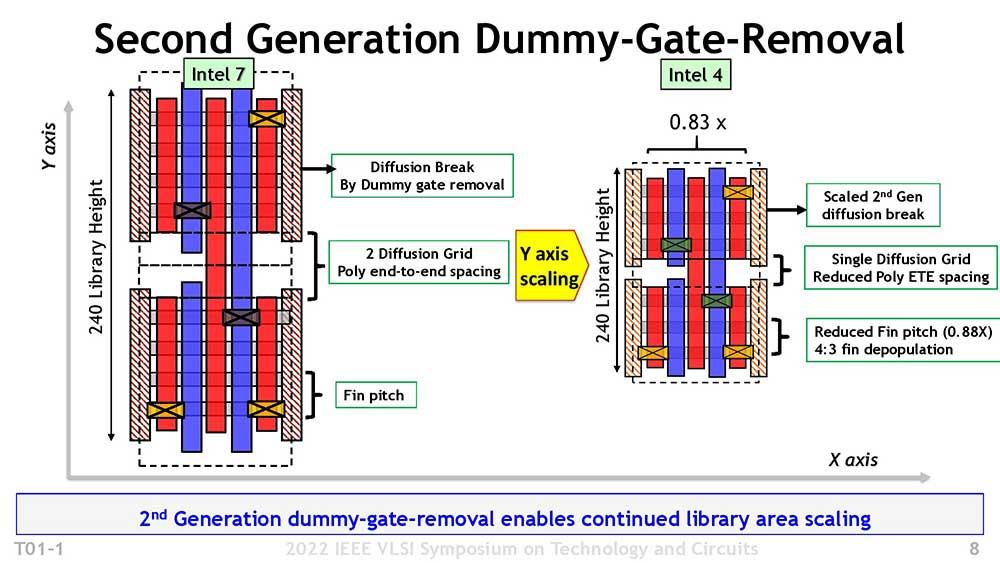

- 2X amélioration de la mise à l'échelle de la zone.

Tout cela contre le procédé lithographique Intel 7 actuel, qui était le plus dense comparativement à son prédécesseur… Jusqu'à présent. En décomposant point par point on comprendra mieux ce qui a été exposé.

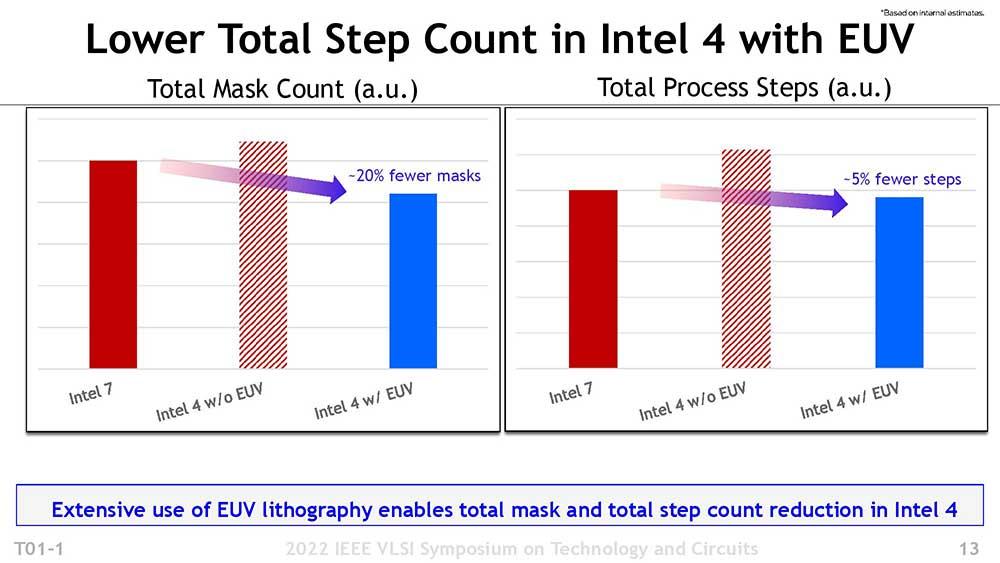

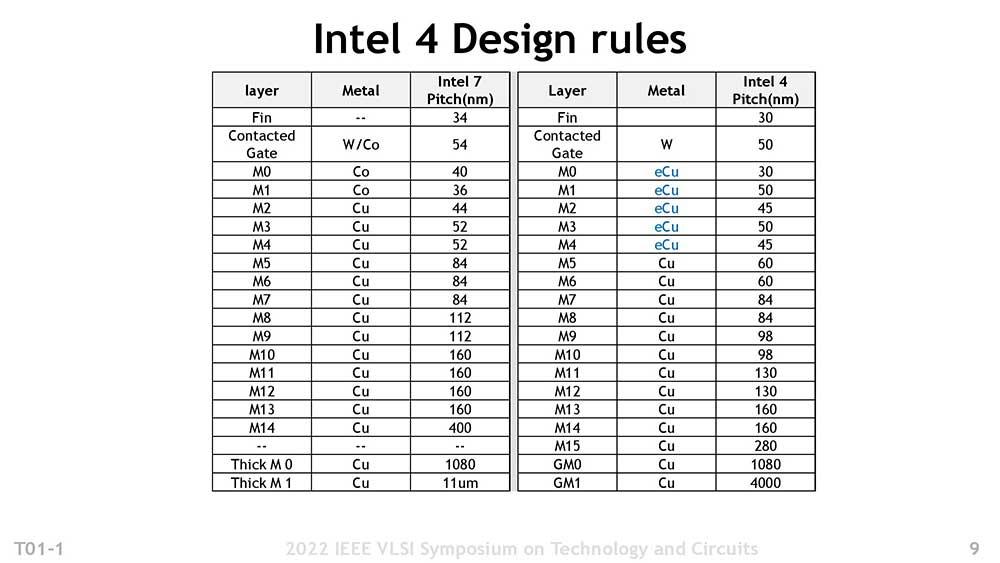

Tout d'abord, la lithographie EUV a été réalisée grâce aux scanners ASML, qu'il a fallu près de deux ans à Intel pour monter en volume afin de générer suffisamment de wafers par heure pour sécuriser suffisamment de puces. Il se compose d'un nombre assez élevé de couches, 18 totale , ce qui est choquant étant donné qu'Intel 7 en possède 17. C'est quelque chose que nous verrons également avec Intel 3 dans le même sens, mais pour le moment il n'y a pas de données.

Le saut de fréquence est le plus intéressant, puisque ni TSMC ni Samsung avec EUV ont atteint des valeurs similaires et si nous l'extrapolons au Core 12 actuel, nous aurions des fréquences de 6.6 GHz dans le futur Core 14, des chiffres fous dont on ne sait pas même s'ils sont réalisables et compatibles en ces termes avec l'architecture, où en tout cas il y aura une augmentation sans aucun doute.

Si Intel opte pour l'efficacité, le résultat peut être un succès dans le bas de gamme

Et c'est qu'Intel crée normalement deux bibliothèques pour chaque nœud : une de haute densité et une autre de haute performance. Dans le cas d'Intel 4, cela va entraîner une certaine tournure des événements, car les bibliothèques pour la haute densité ne sont apparemment pas disponibles sur ce nœud, donc seules les hautes performances restent en tant que telles.

Cela dit, dans les hautes performances, nous pouvons trouver, techniquement parlant, deux approches nommées ci-dessus : exposer la fréquence maximale disponible, exposer le nœud à son efficacité maximale. Si Intel opte pour les deux approches en segmentant la gamme, on pourrait se retrouver avec des processeurs rapides et, surtout, très économes en énergie, ce qui serait très intéressant pour les portables de jeu et les ordinateurs de travail à bas prix, car si à 5.5 GHz ils parviennent à baisse de 40% la consommation on parlerait d'un Core i9-12900KS avec à peine 125 watts en plein, des chiffres désormais impensables.

| Intel 4 | Intel 7 | TSMC-N5 | TSMC N3 | |

| Densité de bibliothèque HP | 160MTr/mm^2 (estimation) | 80MTr/mm^2 | 130MTr/mm^2 (estimation) | 208 MTr/mm^2 (estimation) |

| Densité de la bibliothèque HD | Aucun prévu | 100MTr/mm^2 | 167 MTr/mm^2 (estimation) | 267 MTr/mm^2 (estimation) |

| Densité logique | 2x | 2.7x | 1.83x | 1.6x |

| Perf (puissance iso) | 1.2X | 1.15x | 1.15x | 1.11x |

L'amélioration de la mise à l'échelle de la zone est le calcul technique de tout ce qui a été dit. Et c'est que la librairie HP (High Power) affiche actuellement une densité de 160 MT/mm2 (il pourrait encore être amélioré dans quelques millions de transistors, mais pas beaucoup), où la densité augmente jusqu'à 2X si l'on tient compte du fait qu'Intel 7 était à 80 MT/mm2, avec un rendement iso de 1.2X .

Son rival direct est le TSMC N5 et dans une moindre mesure le Samsung N3 déjà avec GAA