L'annonce du processus 2 nm par IBM est une démonstration que le matériel continuera à évoluer au cours des 5 prochaines années comme il l'a toujours fait et en continu, mais à son tour, ladite annonce génère une série d'inconnues puisque le nombre de nanomètres pendant une longue période le temps correspond plus au marketing qu'à la réalité physique.

Cette semaine, nous avons vu l'annonce du nouveau nœud de fabrication IBM. Que peut-on attendre de ce nœud et quel sera le saut par rapport aux nœuds actuellement utilisés pour la fabrication de différentes puces et mémoires ?

Comparaison du nœud 2 nm d'IBM avec les nœuds actuels

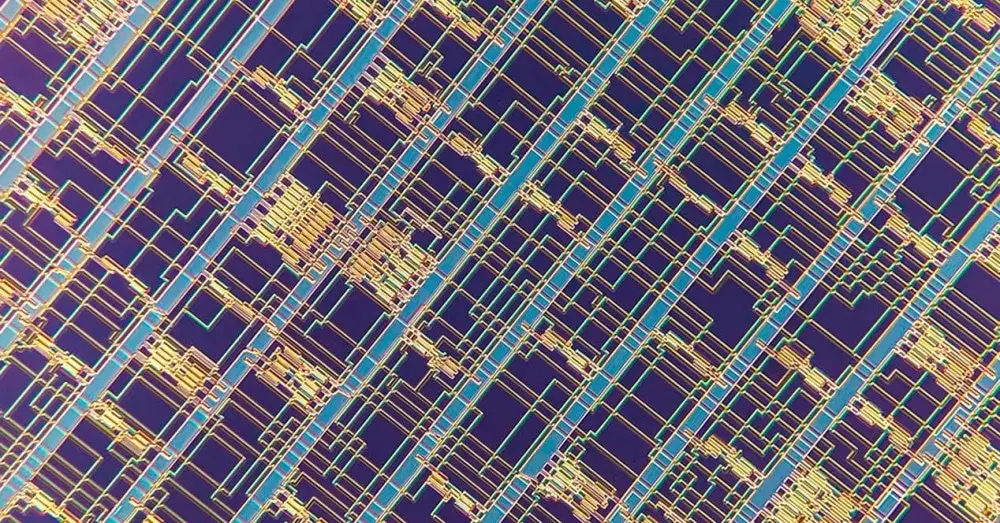

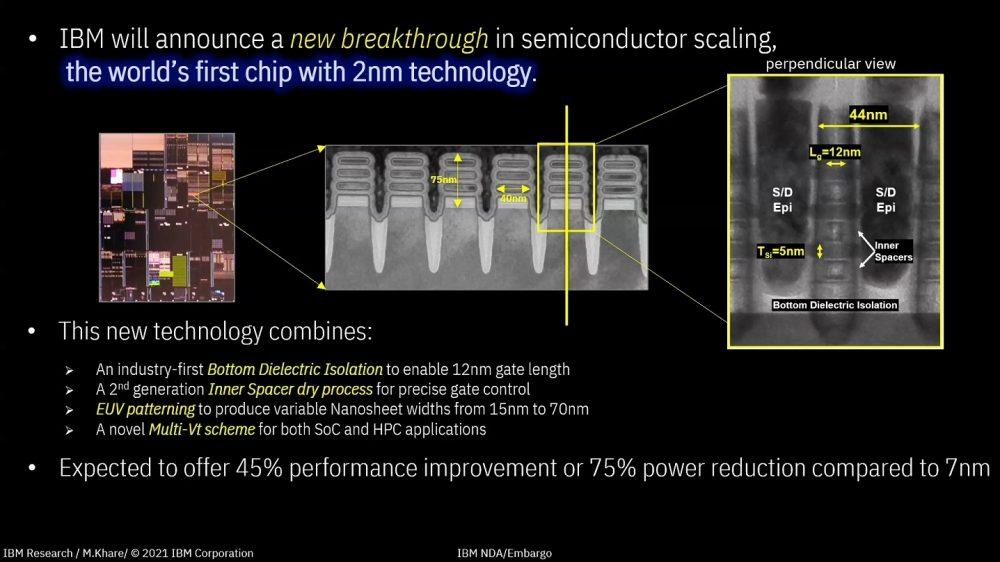

L'échantillon de puce qui a été fabriqué avec le nœud 2 nm d'IBM a une densité de 333 millions de transistors par millimètre carré. Gardez à l'esprit que la densité des transistors dépend de ce qui est construit avec eux et que la mémoire est beaucoup plus dense que la logique, donc toutes les zones du processeur fabriquées par IBM dans son nœud expérimental de 2 nm n'ont pas une telle densité. Dans tous les cas, mesurer la densité à partir de ce que la SRAM occupe dans chaque nœud est normal dans ces cas.

L'actualité est importante face à une situation dans laquelle la loi de Moore semble ralentir de plus en plus et avec le sentiment général qu'un nœud va être atteint qu'en termes de coûts de développement, de déploiement ou de limitations physiques ne permet pas aux puces de être mis à l'échelle plus loin. .

En réalité nous sommes face à un nœud donc il faut attendre 2024 ou 2025 au moins pour sa mise sur le marché.

Sont-ils vraiment 2 nm ?

La densité de nœuds de 7 nm de TSMC est de 96.5 millions de transistors par millimètre carré. Il faut tenir compte du fait que la densité des transistors augmente quadratiquement avec la diminution de leur taille. Par exemple, pour doubler la densité d'un nœud, il suffit de multiplier la taille par 0.7. Par exemple, si nous prenons celui de 7 nm, nous n'avons qu'à multiplier cette taille par 0.7, ce qui nous donne un nœud de 4.9-5 nm.

Mais regardons-nous vraiment un nœud de 2 nm ? Pour connaître la densité qu'aurait un hypothétique futur nœud, il suffit de faire le calcul suivant :

Facteur d'échelle du nœud à convertir en = (1 / nœud connu) ^ 2

Ensuite, nous n'avons plus qu'à faire ce qui suit :

Densité de transistors du nouveau nœud = Densité de transistors du nœud connu / Facteur d'échelle du nœud vers lequel il est prévu de convertir.

Avec la première formule, nous obtenons un facteur d'échelle de 0.08, ce qui indique qu'un nœud hypothétique « réel » de 2 nm aurait une densité de près de 1200 millions de transistors par millimètre carré. Presque quatre fois plus que celui annoncé par IBM, mais il faut aussi ajouter à cela que le 7 nm de TSMC n'est pas vraiment exactement 7 nm, mais une densité bien plus faible et donc un nœud bien plus élevé en nanomètres réels.

Comment se compare-t-il au reste des nœuds existants ?

La raison pour laquelle on l'appelle nœud 2 nm est que sa densité est supérieure aux nœuds 3 nm annoncés par Samsung et TSMC. Dans le cas de Samsung, la densité annoncée pour son nœud 3 nm est de 180 millions par millimètre carré, tandis que le processus 3 nm de TSMC a une densité annoncée de 315 millions.

La raison pour laquelle IBM appelle son nœud "2 nm" est simplement parce que ses spécifications sont bien supérieures à celles de TSMC et Samsung. Maintenant, nous allons voir les arguments pour cela.

Vitesse et consommation électrique des nœuds IBM 2 nm

Un autre point important est la façon dont les processeurs évoluent en vitesse et en consommation, c'est-à-dire si nous fabriquons une puce existante sous le nouveau nœud. À quelle vitesse atteindrait-il ou comment la consommation serait-elle réduite ? Les deux en même temps ne peuvent pas être, donc les deux chiffres sont donnés séparément.

Un processeur fabriqué sous le nœud 7 nm de TSMC, sous le nœud 2 nm d'IBM irait 45% plus vite en vitesse d'horloge pour la même consommation. Alors que si nous maintenions la vitesse d'horloge, la consommation d'énergie chuterait à 75%.

La vitesse d'horloge, cependant, a une astuce, puisque le point exact de la courbe de tension et de vitesse d'horloge qui est le plus élevé est toujours recherché. Il en va de même pour le consommateur, où il semble qu'IBM ait obtenu un meilleur nœud du point de vue de l'énergie consommée.

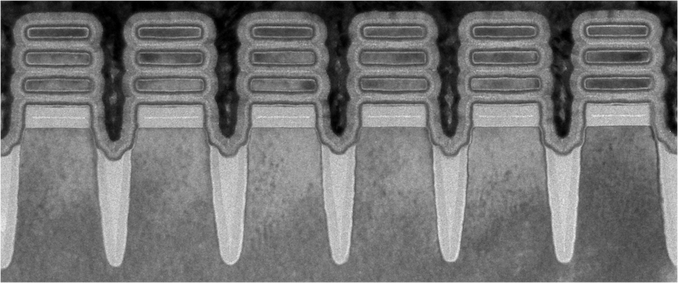

C'est dans la plus haute efficacité énergétique que le nœud IBM 2 nm reçoit son nom, et cela est dû à l'utilisation de ce qu'on appelle HNS ou Horizontal Nanosheets, une technologie qui Intel utilisera dans son nœud de 5 nm, qui rivalisera de votre visage vers les nœuds de 3 nm de Samsung et TSMC. Nous savons que Samsung les adoptera à l'avenir mais nous ne savons pas si TSMC le fera ou s'ils opteront pour une autre solution.

La joint-venture entre IBM et Intel

Oui, cette affirmation peut vous paraître très choquante, mais il faut garder à l'esprit qu'IBM, contrairement à Intel, n'a pas ses propres fonderies, mais qu'elle conçoit des puces et, surtout, investit beaucoup dans la conception de nouvelles fabrications de puces. nœuds qu'il concède sous licence à des tiers. C'est donc un modèle commercial différent de celui de TSMC, Samsung et Intel.

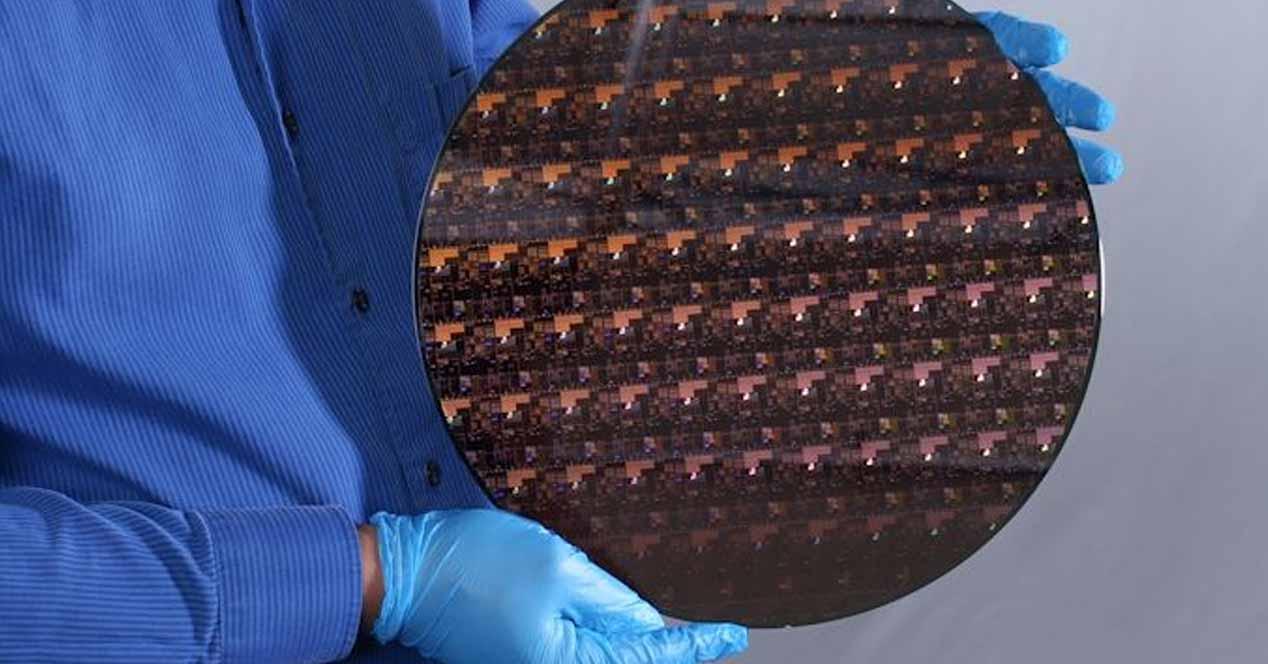

C'est-à-dire que ce qu'IBM a fait, c'est concevoir les normes d'un nouveau nœud de fabrication, puis il a créé un échantillon de puce, qui est une conception qui rassemble tous les éléments communs dans la conception d'un processeur contemporain et a recréé en utilisant une version expérimentale de son nœud de 2 nm.

IBM a régulièrement travaillé avec GLOBAL FOUNDRIES, mais ils ont complètement abandonné la course et n'ont pas atteint le 7 nm. Le partenaire d'IBM dans ce cas est donc Intel et nous examinons peut-être les spécifications d'un futur nœud Intel.

De plus, il est possible que nous soyons confrontés aux spécifications du nœud 5 nm d'Intel, avec lequel ils résisteraient aux nœuds 3 nm de TSMC et Samsung dont nous avons discuté plus tôt dans cet article.