L'arrivée future des processeurs à base de chipsets entraîne une question: quelles interfaces et quels protocoles seront utilisés pour communiquer les différents éléments d'un chipset entre eux. Bien qu'il y en ait plusieurs différents et un pour chaque marque, l'E / S électrique commune dans deux de ses variantes est l'interface de communication qui sera utilisée pour la communication des chiplets au-dessus d'un interposeur.

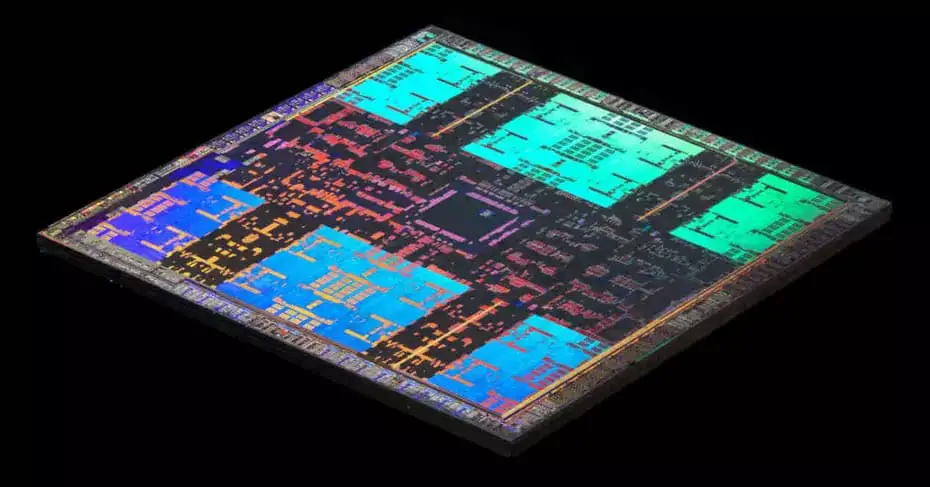

Il ne fait aucun doute que les processeurs composés de puces seront la norme dans les années à venir, on sait que ce sera le pari des futurs designs des deux Intel, AMD et NVIDIA, dans lequel chacun d'eux a développé une interface propriétaire de communication à utiliser avec vos architectures.

L'interface électrique commune, en revanche, est l'interface qui est normalisée pour la communication entre les éléments d'un chiplet et qui n'appartient pas à ces trois sociétés. De plus, de nombreuses conceptions sont des unités FPGA construites qui utilisent cette interface pour communiquer les différentes parties. Bien qu'avant d'expliquer en quoi il consiste, il est préférable de faire un tour à travers une série de concepts de base.

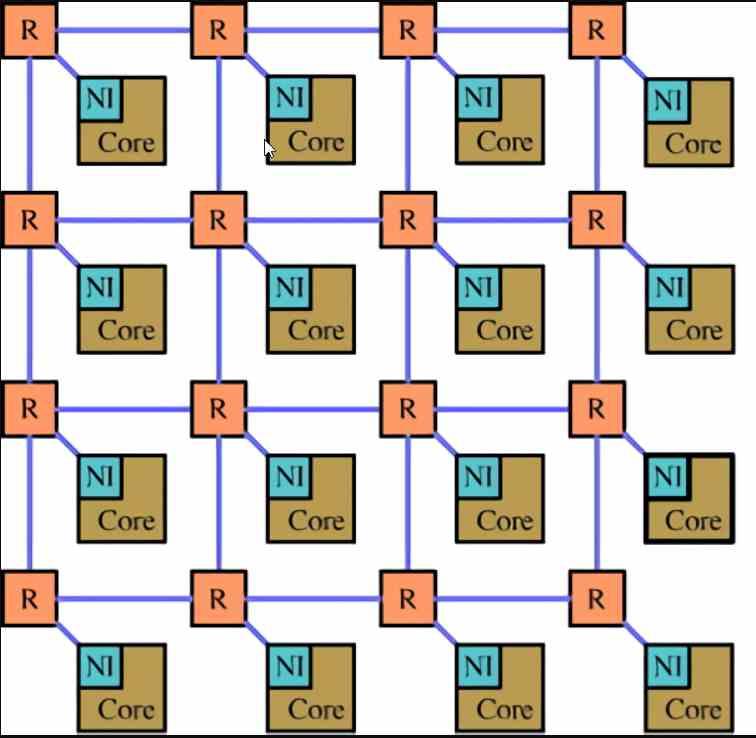

Le concept de NoC

NoC ou réseau sur puce, c'est l'idée de faire une intercommunication entre les différents composants du PC comme s'il s'agissait d'un réseau, pour cela chacun des éléments dispose d'un routeur qui le communique avec les autres éléments, donc seulement Il est nécessaire que chaque élément du réseau a un routeur intégré qui est utilisé pour communiquer et communiquer avec le reste

Chaque élément du réseau de composants a sa propre adresse et la façon de communiquer entre les différents composants consiste à faire appeler chaque élément l'adresse réseau d'un autre élément, dans lequel non seulement les éléments de traitement ont une adresse dans le même, pas seulement les processeurs. et les interfaces d'E / S, mais aussi les mémoires qui le composent, que ce soit RAM, VRAM et même puces NVMe afin de faciliter la communication.

L'idée d'un MCM comme NoC

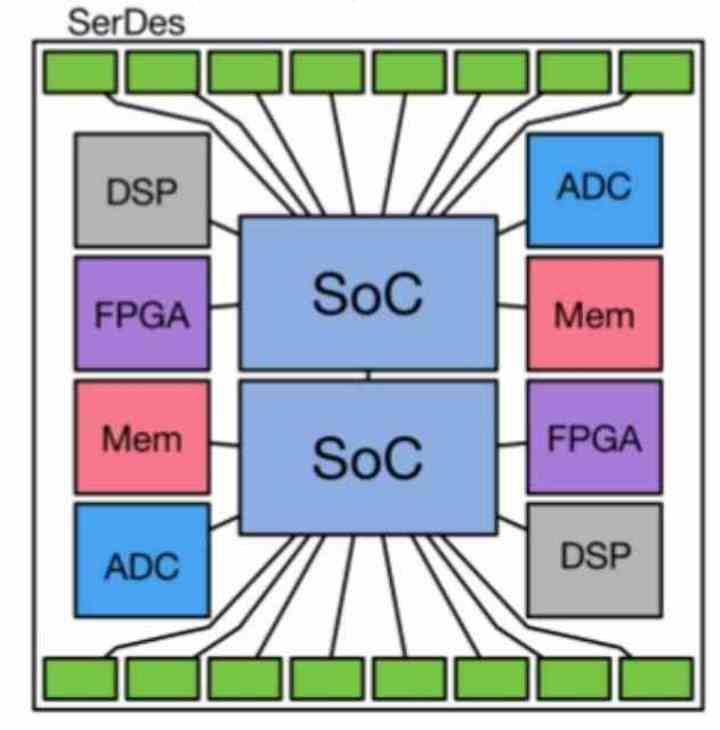

Quelque chose qui différencie un SoC d'un MCM est que dans le premier cas, nous avons une unité centrale sur la puce qui est chargée de communiquer entre eux tous les éléments de la puce et ceux-ci avec la mémoire sont communs à tous les SoC, indépendamment de quelle que soit l'architecture dont nous parlons, tous les SoC contiennent cet élément en commun.

Mais dans un MCM composé de plusieurs éléments séparés, il doit également y avoir une unité chargée de communiquer les différents éléments entre eux. Si nous parlons d'un SoC alors il doit y avoir la même unité en charge de la communication, mais dans le cas où nous parlons d'un NoC dans lequel chaque élément peut communiquer directement avec un autre, les choses changent déjà.

Dans un NoC, la communication est effectuée entre les différents éléments à l'aide d'une interface réseau, imaginez cela comme un réseau LAN, mais en utilisant des connexions beaucoup plus rapides pour la communication entre les différents éléments du chiplet, en raison de la courte distance et du matériel utilisé.

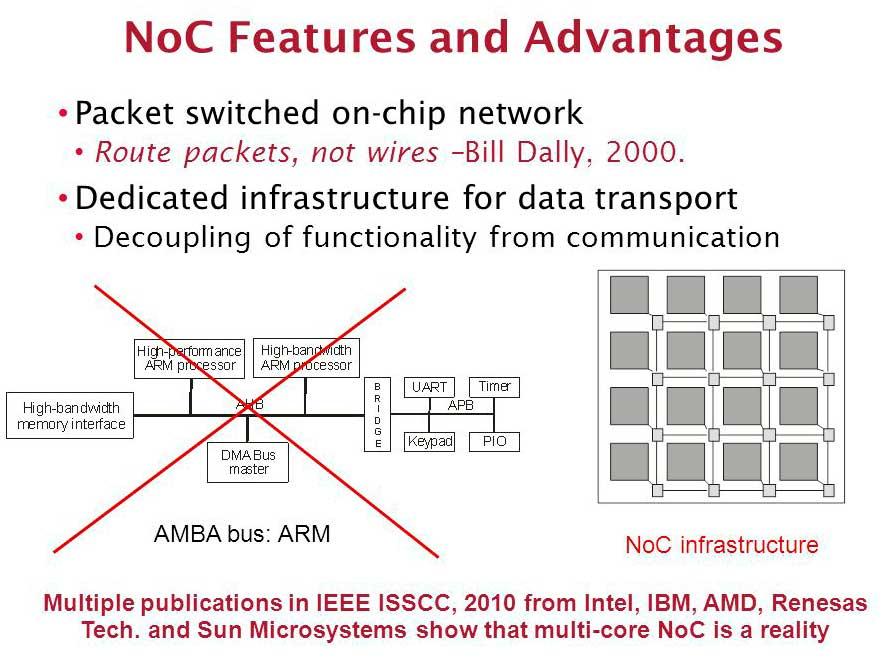

Qu'est-ce que les E / S électriques communes?

La E / S électriques communes abrégé en CEI, est une série d'accords conclus par un consortium appelé Optical Internet Working Forum (OIF), qui est chargé de définir les exigences communes pour les interfaces électriques avec une vitesse de communication avec une vitesse de transfert de 3,125, 6, 11, 25 -28 et 56, 112 et bientôt 224 Gbps.

Le CEI a été à la base de différents types d'interfaces d'E / S et de protocoles tels que l'Hyper Transport dont dérive Infinity Fabric d'AMD, l'interface SATA dans plusieurs de ses versions. diverses interfaces 803.3 et InfiniBand.

Son importance est due au fait qu'Intel et AMD utiliseront leurs propres interfaces propriétaires pour communiquer les différents chipsets au sein du MCM, mais l'existence d'une interface standard utilisable est extrêmement importante non seulement pour déployer des conceptions basées sur des chipsets. . par différents concepteurs de processeurs, mais aussi pour le développement de ceux-ci.

L'E / S électrique commune est une interface de type SERDES, qui dans sa version actuelle peut atteindre une vitesse de transfert de 112 Gbps. Il a actuellement différentes variantes, mais celles qui nous intéressent sont celles liées aux chiplets, puisqu'elles seront largement utilisées pour la communication entre les différents éléments.

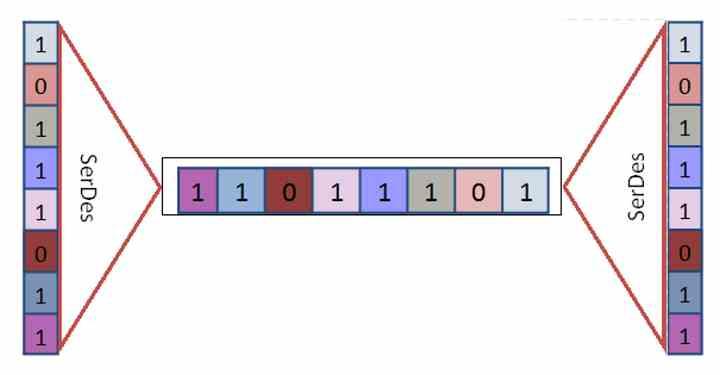

Un SERDES est un type d'interface qui prend une série de données en parallèle et la transmet en série à une autre, car il fera le processus inverse, c'est-à-dire qu'il convertit à nouveau un signal série en un signal parallèle. D'où la dimension SERDES.

Dans le cas de l'interface actuelle de 112 Gbps, il utilise un codage de type PAM4, de telle sorte qu'il puisse atteindre 112 Gbps de vitesse en utilisant une vitesse d'horloge de 28 GHz pour la communication. De telles vitesses d'horloge seraient extrêmement contre-productives si l'on parle de longues distances, mais ce n'est pas le cas d'un MCM composé de chiplets avec un interposeur en dessous, dans lequel les différents éléments sont trop proches pour communiquer.

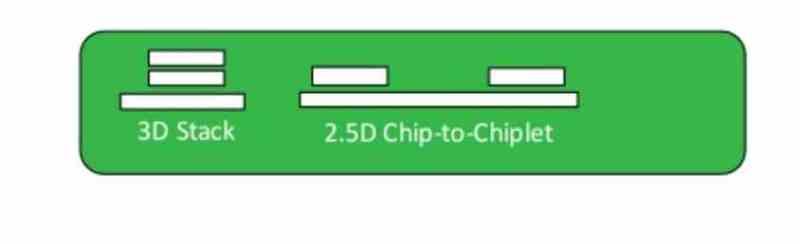

Dans l'interface d'E / S électrique commune, nous avons deux types, d'une part, nous avons celui qui est responsable de la communication dans un chiplet traditionnel, qui dans sa version 112 Gbit / s s'appelle CEI-112G-MCM et est conçu pour être câblé avec une distance entre les deux extrémités d'au plus 2.5 mm, la courte distance du câble lui permet de consommer très peu d'énergie par transfert.

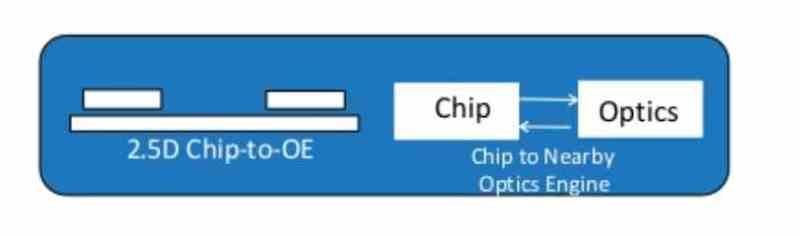

Le deuxième type est conçu pour la communication avec un récepteur optique, et oui, la prochaine étape après les interposeurs conventionnels consiste à utiliser des interfaces optiques pour la communication, même si pour le moment elles ne sont ni utilisées ni utilisées à court terme dans les systèmes domestiques.

E / S électriques communes pour la communication externe des puces

Un chiplet, bien qu'il soit composé de différentes unités à l'intérieur, peut être considéré comme une seule unité tournée vers l'extérieur et la façon dont il communique se fait via une série d'interfaces d'E / S qui fournissent la connectivité.

Bien entendu, pour la communication au sein du chiplet, ce type d'interfaces externes doit être transformé en un signal de type Common Electrical I / O, à travers une série de SERDES proches de la périphérie de la puce. juste avant les interfaces externes, qu'il s'agisse des interfaces RAM, VRAM, PCI Express, etc.