Le concept de Cache DRAM consiste à ajouter un niveau supplémentaire de cache entre le processeur et le RAM mémoire afin d'augmenter les performances du premier. Mais qu'est-ce que cela change dans l'architecture d'un processeur et comment fonctionne ce concept? Nous vous l'expliquons et accessoirement quels processeurs utiliseront cette architecture.

Il y a quelques jours un Apple un brevet est apparu dans lequel l'utilisation de Cache DRAM dans l'un de ses futurs processeurs a été mentionnée, un concept qui, bien que cela puisse paraître exotique, ne l'est pas, nous allons donc le démystifier.

La mémoire DRAM comme cache, une contradiction

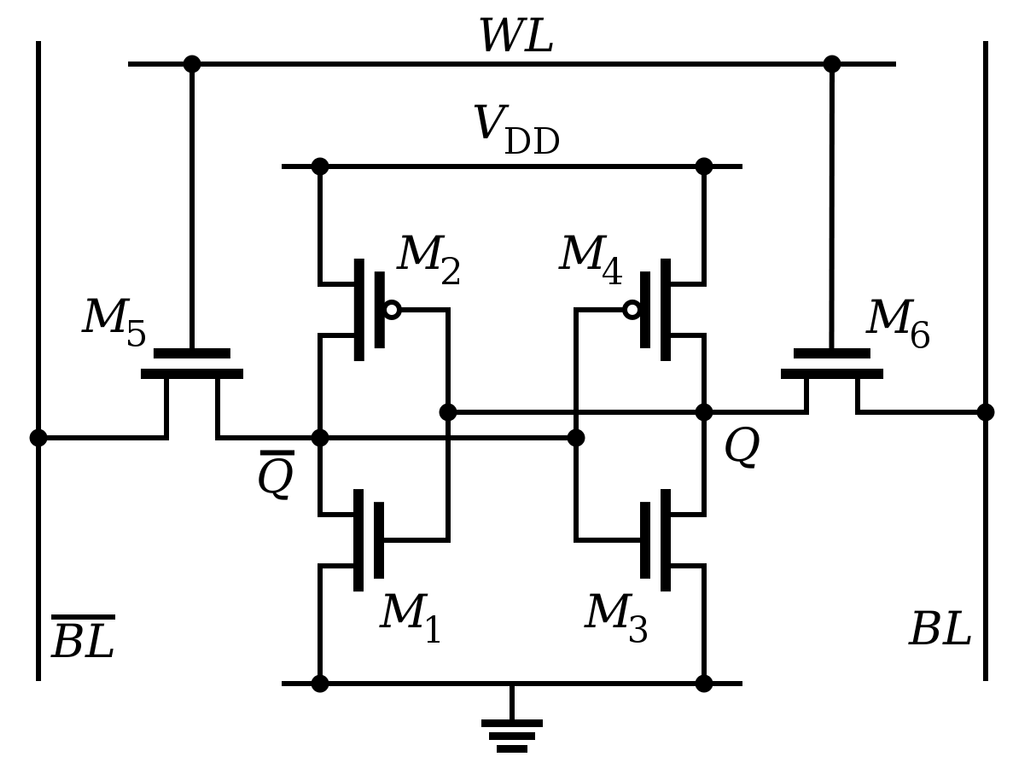

Toutes les mémoires RAM actuelles qui sont utilisées en dehors d'un processeur sont de type DRAM ou Dynamic RAM, tandis que les mémoires utilisées à l'intérieur des processeurs sont de la RAM statique ou de la SRAM. Les deux fonctionnent à peu près de la même manière en termes d'accès aux données, mais ce qu'ils ne sont pas les mêmes, c'est la façon dont ils stockent un peu de mémoire.

La mémoire DRAM est beaucoup moins chère, mais de par sa nature, elle nécessite un rafraîchissement constant, et sa vitesse d'accès est plus lente que la SRAM, elle n'est donc généralement pas utilisée dans les processeurs. D'un autre côté, il évolue d'une manière pire que la DRAM, donc malgré le fait qu'IBM utilise la mémoire DRAM comme cache de dernier niveau dans ses processeurs pour le calcul haute performance, POWER, dans sa prochaine génération, ils utiliseront la SRAM. Mémoire.

Ainsi, le concept de cache, qui est lié à une mémoire de type SRAM, ainsi que le concept de DRAM en principe ne correspondent pas et bien que nous ayons le cas des CPU IBM, nous n'allons pas parler d'utiliser la mémoire DRAM comme cache dans le processeur.

Cache DRAM et mémoire HBM à titre d'exemple

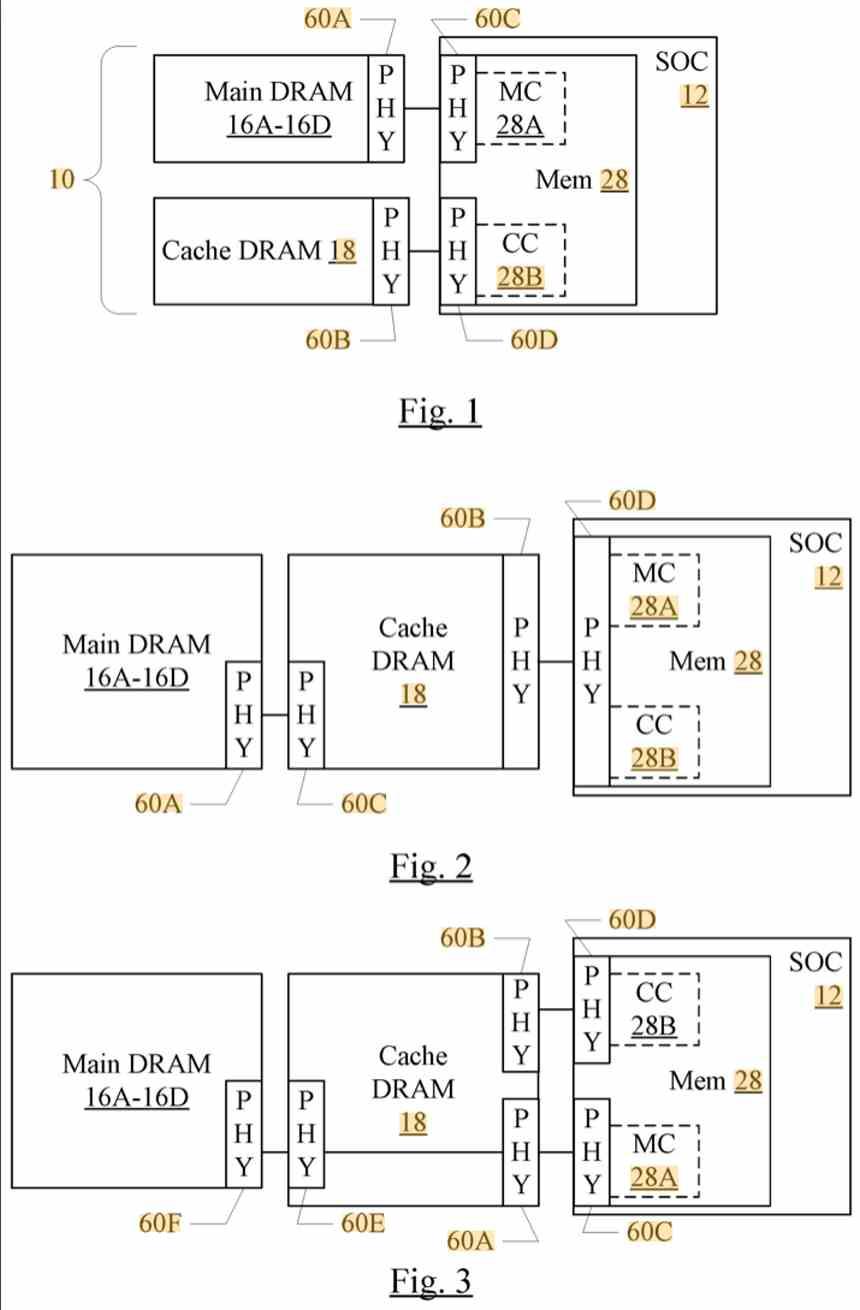

Cache DRAM est le concept d'ajouter une couche supplémentaire dans la hiérarchie de la mémoire entre le cache de dernier niveau du processeur et la mémoire système principale, mais construit à travers une mémoire DRAM avec une vitesse d'accès plus élevée et moins de latence que la DRAM utilisée comme mémoire principale.

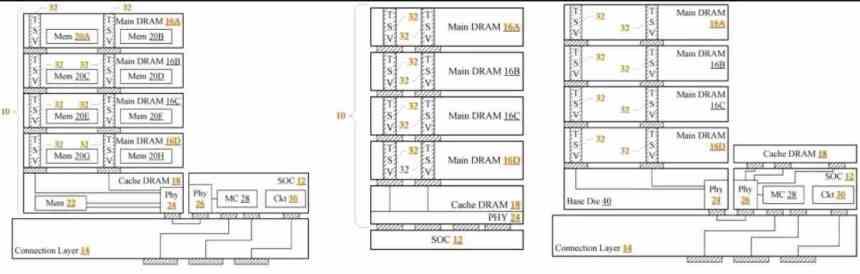

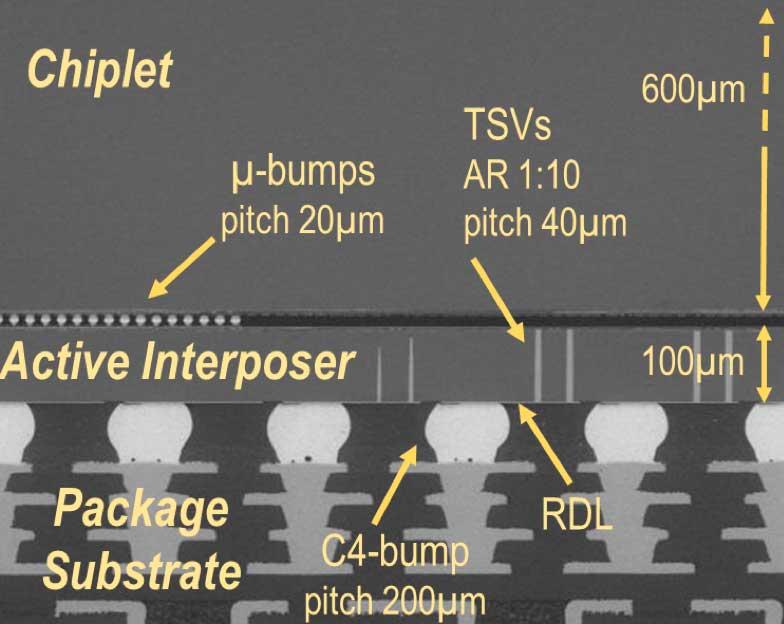

Une façon d'y parvenir consiste à utiliser une mémoire de type HBM comme cache DRAM, qui est un type de mémoire DRAM dans laquelle différentes puces de mémoire sont empilées et connectées verticalement à l'aide d'un type de câblage appelé TSV ou through-path. silicium par le fait qu'ils traversent les puces. Ce type de connexion est également utilisé pour la construction de mémoire 3D-NAND.

Parce que la connexion est verticale, un interposeur est nécessaire, qui est un élément électronique sous la forme d'une carte qui est responsable de la communication du processeur et de la mémoire HBM. Le processeur, que ce soit Processeur or GPU, sont montés sur ledit interposeur, ce qui, en raison de la courte distance, donne à la mémoire HBM la capacité de fonctionner comme un type de mémoire DRAM avec une latence plus faible que les mémoires DDR et GDDR classiques.

Il faut préciser que si la DRAM était plus proche du processeur, comme une configuration 3DIC la place juste au-dessus, alors le niveau de latence par rapport à la mémoire HBM serait plus faible et donc la vitesse d'accès plus élevée, du fait que les électrons ont pour parcourir une distance plus courte.

Nous avons vraiment utilisé la mémoire HBM pour vous donner une idée, mais tout type de mémoire dans une configuration 2.5DIC fonctionne comme un exemple.

Mais un interposeur standard ne suffit pas

Le problème suivant est qu'un cache ne fonctionne pas de la même manière qu'une mémoire RAM, car le système de recherche de données du processeur ne copie pas les lignes d'instructions de la RAM une par une, mais plutôt le système de mémoire. Ce que fait le cache, c'est copier le fragment de mémoire où la ligne de code actuelle se trouve dans le dernier niveau du cache.

Le dernier niveau stocke le cache d'un processeur est partagé par tous les cœurs, mais à mesure que nous nous rapprochons du premier niveau, ceux-ci sont plus privés. Il convient de préciser que dans l'ordre décroissant, chaque niveau de cache contient un fragment du cache précédent. Lorsqu'un processeur recherche des données, il les recherche dans l'ordre croissant des niveaux de cache, où chaque niveau a plus de capacité que le précédent.

Mais, pour que la mémoire HBM se comporte comme un cache, alors nous avons besoin de l'élément qui communique le processeur avec ladite mémoire, l'interposeur, pour avoir les circuits nécessaires pour se comporter comme une mémoire cache. Ainsi, un interposeur conventionnel ne peut pas être utilisé et il est nécessaire d'ajouter des circuits supplémentaires dans l'interposeur qui permettent à la mémoire HBM de se comporter comme un cache mémoire supplémentaire.