Avec l'annonce cette semaine du premier Apple Macintosh basé sur des processeurs avec ISA BRAS, après avoir annoncé la transition par Apple il y a quelques mois, le sujet ARM vs x86 est apparu et la question de savoir pourquoi il n'y a pas de CPU avec ISA x86 sur les appareils basse consommation a réapparu. Mais quels sont les motifs et les mythes entourant cette question?

Si vous vous êtes déjà demandé pourquoi vous ne pouviez pas voir les smartphones, les tablettes et toutes sortes d'appareils utilisant des processeurs x86 avec une consommation inférieure à 10 W et même 5 W.Alors laissez-nous vous dire que ce n'est pas dû à un manque d'intérêt pour Intel or AMD, mais il y a un certain nombre de raisons à cela, une série de barrières insurmontables qui ont à voir avec la nature de l'architecture x86.

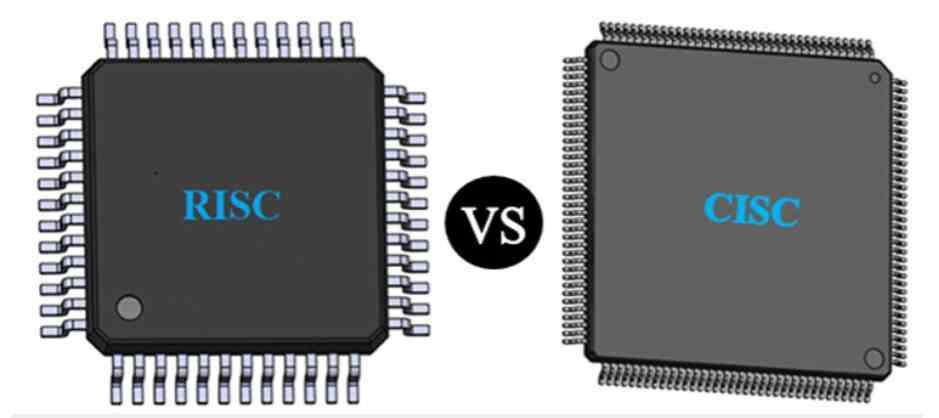

ARM vs x86 ou CISC vs RISC

ARM signifie Advanced RISC Machines, tandis que chaque système x86 Processeur est dit avoir un jeu d'instructions de type CISC. mais qu'est ce que ça veut dire? RISC signifie Reduced Instruction Set Computing ou Computing with a Reduced Instruction Set, tandis que CISC signifie Complex Instruction Set Computing, c'est donc un moyen de classer les jeux d'instructions utilisés par différents processeurs.

La principale différence est que, comme RISC a un ensemble d'instructions réduit, il finit par être nécessaire d'utiliser plusieurs instructions plus simples pour en exécuter une plus complexe, alors que dans le cas d'une unité CISC, de nombreuses instructions complexes peuvent être exécutées en une seule instruction. , donc les lecteurs CISC économisent de l'espace en termes de quantité de mémoire.

Par exemple, le code machine d'une somme dans RISC serait le suivant:

- Stocke le premier opérande dans le registre de l'accumulateur

- Chargez le deuxième opérande et effectuez l'addition.

- Stocke le résultat dans le registre de l'accumulateur.

Au lieu de cela, sur un processeur CISC:

- Ajoutez le premier et le deuxième opérande.

Quant au code machine, un RISC binaire a plus d'instructions et donc prend beaucoup plus de mémoire , tandis que dans le binaire CISC, le code est beaucoup plus léger.

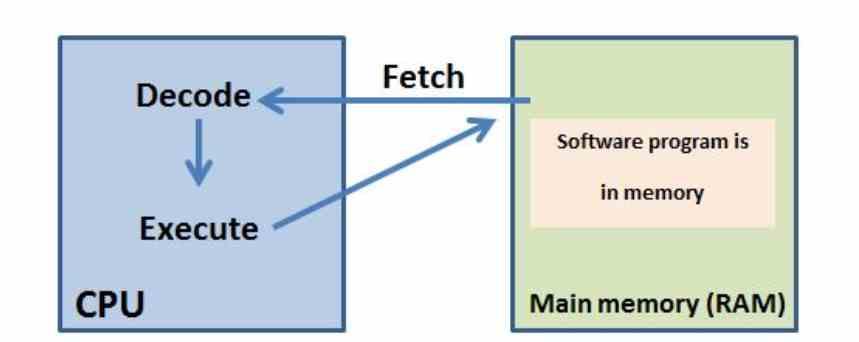

Le cycle d'instruction des processeurs

Chaque processeur, qu'il s'agisse de CISC ou RISC, doit passer par quatre étapes différentes qui sont:

• Récupérer: L'instruction suivante est récupérée en mémoire.

• Décoder: L'instruction est décodée et préparée pour l'exécution.

• Exécuter: L'instruction est exécutée par l'une des unités d'exécution de la CPU. et le résultat de l'instruction est écrit dans la banque de mémoire ou le registre correspondant.

In Processeurs RISC une instruction exécutée par la CPU équivaut à une instruction en code binaire, tandis qu'en CISC une instruction en code machine peut être décomposée en plusieurs micro-instructions, ce qui signifie que le Décoder l'unité de Les processeurs CISC sont beaucoup plus complexe et est un autre des facteurs les plus importants pour que x86 ait une consommation plus élevée.

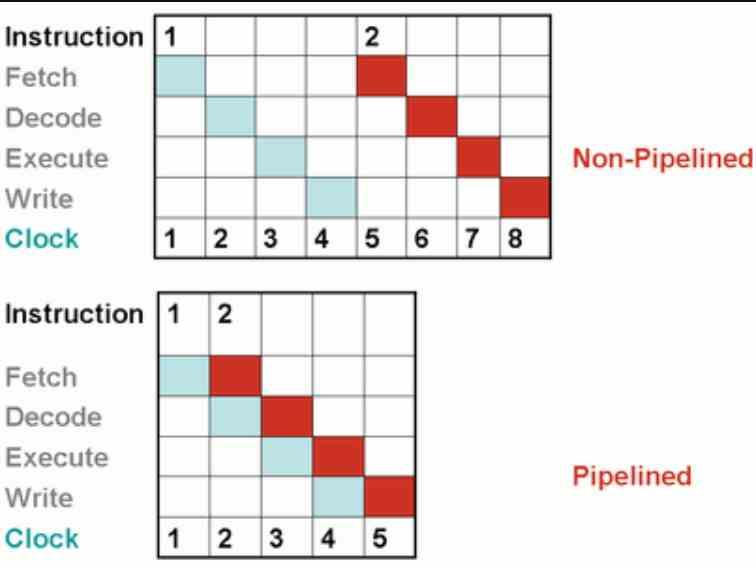

Segmentation sur x86 vs ARM

L'une des particularités de tous les processeurs depuis le début des années 90 est la segmentation, consistant en ce qu'au lieu d'attendre qu'une instruction soit exécutée intégralement dans le processeur pour faire place à la suivante, celles-ci sont avancées à chaque étape de l'instruction. cycle, qui peut être divisé en plusieurs sous-étapes chacune d'elles.

Comme les processeurs RISC ont une corrélation directe entre le nombre d'instructions dans le code binaire et celles exécutées par le CPU, il est très facile de segmenter les instructions en plusieurs étapes. Mais dans un x86, c'est extrêmement difficile , puisque la segmentation se fait sur les micro-instructions générées lors de l'étape de décodage, ce qui signifie encore plus circuits supplémentaires courant et consommant de l'énergie en continu.

Non seulement cela, mais si par exemple les opcodes de chaque instruction dans ARM sont de taille fixe dans le cas de x86, ils sont variables, ce qui rend le décodage des instructions dans les micro-instructions beaucoup plus complexe dans le cas des processeurs x86.

Moins d'enregistrements équivaut à moins d'efficacité énergétique

L'ISA x86 a beaucoup moins de registres à l'intérieur de celui-ci que d'autres ISAS, cela signifie que de nombreuses instructions doivent être exécutées sur la mémoire, ou les caches, ce qui fait que vous finissent par consommer beaucoup plus d'énergie lors de l'exécution. C'est un problème classique de l'architecture x86 et non pas parce que c'est une architecture CISC.

Pour le comprendre, il faut prendre en compte la consommation d'énergie de chaque opération dépend de la distance entre les données et le processeur .

x86 vs ARM sur les appareils à très faible consommation.

Intel l'a essayé il y a quelques années avec le processeur Intel Medfield en panne.

De plus, l'une des possibilités envisagées est la création d'un CPU mixte , qui consiste en un x86 qui décode en interne ses instructions en instructions ARM et permet une compatibilité totale entre les deux ISAS, qui serait le processeur définitif.

Mais malheureusement ni ARM, ni Intel et AMD, en particulier ces derniers, ne sont intéressés par la fabrication de ce processeur mixte car pour le faire travailler dans les deux modes, il serait très difficile à réaliser, à part cela, le décodage des instructions x86 continuerait d'être un problème, nous aurions donc un processeur qui ne pourrait fonctionner que d'une seule manière et où la plupart du circuit serait gaspillé.