S'il y a quelque chose d'évident dans le processeur l'industrie, c'est ça Intel et AMD dominer complètement le marché dans un duopole qui semble sans égal. Cependant, ces derniers temps, l'ODM (cela signifie qu'ils ne fabriquent pas de puces, ils ne font que les concevoir) BRAS prend de plus en plus d'importance, en particulier avec des designs tels que DynamIQ , un pari qui promet de améliorer la puissance de processeurs tout en maintenant la consommation, et dans cet article nous allons vous dire de quoi il s'agit.

En fait, s'il existe une conception ARM connue, elle est big.LITTLE , constitué d'une architecture hétérogène qui se compose de cœurs plus gros et plus puissants pour effectuer des tâches exigeantes et d'autres cœurs plus petits et de faible puissance pour économiser de l'énergie lorsque l'équipement ne le fait pas. nécessite une grande puissance. Cette architecture est implémentée dans les puces de smartphone depuis longtemps et il n'y a pas si longtemps qu'Intel (et il semble même qu'AMD avec Zen 5) ait adopté un paradigme similaire (mais à sa manière) dans ses processeurs de bureau, donc tout indique ce qui est la voie à suivre.

ARM DynamIQ, comment augmenter la puissance sans augmenter la consommation?

L'architecture ARM a fonctionné pendant de nombreuses années comme une alternative à Intel et AMD, mais surtout dans les téléphones mobiles et les serveurs grâce à sa faible consommation, mais il a fallu attendre Apple a décidé de créer sa propre puce M1 et de l'intégrer dans ses ordinateurs jusqu'à ce que ARM entre véritablement dans l'industrie informatique nationale.

Cette nouvelle architecture qu'ARM a baptisée DynamIQ (c'est un jeu de mots en anglais qui combine le mot «dynamic» avec «IQ», IQ) s'adresse en principe aux appareils mobiles et IdO appareils, mais ils ont confirmé qu'ils ont également l'intention d'atteindre l'écosystème des ordinateurs personnels et même des serveurs, car son potentiel est énorme.

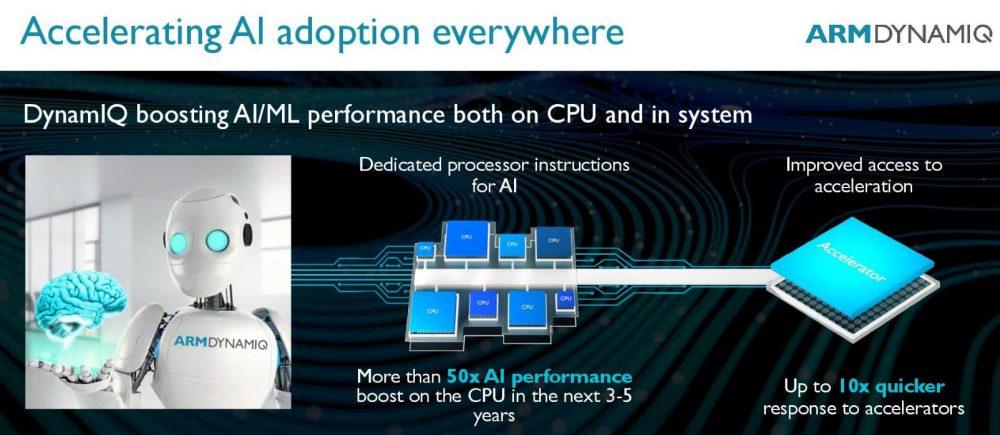

Selon ARM, l'objectif de cette architecture est de permettre à leurs puces d'être équipées de systèmes de réalité virtuelle et d'apprentissage automatique, et pour cela ils ont ajouté plus de cœurs et un plus grand nombre d'instructions (et c'est précisément ce que ARM a toujours fait «faible» par rapport à x86, car ses puces ont des jeux d'instructions beaucoup plus petits et plus spécifiques), offrant jusqu'à 50 fois plus de puissance global pour les tâches d'IA.

Le thème sous-jacent de DynamIQ est l'évolutivité hétérogène; Ces deux mots cachent beaucoup de jargon à l'écosystème, mais comme ARM prédit que 100 milliards de puces ARM supplémentaires seront vendues dans les 5 prochaines années, ils pointent vers des domaines clés tels que l'automobile, l'intelligence artificielle et l'apprentissage automatique à la fin intéressante de cela. croissance. Par conséquent, les performances, l'évolutivité et la latence seront des indicateurs clés à l'avenir que DynamIQ entend activer.

Un pas au-delà du grand.

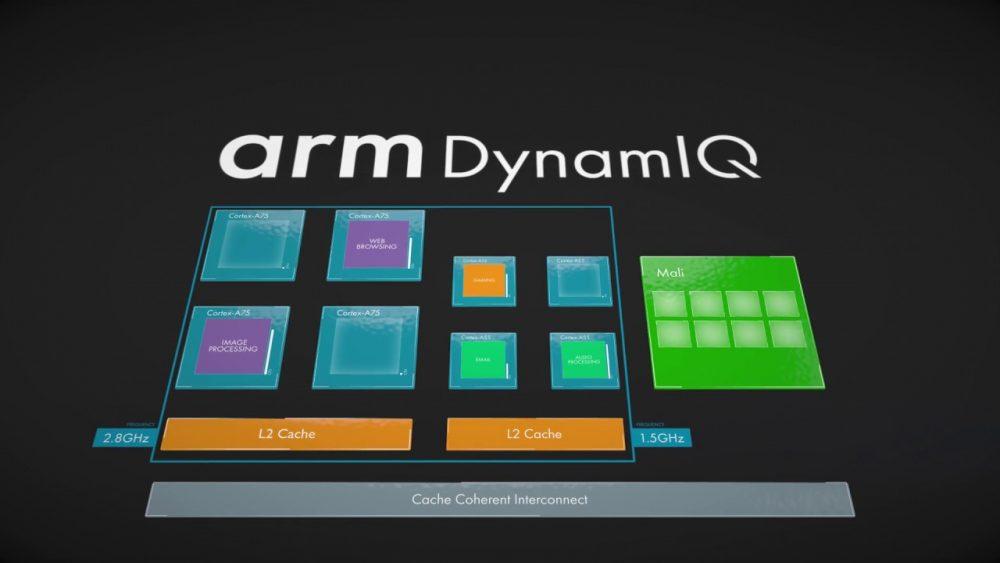

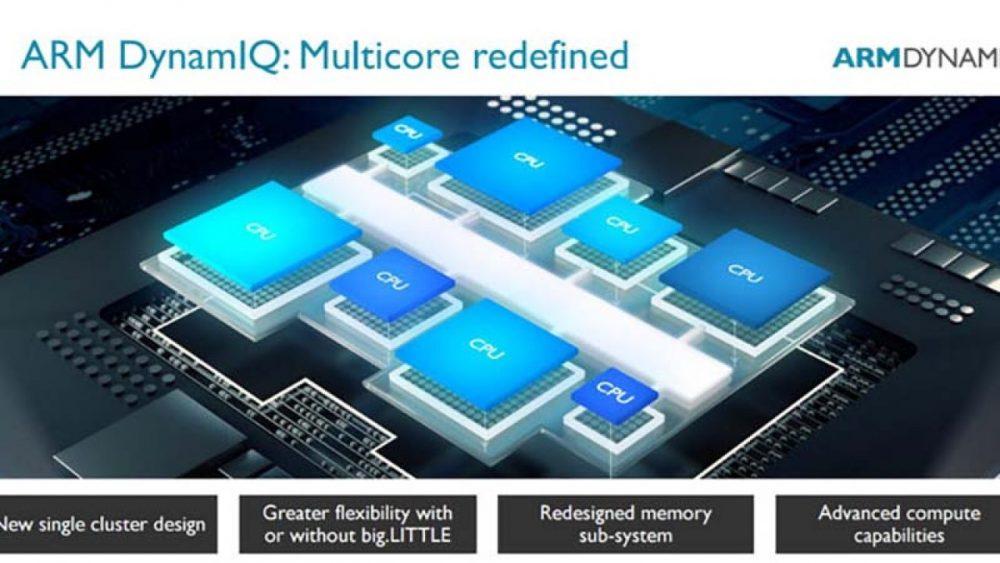

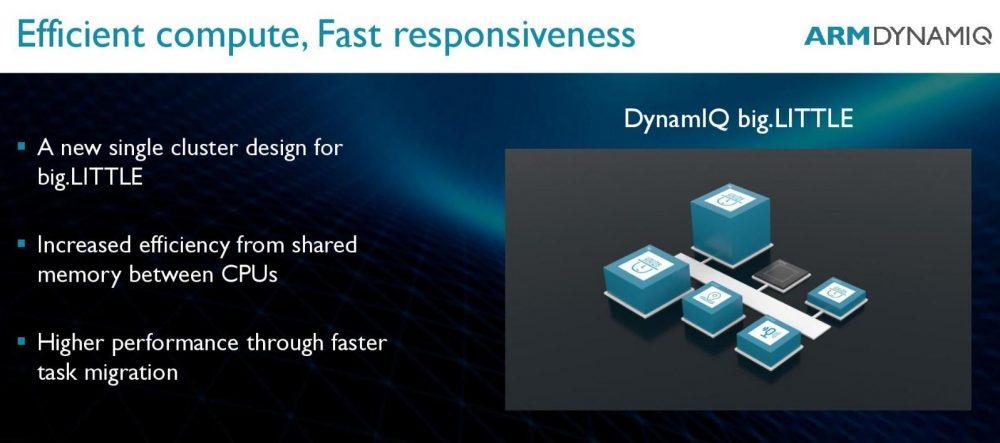

La première étape de DynamIQ est un paradigme de cluster plus large, ce qui signifie jusqu'à huit cœurs pour chacun d'eux. Cependant, cela signifie qu'il peut également y avoir une conception de noyau variable au sein d'un cluster; Ces huit cœurs pourraient être complètement différents les uns des autres, et même de différentes familles Cortex-A dans différentes configurations.

La similitude avec big.LITTLE est plus qu'évidente, seulement qu'au lieu d'avoir des «gros noyaux» et des «petits noyaux», ici cela permettrait directement d'avoir un nombre défini de noyaux et que chacun d'eux était différent de tous les noyaux . d'autres (c'est vraiment la différence avec big.LITTLE).

De nombreuses questions se posent ici, telles que la manière dont la hiérarchie du cache permettra aux threads de migrer entre les cœurs d'un cluster (peut-être de la même manière que les threads migrent entre clusters big.LITTLE aujourd'hui), même lorsque les cœurs ont des dispositions de cache différentes. ARM n'est pas encore entré dans ce niveau de détail, il est donc toujours en suspens. Chaque cluster de configuration à cœur variable fera partie d'une nouvelle structure, avec des modes d'économie d'énergie supplémentaires, et son objectif est de fournir une latence beaucoup plus faible.

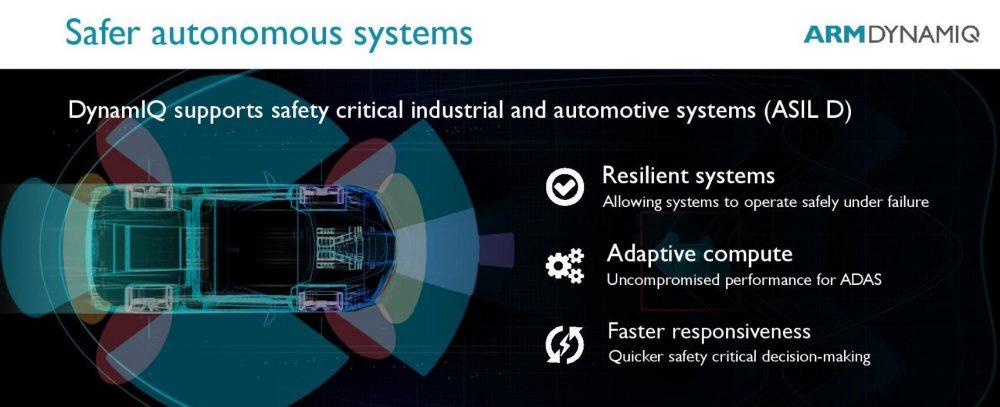

La conception sous-jacente permet également à chaque noyau d'être contrôlé indépendamment pour la tension et la fréquence, ainsi que les états de veille d'économie d'énergie. Selon les diapositives fournies par ARM, divers autres blocs IP tels que les accélérateurs, devraient pouvoir se connecter à cette matrice et bénéficier de cette faible latence; les éléments cités par ARM comme étant des décisions automobiles critiques pour la sécurité pourraient en tirer un grand bénéfice.

L'un des principaux domaines d'intervention d'ARM est la redondance. La nouvelle structure permet d'utiliser un nombre apparemment illimité de clusters, de sorte que si l'un échoue, les autres peuvent prendre sa place. Cela dit, le type de redondance dont certains clients de puces ARM pourraient avoir besoin est le basculement en cas de dommages physiques, comme cela pourrait se produire dans un accident de voiture autonome. Il sera intéressant de voir si la vision d'ARM avec DynamIQ s'étend à ce niveau de redondance au niveau du SoC ou si ce type d'implémentation dépendra des partenaires ARM.

Parallèlement au nouveau cadre, ARM a déclaré qu'une nouvelle conception de sous-système de mémoire a été mise en œuvre pour aider avec les capacités de calcul; cependant, rien de spécifique n'est mentionné. Sur la ligne de calcul supplémentaire, ARM affirme que de nouvelles instructions de processeur dédiées (telles que des opérations à précision limitée) pour AI et L'apprentissage automatique va être intégré dans une variante de l'architecture ARMv8.

Nous ne savons pas pour le moment s'il s'agit d'une extension d'ARMv8.2-A qui a introduit une précision moyenne pour le traitement des données, ou s'il s'agit d'une toute nouvelle version. ARMv8.2-A ajoute également des fonctionnalités RAS et des améliorations du modèle de mémoire, ce qui est cohérent avec la «nouvelle conception de sous-système de mémoire» mentionnée ci-dessus. ARM a déclaré que de nouveaux cœurs seront nécessaires pour fabriquer des processeurs avec cette architecture.

Pour l'instant, ARM DynamIQ se concentre sur les technologies nouvelles et futures telles que l'IA, l'automobile et la réalité mixte, même s'il est vrai qu'il est clair que DynamIQ peut être utilisé dans d'autres modèles d'utilisation existants tels que les tablettes, les smartphones, les PC et les serveurs. Cela dépendra, oui, de la façon dont ARM le rend compatible avec les conceptions de base actuelles, car ils pourraient simplement le publier sous forme de licence distincte.