La AMD L'architecture Zen 4 est la quatrième génération de l'architecture Zen d'AMD et apporte une série de changements importants par rapport à la génération précédente ainsi qu'une série de nouveautés spécifiques. Tous dans le but d'augmenter les performances par rapport à Zen 3 et d'être compétitif contre un Intel qui met toute sa viande sur le gril. Quoi de neuf dans l'architecture AMD Zen 4 ? On vous l'explique.

Plusieurs années se sont écoulées depuis qu'AMD a sorti ses premiers processeurs Ryzen 1000 basés sur son architecture Zen de première génération. Ce qui était un coup de chance pour la société dirigée par Lisa Su et qu'AMD ne sera plus considérée comme une marque de processeurs bon marché toujours à la remorque d'Intel. Aujourd'hui, les architectures AMD peuvent non seulement échanger des coups avec celles d'Intel, mais aussi les surpasser à plusieurs égards.

Dans le cas de Zen 3, il a supposé que la tortue AMD avait dépassé le lièvre Intel. Qui a réalisé le danger d'un AMD qui a réduit la part de marché des processeurs x86 dans les différents segments de ceux-ci dans lesquels ils sont en concurrence de vous à vous. Mais malgré son avantage éventuel, AMD ne peut pas se permettre de s'endormir sur un marché en constante évolution et changement où se reposer sur ses lauriers, c'est directement sortir de la course et même disparaître. C'est pourquoi AMD a conçu le Zen 4 avec des changements importants par rapport au Zen 3 et qui comprend plusieurs gammes de ses processeurs.

Configuration des cœurs dans Zen 4

L'architecture Zen englobe les cœurs dans quelque chose qu'AMD appelle CCX, qui consiste en une série de cœurs avec les caractéristiques suivantes :

- Chaque cœur a un cache privé de premier et de deuxième niveau, c'est-à-dire que le reste des cœurs ne peut pas y accéder.

- Le cache L3 est partagé et tous y ont accès. De plus, les différents cœurs communiquent en interne via un réseau d'interfaces Infinity Fabric.

- Dans Zen et Zen 2, chaque CCX était composé de 4 cœurs et de leur L3 partagé. Dans Zen 3, il est passé de 4 à 8 cœurs. Zen 4 aura le même type de configuration que Zen 3 et donc 8 cœurs par CCX .

Une autre différence est que l'architecture Zen 4 est conçue pour être construite sous le nœud 5 nm de TSMC, qui a des règles de conception différentes de celles de son nœud 7 nm. Ainsi, toute puce utilisant les cœurs Zen 4 sera basée sur ce nœud de fabrication. Soit une puce CCD, soit un APU monolithique.

L'architecture Zen 4 intégrera les instructions AVX-512

La première grande nouveauté sera dans le prise en charge des instructions AVX-512 , qui jusqu'à présent était réservé aux processeurs Intel. Ces instructions, comme leur nom l'indique, sont des instructions SIMD de 512 bits, les plus longues à ce jour qui ont été utilisées dans un Processeur avec architecture x86. De plus, les instructions AVX-512 contiennent différentes extensions pour différentes applications. Extensions AVX512 supportées par les cœurs Zen 4 ? Ils sont les suivants

- AVX512VL

- AVX512BW

- AVX512CD

- AVX512_IFMA

- AVX512DQ

- AVX512F

- AVX512_VPOPCNTDQ

- AVX512_BITALG

- AVX512_VNNI

- AVX512_VBMI2

- AVX512_VBMI

- AVX512_BF16

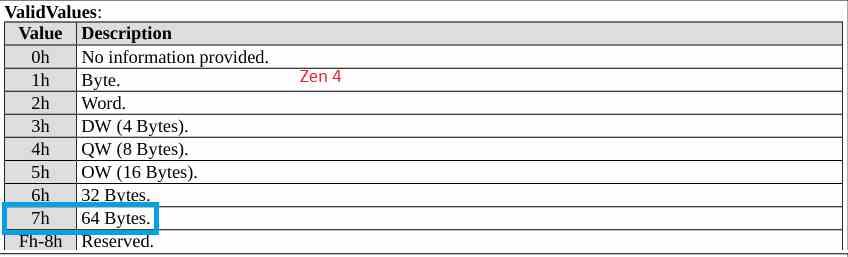

De plus, l'implémentation des instructions AVX-512 dans Zen 4 suppose que les lignes de cache de données de premier niveau et les niveaux de cache ultérieurs ont augmenté le taille de la ligne de cache de 32 à 64 octets ou 512 bits . Ce qui est essentiel pour collecter toutes les données pour une instruction AVX-512 à un seul cycle. Cette petite amélioration signifie non seulement la prise en charge des instructions AVX-512, mais la bande passante des unités Load/Store du CPU a augmenté et avec elle la bande passante interne du processeur. De plus, le fait que Zen 4 puisse charger directement 64 octets de données signifie qu'il existe un nouvelle unité AVX-512 capable d'exécuter ces instructions en un seul cycle.

Les instructions de l'AVX-512 contiennent cependant une limitation et c'est leur niveau de consommation élevé. Cela pourrait amener les processeurs Zen 4 à fonctionner en dessous de leur vitesse d'horloge habituelle lors de l'utilisation de ces types d'instructions.

Changements du système de cache dans l'architecture Zen 4

| Cache | AMD Zen 4 | AMD Zen 3 |

|---|---|---|

| Données L1 | 32 Ko 8 voies | 32 Ko 8 voies |

| Instructions L1 | 32 Ko 8 voies | 32 Ko 8 voies |

| L2 | 1 Mo 8 voies | 512 Ko 8 voies |

| L3 | 32 Mo 16 voies | 32 Mo 16 voies |

| L1 ITLB (MMU) | 64 entrées entièrement associatives | 64 entrées entièrement associatives |

| L1 DTLB (MMU) | 512 entrées 4.Way | 512 entrées 4.Way |

| L2 ITLB (MMU) | 72 entrées entièrement associatives | 64 entrées entièrement associatives |

| L2 DTLB (MMU) | 3072 billets aller-retour | 2048 billets aller-retour |

Depuis le premier AMD Zen, le système de cache des processeurs AMD est resté plus ou moins le même. À l'exception du cache de dernier niveau qui est partagé par tous les cœurs du CCD, mais dans le cas de Zen 4, il y aura des changements dans la structure du cache du cœur lui-même, que vous pouvez voir dans le tableau suivant.

Le premier changement à souligner est dans le cache L2 de chaque cœur , cela augmentera la capacité du 512 Ko à 1 Mo de mémoire , ce qui augmente les chances de trouver les données dans ledit cache, mais au lieu de cela, les caches L1 et L3 resteront de taille inchangée. Bien sûr, comme nous l'avons déjà commenté, la taille par ligne de cache est passée de 32 octets à 64 octets.

Il ya aussi des modifications apportées au TLB ou aux tampons d'anticipation de traduction . Ils sont utilisés par la MMU dans chaque cœur de processeur pour traduire les adresses virtuelles en adresses physiques. Comme vous pouvez le voir dans le tableau qui commence cette section, le tampon d'anticipation pour le cache de données de premier niveau est passé de 64 entrées à 72 entrées . En revanche, le cache L2 est passé de 2048 entrées à 3072 entrées s. Cela représente une augmentation de 50 % à cet égard et non seulement en capacité, mais aussi en nombre d'accès simultanés .

Prise en charge de la mémoire RAM via Compute Express Link

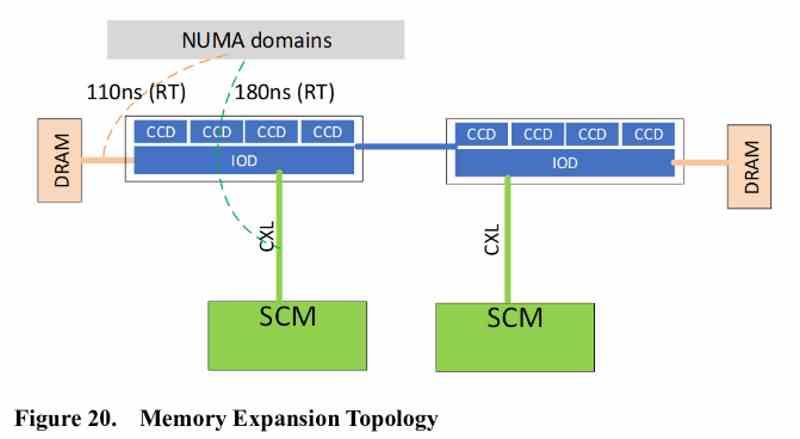

C'est là qu'il faut commencer à différencier la gamme de processeurs pour portables et desktops du futur AMD EPYC sous le nom de code Genoa et c'est alors que la norme PCI Express 5.0 ne sera pas disponible pour les CPU sous socket AM5 ce sera. sur les processeurs AMD HEDT et serveurs basés sur Zen 4 et avec ça prise en charge de CXL .

La clé de la norme CXL est qu'elle donne une cohérence mémoire à l'interface PCI Express 5.0, ce qui signifie que les modules de mémoire, qu'ils soient de la mémoire non volatile, RAM, ou une combinaison de ceux-ci peut non seulement être connecté via l'interface mémoire classique , mais aussi via le port PCI Express.

Sur le marché, il existe déjà des modules d'extension de mémoire RAM via PCI Express avec CXL, également appelés Storage Class Memory ou SCM. AMD va intégrer dans son AMD EPYC Genoa la possibilité d'étendre la RAM système via l'interface PCIe 5.0 . Bien entendu, avec en contrepartie une latence plus élevée dans l'accès à ladite mémoire par rapport à la DDR5, LPDDR5 ou tout autre type de mémoire compatible avec laquelle AMD rend compatibles les CPU et APU à l'architecture Zen 4.

L'utilisation de deux puits mémoire différents au niveau physique implique également la mise en œuvre de Mécanismes DMA pour copier les données des deux espaces mémoire , qui, bien qu'unifiées au niveau de l'adressage, ne le sont pas au niveau physique, ce qui signifie qu'il faut un mécanisme pour copier les données d'un espace RAM à l'autre.

Plus grande bande passante interne et externe

Il y a un détail qui n'a pas été dit dans tout ça et c'est qu'AMD utilise son interface Infinity Fabric pour communiquer à la fois en interne et en externe les différents composants. Des interfaces IF avec une bande passante de 32 octets ont été utilisées pour communiquer des caches entre elles depuis plusieurs générations d'AMD Zen et le passage de 32 octets par ligne de cache à 64 octets représente également un saut dans cet aspect et cela la quantité de données circulant à l'intérieur du CCD et du CCX avec l'architecture Zen 4 a doublé par rapport à Zen 3.

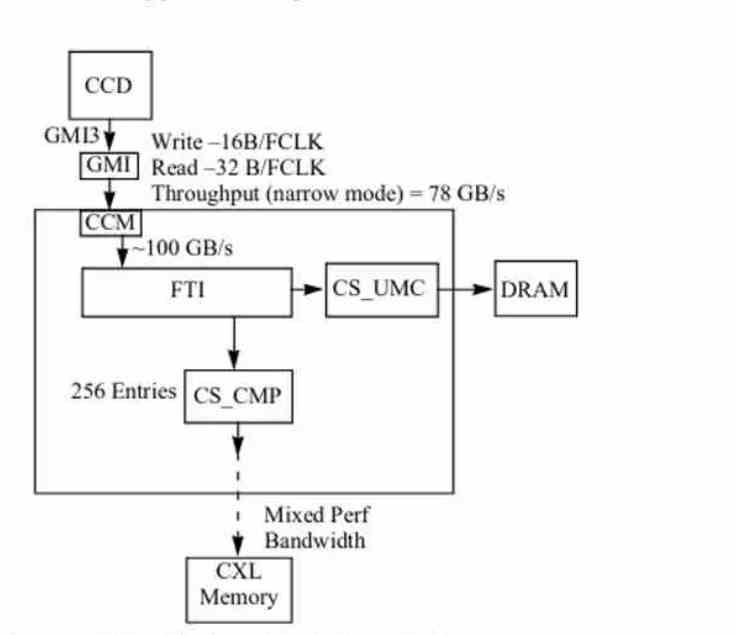

Cependant, en termes de communication avec le Northbridge ou l'IOD, il ne semble pas qu'il y aura de changements et le GM Le port I qui communique les Chiplets CCD qui contiendront les cœurs Zen 4 continuera à avoir un bus 16 octets/cycle pour l'écriture et un bus 32 octets. / cycle pour la lecture à la vitesse d'horloge IOD . Dont on se souvient que dans l'architecture zen dépend de la vitesse d'horloge du contrôleur DRAM utilisé . Dans le schéma extrapolant les bandes passantes on peut déduire que la vitesse d'horloge de l'IOD est de 2400 MHz, ce qui correspond au memclk de la DDR5-4800.

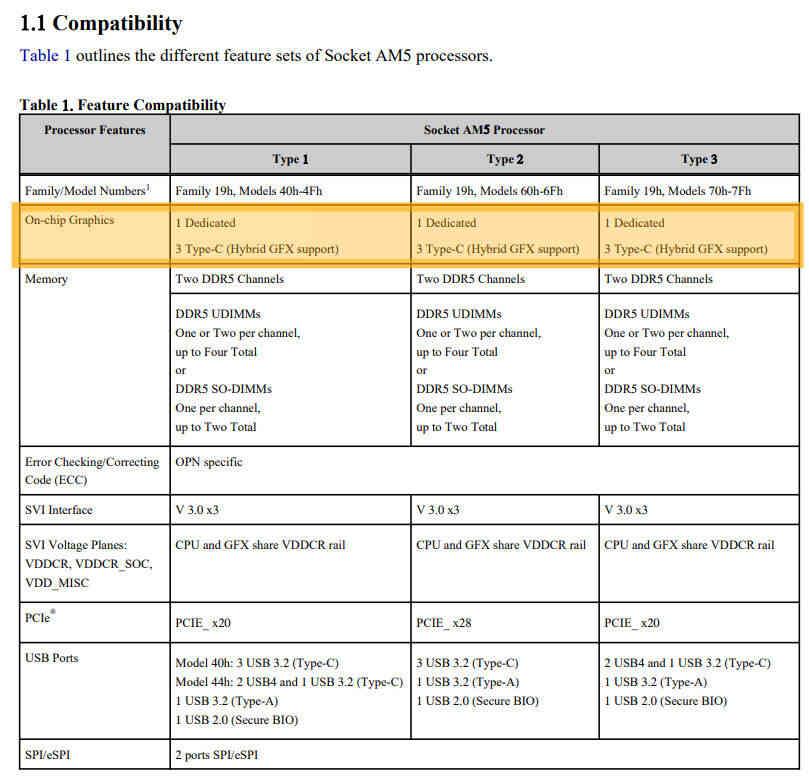

Nous ne pouvons pas oublier le IO Hub soit . Qui se trouve également dans l'IOD ou Northbridge et est responsable de la communication avec les périphériques. Étant l'une des parties qui a également reçu des améliorations à la suite de la prise en charge des nouvelles interfaces d'E / S. Comme c'est le cas avec USB4 et PCI Express 5.0. AMD a donc augmenté son bande passante de 750 MHz à 1150 MHz .

Qui sert pour que le nombre maximum de voies PCIe 4.0 est passé de 24 lignes à 28 lignes . Cela signifie que carte mère fabricants peut intégrer un deuxième M.2 NVMe SSD ou une interface USB 4 . Bien entendu, ces 4 lignes supplémentaires ne seront pas disponibles sur tous les chipsets compatibles Zen 4 comme on peut le voir dans le tableau qui accompagne ces deux derniers paragraphes.