Kaikki tässä elämässä noudattaa menetelmiä, erityisesti uusien tuotteiden kehittämiseksi. Joka koostuu sarjasta protokollia, joiden tarkoituksena on saavuttaa selkeä tulos mahdollisimman lyhyessä ajassa. Suorittimien suunnittelu ei ole tästä vieras ja siksi aiomme kuvata eri vaiheita, joita noudatetaan suunniteltaessa prosessori.

Jos otamme muutama vuosi sitten suoritetun prosessorin ja ostamme sen uudella ensi silmäyksellä, ne näyttävät samanlaisilta, mutta näin ei ole, uudempien mallien monimutkaisuus vaatii paljon pidempää työaikaa ja sen myötä entistäkin enemmän pätevä henkilöstö. määrä. On totta, että jokainen uusi valmistussolmu sallii useamman transistorin sijoittamisen, mutta tämä edellyttää myös enemmän työtä ja koska kehitysajat ovat anteeksiantamattomia, on välttämätöntä, että uusien mallien suunnittelu seuraa sarjaa järjestettyjä vaiheita.

Kaikki alkaa valmistussolmun valitsemisesta

Ensimmäisen vaiheen eivät tee insinöörit, vaan sen suorittavat johtajat, jotka neuvottelevat monen miljoonan dollarin sopimukset eri valimoiden kanssa ja tekevät erilaisia ennusteita tuotannon tasosta ja kustannuksista.

Valmistussolmun eritelmät ja kustannukset määrittävät arkkitehdeille, mikä on alue, jonka he tarvitsevat luoda siru, budjetti transistoreiden lukumäärälle ja kehitysajat, jotka heidän on luotava uudet CPU-mallit.

Seuraava on oivalluksen toteutus

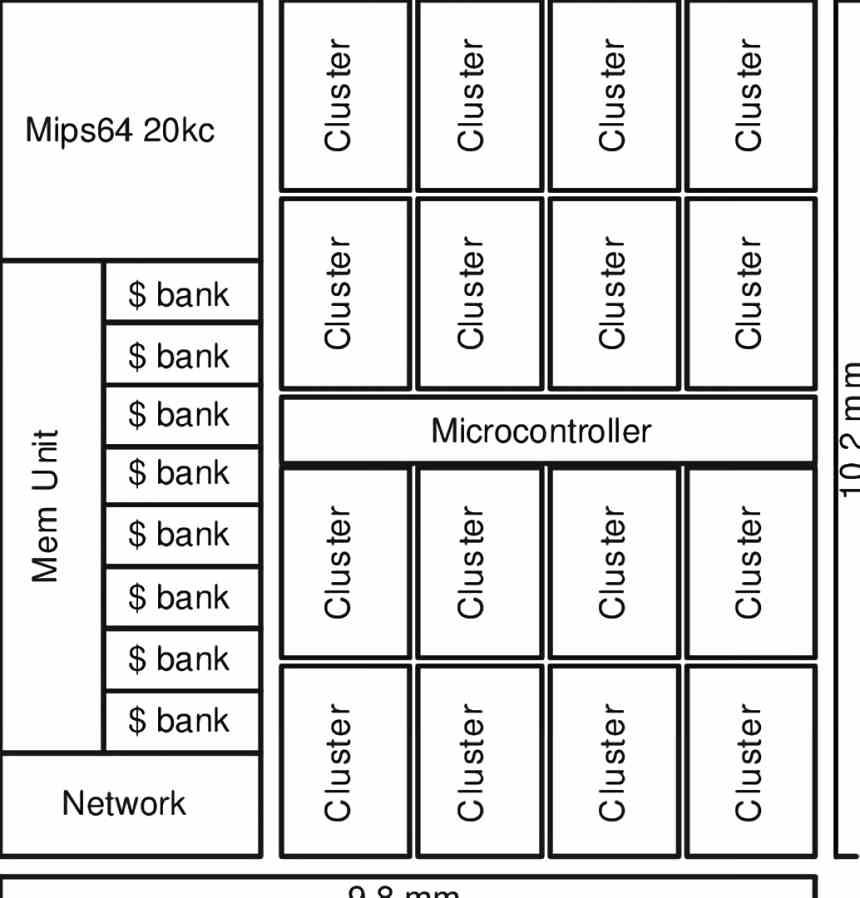

Pohjapiirros ei ole muuta kuin kaavio, jossa ilmoitamme CPU: n muodostavat yleiset peruselementit tilaamaan ne tilaan. Yleisillä elementeillä emme puhu suorittimen ytimen sijoittamisesta tänne, välimuisti täältä GPU siellä jne.

Mutta tällä tarkoitamme paljon enemmän peruselementtejä, kuten yhdistelmäpiirejä, kuten multiplekseri, erityyppiset logiikkaportit, ALU: t, muistipuskurit jne. Tämä johtuu siitä, että laitteistokuvauskielet edellyttävät, että eri elementit on määriteltävä, ja siksi on välttämätöntä ottaa lyijykynä ja paperi, valtava paperiarkki yhdistääksesi järjestelmän eri elementit.

Ensimmäinen luotu kaavio ei ole lopullinen, mutta sitä käytetään järjestämään prosessorin eri moduulit kahteen tyyppiseen lohkoon:

- Ensimmäisiä kutsutaan kiinteiksi lohkoiksi, ne sisältävät elementtejä, joita ei muuteta suunnittelumuunnelmissa ja jotka pysyvät staattisina pinta-alaltaan, johtuen siitä, että niiden luonne sen sallii.

- Toisaalta monipuoliset lohkot ovat osia, jotka aiotaan muuttaa, varsinkin koska vuorovaikutus sirun muiden osien kanssa vaatii sitä tai yksinkertaisesti siksi, että ne eivät vielä tiedä, mikä muotoilu toteutetaan lopullisessa versiossa.

Jos prosessorin pohjapiirroksessa on riittävästi tilaa joidenkin elementtien parantamiseksi, se pyrkii integroimaan kehittyneempiä ratkaisuja niille osille, joita kehitetään rinnakkain ja jotka näemme seuraavassa osassa.

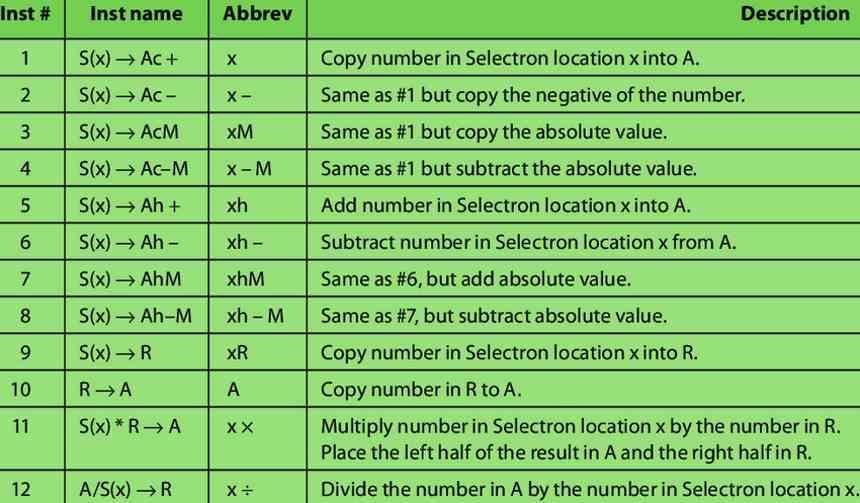

3. CPU: n suunnitteluvaiheista: ISA: n määrittely

Seuraava vaihe on määriteltävä käytettävä rekisteri- ja käskyjoukko. Jos suorittimet periytyvät sukupolvelta toiselle, niiden suorittaminen saattaa tuntua helpolta, mutta uusien ohjeiden ja rekistereiden lisääminen tuo mukanaan uudelleenjärjestelyn jotain, joka itsessään on riittävän monimutkainen.

Grafiikkasuoritimissa se on erilainen, ne eivät käytä ohjelmia, ja jokainen uusi sukupolvi tarkoittaa kykyä muuttaa sen varjostinyksiköiden ISA: n luonnetta monipuolisemmalla tavalla. Joten jos ohjeiden poistaminen on välttämätöntä, se voidaan tehdä, mutta suorittimessa se ei ole, käskyn tai rekisterin poistaminen rikkoo yhteensopivuutta ohjelmiston kanssa.

Tietojen käsittelystä vastaavat osat ovat yleensä erikokoisia minkä tahansa tyyppisen prosessorin suunnittelussa ja ne, jotka lopulta käyvät läpi tämän suunnitteluvaiheen. Kiinteät funktioelementit eivät sitä vastoin saa näitä muutoksia.

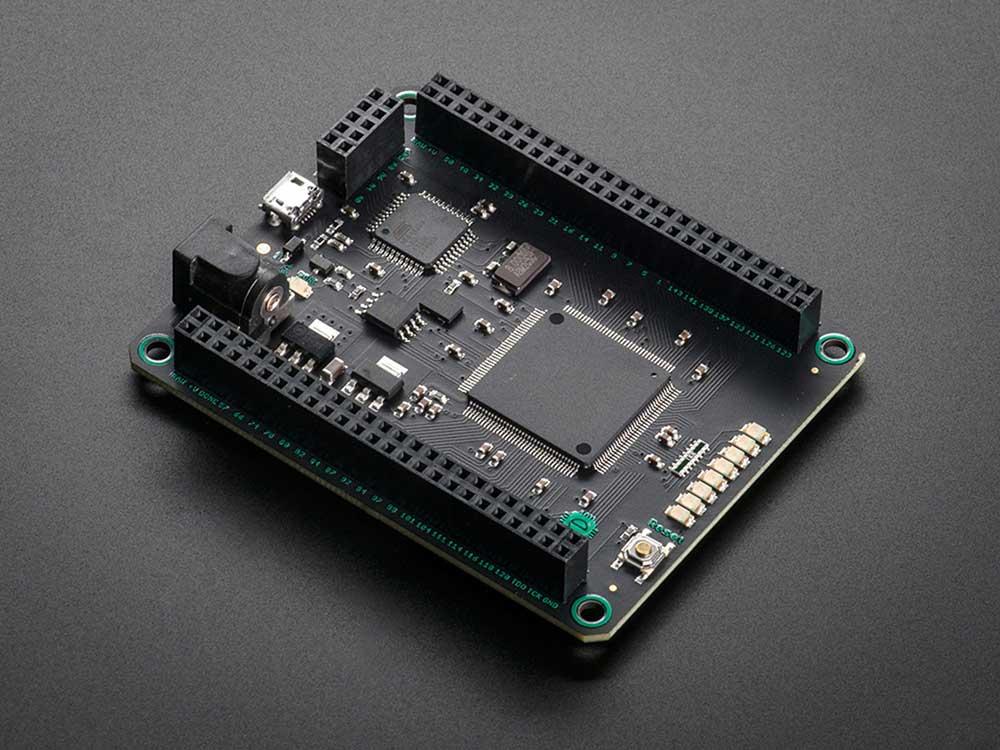

Neljäs CPU: n suunnitteluvaihe: testaus FPGA-tiedostoissa

Ei, emme ole vielä saavuttaneet viimeistä vaihetta, mutta on tarpeen osoittaa, että suunnittelu on toimiva, tätä tarkoitusta varten FPGA-levyt on yleensä kytketty toisiinsa valtavassa matriisissa. Jokainen FPGA: sta on ohjelmoitu tai pikemminkin konfiguroitu toimimaan osana suunnittelemaamme suorittimen tai GPU: n kokonaissuunnittelua.

Ajatuksena ei ole saada täyttä nopeutta, vaan tarkistaa hidastettuna, että muotoilu on toimiva. Joten meillä on paljon suuremmat viiveet ja paljon pienemmät nopeudet kuin lopullisella prosessorilla, mutta meitä kiinnostaa se, että kaikki elementit toimivat.

Viides suorittimen suunnitteluvaihe: I / O, teho ja kello

Neljäs vaihe koostuu jo sirun luomisesta on lopullisen sirun luominen, mutta meillä on tulo-ongelma, että meidän on suunniteltava toisaalta piirin energian jakautuminen ja toisaalta kellosignaalien energiajakauma , joista osa on johdettu pääkellosta, joka jaetaan alempana, ja toisilla on oma kellonsa.

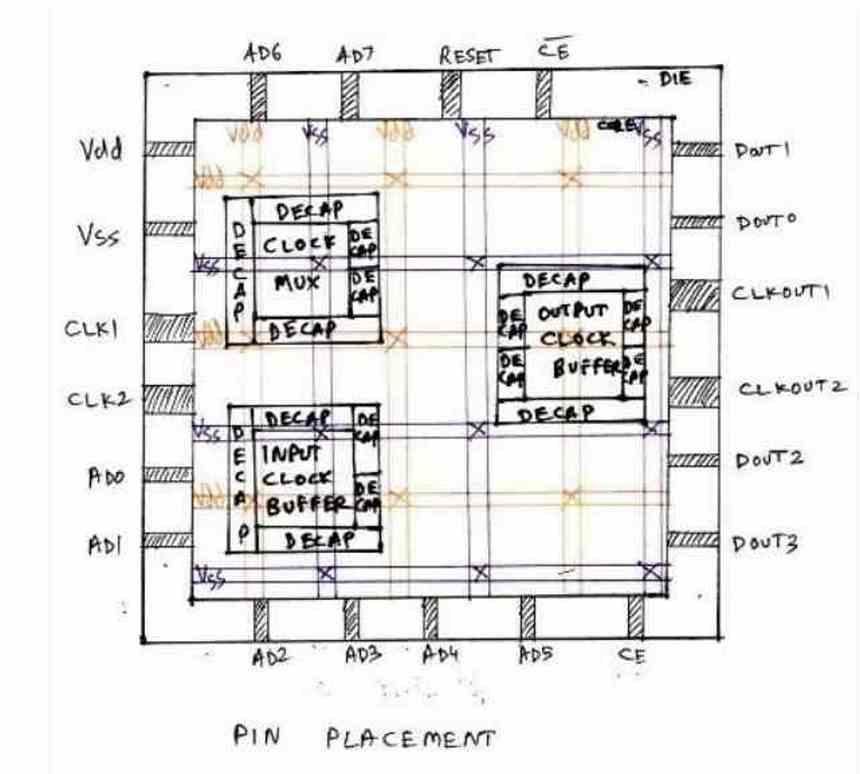

Se, mitä teet, on ottaa pohjapiirros, jonka olemme nähneet edellisessä osassa, ja ympäröi se neliöön tai suorakulmioon jaettuna kvadrantteihin. Neljännesten ulkopuolelle sille on määritetty tietty energia- tai I / O-toiminto. Täällä sirun kehä on suunniteltu ja erilaisten tietoliikenneliitäntöjen sijainti oheislaitteiden ja muistin kanssa on merkitty.

Tässä vaiheessa tarkistetaan myös kaikki sähköenergian jakautumista koskevat asiakirjat, jos eri elementtien suunnittelu mahdollistaa odotettujen kellonopeuksien saavuttamisen.

Suorittimen vahvistus

Suunnittelun jälkeen tulee saman todentaminen. Jossa täysin erilainen joukkue validoi valmiin suunnittelun, joka etsii suunnitteluvikoja fyysisellä tasolla, jolla sillä voi olla. Validointiryhmän tuntemus on täysin erilainen kuin suunnittelun.

Syynä tähän on se, että ne koskettavat hyvin erilaisia haaroja ja validointitiimi keskittyy enemmän havaitsemaan ja korjaamaan virheitä, jotka tapahtuvat suorittimen fyysisessä toteutuksessa eikä sen arkkitehtuurissa, joka ei muutu alkuperässä. Rakennemaailmaa vastaava olisi sellaisten työntekijöiden ja urakoitsijoiden ryhmä, jotka prototyyppiävät talon tai rakennuksen ja havaitsevat virheet, jotka vaikuttavat lopullisen suunnittelun suorituskykyyn ja joita ei näy simulaatiossa.