Kun se tulee mittaamaan RAM ja VRAM, puhumme yleensä kahdesta suorituskykyparametrista, jotka ovat kaistanleveys ja viive. Mutta mikä on näiden kahden ominaisuuden suhde ja voimmeko luokitella ne vakioiksi?

Yksi teknisten eritelmien ongelmista on, että niillä on taipumus antaa 100%: n suorituskyvyllä täydellisissä olosuhteissa. Muistin tapauksessa tätä ei tapahdu, koska kaikki tiedot eivät ole samalla viiveellä ja kaistanleveys ei ole koskaan 100%.

Suurempi kaistanleveys ei tarkoita vähemmän viivettä

Ymmärrämme käsittelyyksikön ja siihen liittyvän muistin välisen viiveen ajan, joka kuluu pyydettyjen tietojen vastaanottamiseen tai signaalin vastaanottamiseen siitä, että muutos on tehty muistiin. Joten latenssi on todellakin tapa mitata aikaa.

Kaistanleveys on sen sijaan tietomäärä, joka lähetetään sekunnissa, joten se on nopeuden nopeus. Joten suoran logiikan avulla voimme ajatella, että suuremmalla nopeudella, kun etsimme dataa, sitten lyhyemmässä ajassa prosessori, GPU tai mikä tahansa muu käsittelyyksikkö saa tiedot.

Tosiasia on, että näin ei ole, ja lisäksi on erityispiirre, että mitä enemmän kaistanleveyttä muistilla on, niin sillä on yleensä enemmän viivettä muihin verrattuna. Tällä ilmiöllä on selitys, jonka aiomme selittää sinulle tämän artikkelin seuraavissa osissa.

Tietojen etsiminen lisää viivettä

Lähes kaikilla prosessointiyksiköillä on nykyään välimuistien hierarkia, jossa prosessori kysyy jokaiselta ensin ennen RAM-muistin käyttöä. Tämä johtuu siitä, että suorittimen ja RAM-muistin välinen suora viive on riittävän suuri johtamaan suorituskyvyn menetykseen ihanteellisen prosessorin yli.

Kuvittele, että etsit tiettyä tuotetta. Ensinnäkin etsit paikallista kauppaa, sitten hieman suurempaa kauppaa ja lopuksi tavarataloa. vierailu jokaiseen laitokseen ei tapahdu heti, mutta vaatii matkustusaikaa. Samaa tapahtuu välimuistihierarkiassa, tätä kutsutaan välimuistihäviöksi, jotta voimme tiivistää ajan seuraavasti:

Hakuaika = Haku aika ensimmäisessä välimuistissa + välimuistin ohitusjakso +… viimeisen välimuistin hakuaika.

Jos välimuistin hakuaika on pidempi kuin päämuistiin siirtymiseen kuluva aika, välimuistijärjestelmä on huonosti suunniteltu prosessorille, koska se on vastoin välimuistin luomistarkoitusta.

Nyt latenssiongelma on monimutkaisempi, koska välimuistihaun lisäämään pääsyaikaan meidän on lisättävä latenssi, joka lisätään RAM-muistin tietojen etsimiseen, jos sitä ei löydy RAM-muistista. Mitä ongelmia voimme löytää itsestämme? No, esimerkiksi kaikki muistikanavat ovat varattuja ja syntyy kilpailu, joka tapahtuu, kun RAM on miehittänyt muistikanavat ja vastaanottaa tai toimittaa muuta dataa.

Kuinka viive vaikuttaa kaistanleveyteen?

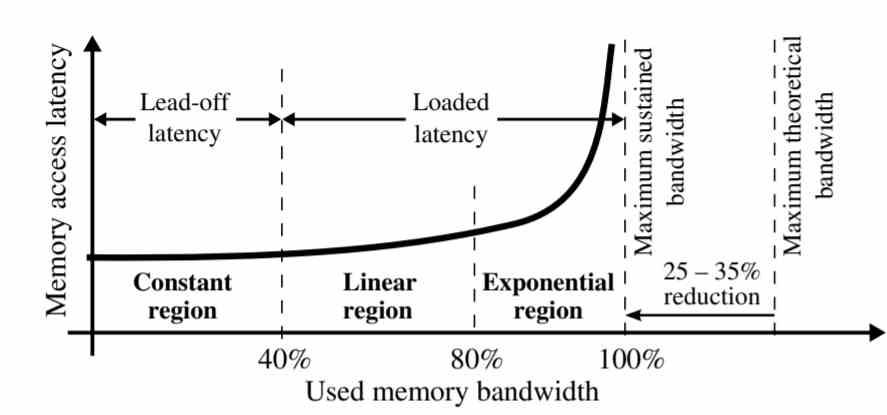

Kuten kaaviosta nähdään, latenssi ei ole sama kaikille muistin kaistanleveyksille.

- Vakioalue: Latenssi pysyy vakiona 40%: lla jatkuvasta kaistanleveydestä.

- Lineaarinen alue: 40–80% jatkuvasta kaistanleveydestä latenssi kasvaa lineaarisesti. Tämä johtuu siitä, että muistipyyntöjä on ylikuormitettu, jotka ovat kertyneet loppuun kilpailun vuoksi.

- Eksponentiaalinen alue: Kaistanleveysosan viimeisten 20 prosentin osassa datan viive kasvaa eksponentiaalisesti, kaikki muistipyynnöt, joita ei voitu ratkaista edellisen jakson aikana, kerääntyvät tähän osaan ja luovat kiistoja niiden välille.

Tällä ilmiöllä on hyvin yksinkertainen selitys, ensimmäiset muistipyynnöt, joihin vastataan, ovat ne, jotka löytyvät ensin, suurin osa niistä on välimuistissa, kun sillä on kopio, mutta ne, jotka eivät ole välimuistissa, kertyvät. Yksi eroista välimuistien ja RAM-muistin välillä on se, että edellinen voi tukea useita samanaikaisia pääsyjä, mutta kun tietojen haku tapahtuu RAM-muistissa, viive on paljon suurempi.

Meillä on tapana kuvitella RAM-muistia eräänlaiseksi vesivirraksi, jossa tiedot eivät lopu kiertämään määritetyllä nopeudella, kun RAM ei todellakaan aio siirtää tietoja, ellei sillä ole siihen pyyntöä. Toisin sanoen latenssi vaikuttaa läpimenoon ja siten kaistanleveyteen.

Tapoja vähentää latenssia

Kun tiedämme, että kilpailu tietojen saannissa luo viiveen ja tämä vaikuttaa kaistanleveyteen, on ajateltava ratkaisuja. Selkein asia on se, että muistikanavien määrää lisätään RAM-muistilla, juuri tämä on yksi avaimista, joilla HBM-muistilla on pienempi viive kuin GDDR6: lla, koska 8 muistikanavaa sallivat vähemmän kiistoja kuin kahdella GDDR2-kanavalla.

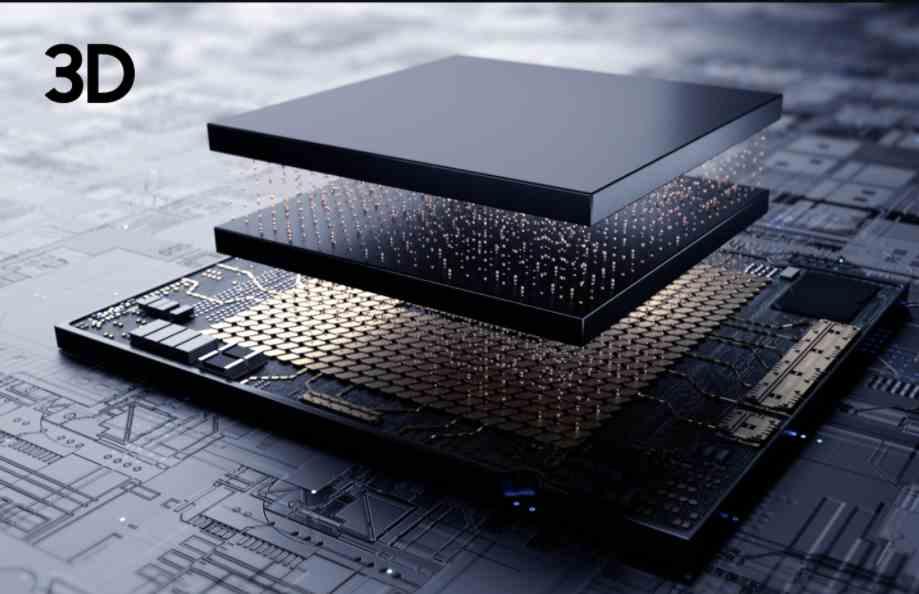

Paras tapa vähentää viivettä olisi luoda muistia niin lähelle prosessoria kuin välimuisti, mutta on mahdotonta luoda RAM-muistia, jolla on riittävästi tallennuskapasiteettia ollakseen täysin toimiva. Voimme sijoittaa muistisirun ja liittää sen TSV: n kautta, mutta koska muisti on niin lähellä termisen hukkumisen ja sen tehokkaan kaistanleveyden välttämiseksi.

Tässä tapauksessa, koska latenssi vaikuttaa kaistanleveyteen muistin ja prosessorin läheisyyden vuoksi, latenssin vaikutus muistiin olisi paljon pienempi. Kompromissi suorittimen tai GPU: n toteuttamisesta 3DIC: n kanssa? Se kaksinkertaistaisi PC: n kustannukset ja monimutkaisempi valmistusprosessi saisi meidät vähemmän yksikköjä, lisäisi niukkuutta ja siten jopa kalliimpia hintoja.