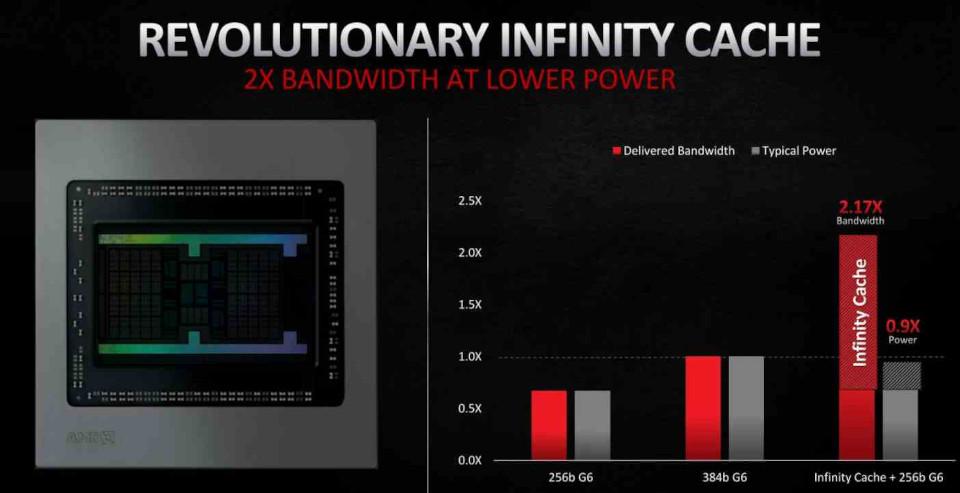

Infinity Cache on merkittävin ero äskettäin esiteltyjen RX 6000 -sarjan näytönohjainten (RX 6800, RX 6800 XT ja RX 6900) välillä Xbox Sarja X SoC GPU, joka perustuu myös RDNA 2: een. ¿Mutta mikä on Infinity Cache, mikä on sen käyttö ja miten se toimii? Kerromme sinulle kaikki sen salaisuudet.

RX 6000: n esittelyä edeltävistä viikoista lähtien olemme tienneet tämän valtavan muistialueen olemassaolon GPU: n sisällä, valtava, koska puhumme GPU: n historian suurimmasta välimuistista 128 Mt kapasiteettia . Mutta AMD ei ole antanut paljon tietoa siitä, se on yksinkertaisesti kertonut meille olemassaolostaan.

Siksi tarvitaan yksityiskohtainen selitys sen ymmärtämiseksi, miksi AMD on asettanut vastaavan kokoisen välimuistin RDNA 2 PC: lle -versioon.

Infinity-välimuistin sijainti

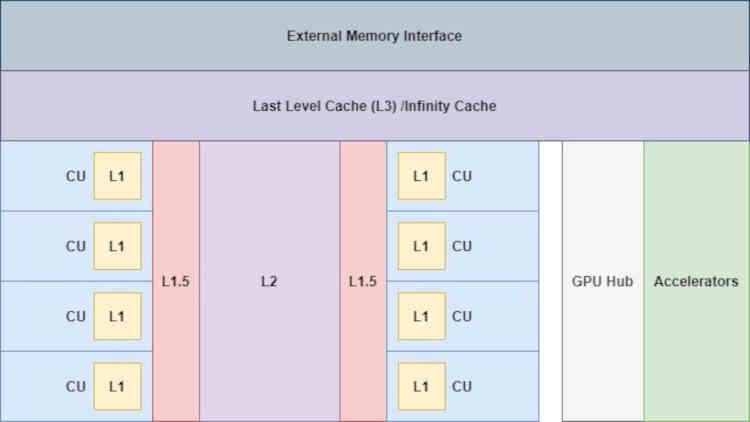

Ensimmäinen asia, joka on tarpeen sen ymmärtämiseksi, mikä pala on laitteistossa, on päätellä sen toiminta sen sijainnista järjestelmässä.

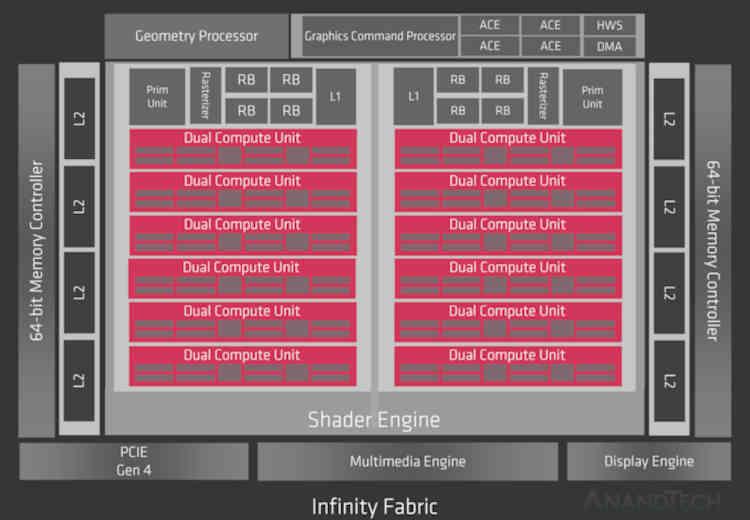

Koska RDNA 2 on RDNA: n evoluutio Ensinnäkin meidän on tarkasteltava nykyisen AMD-grafiikkaarkkitehtuurin ensimmäistä sukupolvea, josta tunnemme kaksi sirua, jotka ovat Navi 10 ja Navi 14.

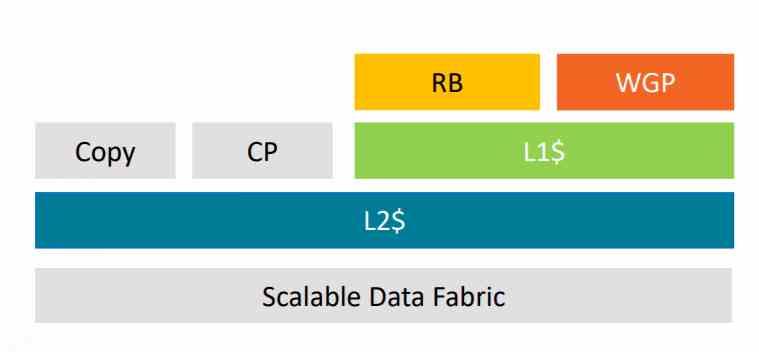

No, jos Infinity Cache olisi otettu käyttöön RDNA: ssa, se olisi siinä osassa, joka sanoo kaavion Infinity Fabric, joten välimuistin organisaatiotasolla menisimme tästä:

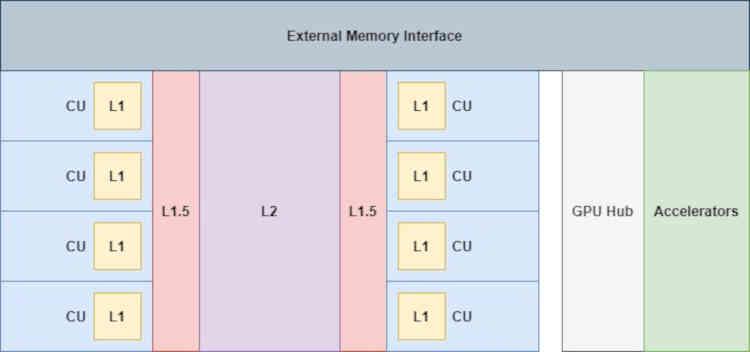

Jos GPU-keskittimeen kytketyillä kiihdyttimillä (videokoodekilla, näytön ohjaimella, DMA-asemilla jne.) Ei ole suoraa pääsyä välimuistiin, edes L2-välimuistiin.

Infinity-välimuistin lisäämisen myötä asiat muuttuvat jo vähän, koska nyt kiihdyttimillä on pääsy tähän muistiin,

Tämä on erittäin tärkeää, etenkin Display Core Nextille, joka on vastuussa lopullisen kuvapuskurin lukemisesta ja lähettämisestä vastaavaan näyttöporttiin tai HDMI-liitäntään niin, että kuva näkyy näytöllä, mikä on tärkeää pääsyjen vähentämiseksi. näiden yksiköiden VRAM: lle.

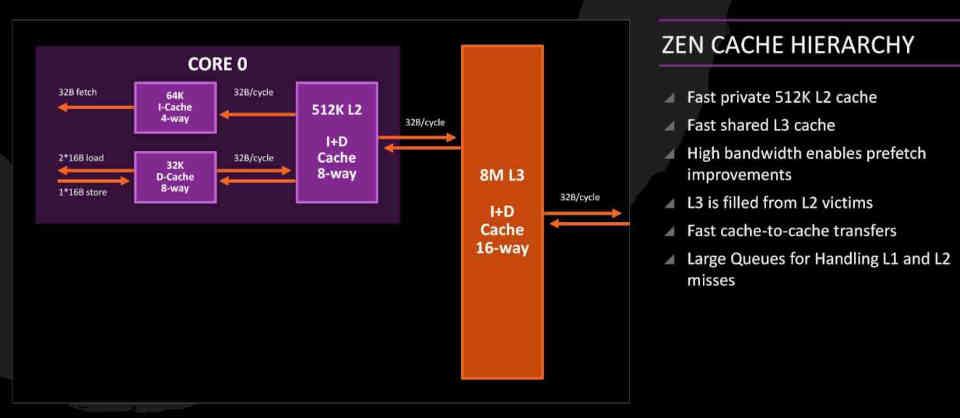

Muistetaan RDNA-välimuistijärjestelmä

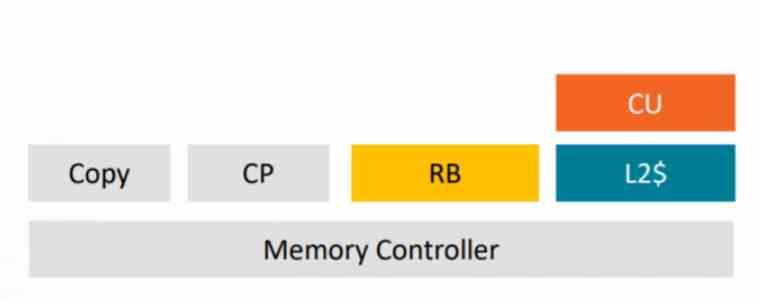

RDNA: ssa välimuistit on kytketty toisiinsa seuraavasti:

L2-välimuisti on kytketty ulkopuolelle 16 kanavaan, joissa on 32 tavua / sykli, jos tarkastelemme Navi 10 -kaaviota, näet kuinka tällä GPU: lla on noin 16 L2-välimuistiosiota ja 256-bittinen GDDR6-väylä johon he ovat yhteydessä.

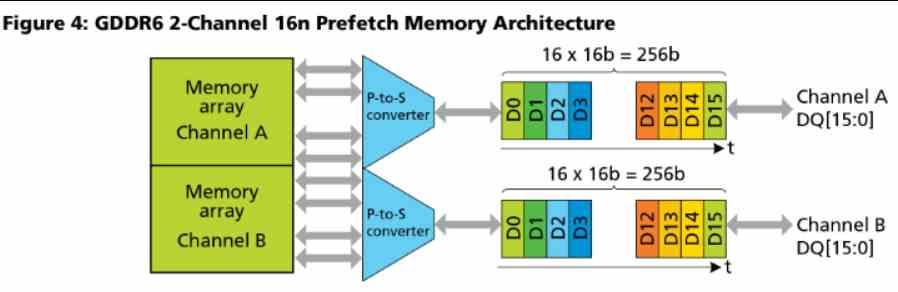

Muista, että GDDR6 käyttää kahta kanavaa sirua kohden jotka toimivat rinnakkain, kukin 16 bittiä.

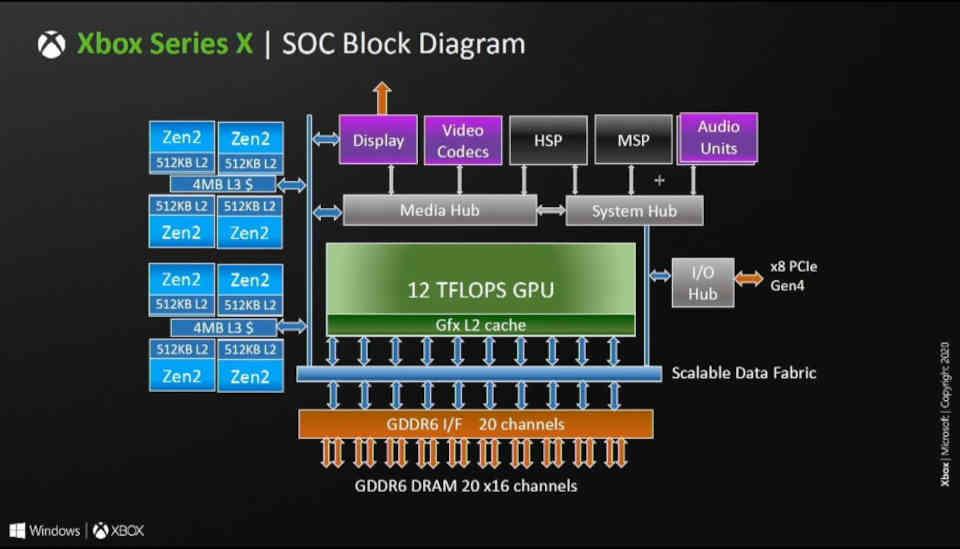

Toisin sanoen LNA-välimuistiosioiden määrä RDNA-arkkitehtuureissa on yhtä suuri kuin grafiikkaprosessoriin kytkettyjen 2-bittisten GDDR16-kanavien määrä. RDNA: ssa ja RDNA 6: ssa kukin osio on 2 kt, tämä on syy, miksi Xbox Series X: ssä, jossa on 256-bittinen väylä ja siten 320 GDDR20-kanavaa, on noin 6 Mt L5-välimuistia.

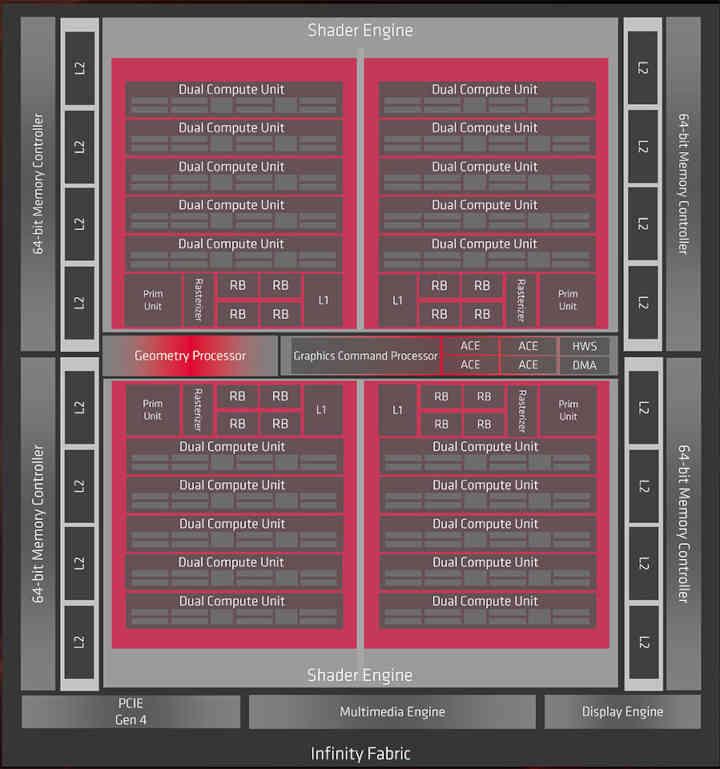

Uusi välimuistitaso: Infinity Cache

Koska kyseessä on ylimääräinen välimuistitaso, Infinity-välimuisti on liitettävä suoraan L2-välimuistiin, joka on välimuistihierarkian edellinen taso, tämän vahvistaa meille AMD alatunnisteessa:

AMD-insinöörien laskema mittaus Radeon RX 6000 -sarjan kortilla 128MB AMD Infinity Cache ja 256-bittinen GDDR6. Mitataan keskimääräiset AMD Infinity Cache -menestysprosentit 4k-peleissä 58% suurimmissa peleissä kerrottuna 16 64B AMD Infinity Fabric -kanavaa välimuistin liittäminen grafiikkamoottoriin jopa 1.94 GHz: n tehostustaajuudella.

RX 6800: n, RX 6800 XT: n ja RX 6900: n GPU on Navi 21, jolla on 256-bittinen GDDR6-väylä, ergo: lla on 16 kanavaa ja siten Caché L16: n 2 osiota, jotka kukin on yhdistetty Infinity Cache -osioon.

Mitä tulee 58 prosentin osumaprosentteihin, se on monimutkaisempi ja yritämme selittää alla.

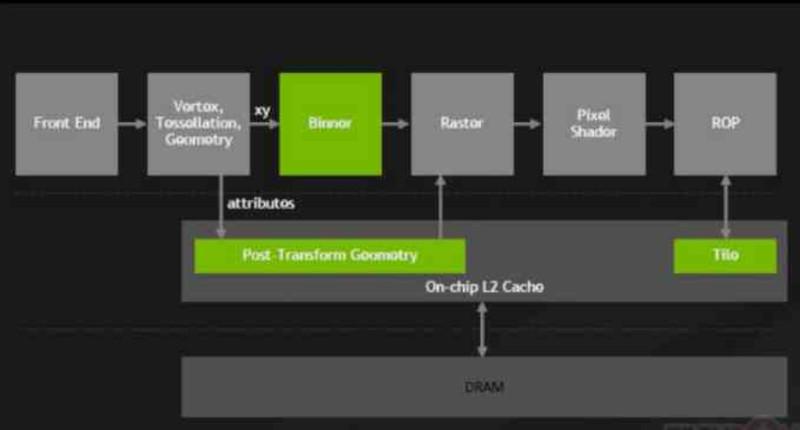

Laattojen välimuisti NVIDIA-näytönohjaimissa

Ennen kuin jatkamme Infinity Cache -ohjelmaa, meidän on ymmärrettävä sen olemassaolon syyt ja tätä varten on tarkasteltava, kuinka GPU: t ovat kehittyneet viime vuosina.

Alkaen NVIDIA Maxwell, GeForce 900 -sarja, NVIDIA teki merkittävän muutoksen grafiikkasuorittimissaan, jota he kutsuivat nimellä Tile Caching, jonka muutokseen liittyi ROPS ja rasteriyksikkö L2-välimuistiin.

Tämän muutoksen myötä ROPS lopetti kirjoittamisen suoraan VRAM-muistiin, ROPS on yleinen kaikissa GPU: issa ja vastaa kuvapuskurien luomisesta muistiin.

Tämän muutoksen ansiosta NVIDIA pystyi vähentämään muistiväylän energiavaikutuksia vähentämällä VRAM: lle ja sieltä tapahtuvien siirtojen määrää. Tämän avulla NVIDIA onnistui saamaan energiatehokkuuden AMD: ltä Maxwell- ja Pascal-arkkitehtuureilla.

DSBR, Tile Caching AMD-näytönohjaimissa

AMD toisaalta GEG-arkkitehtuurin kaikkien sukupolvien ajan ennen Vegaa, yhdisti Render Backends (RB) suoraan muistin ohjaimeen.

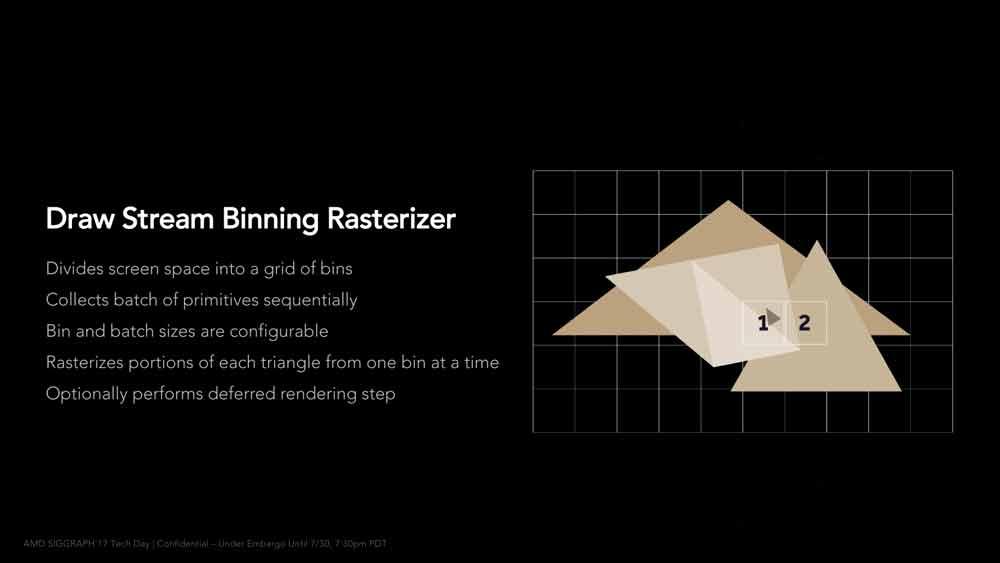

Mutta aloittaen AMD Vegasta, hän teki kaksi muutosta arkkitehtuuriin lisätäksesi Tile-välimuistin näytönohjaimiinsa, joista ensimmäinen oli uudistaa rasteriyksikkö, jonka hän nimitti uudelleen DSBR: ksi, Draw Stream Binning Rasterizer.

Toinen muutos oli se, että he liittivät rasterikokonaisuuden ja ROPS: n L2-välimuistiin, joka on edelleen RDNA: ssa ja RDNA 2: ssa.

DSBR- tai Tile Caching -apuohjelma

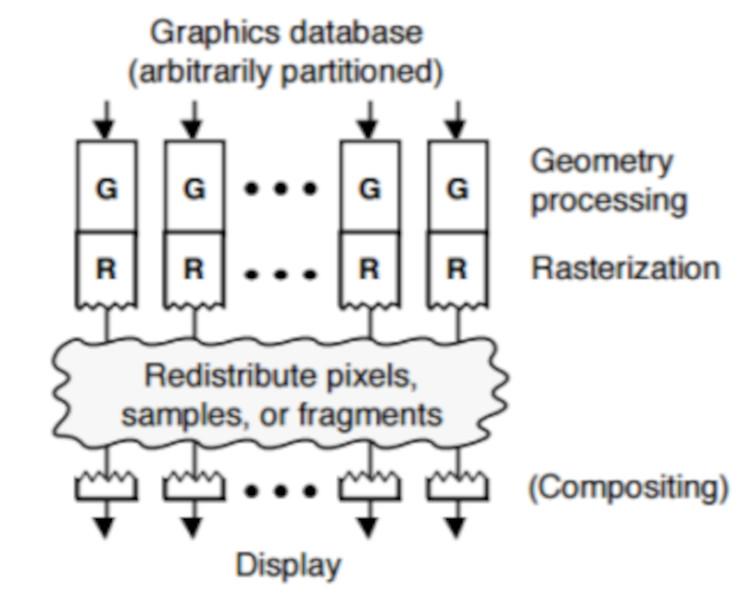

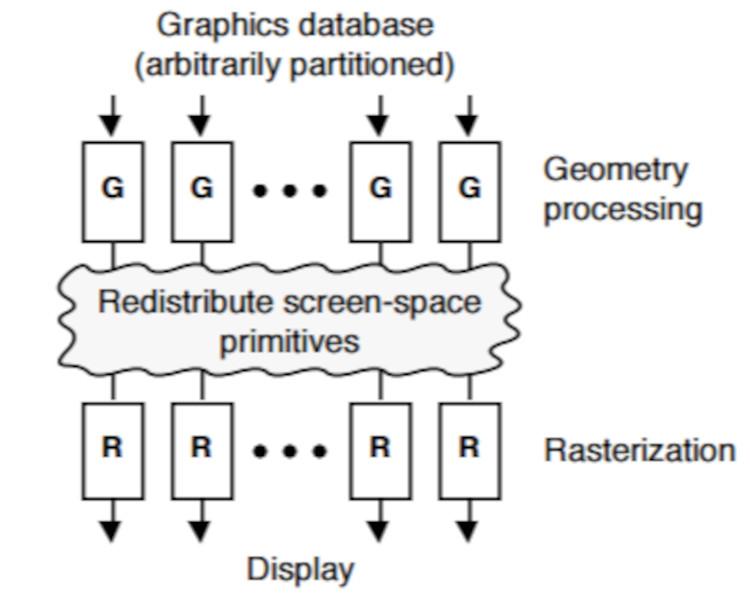

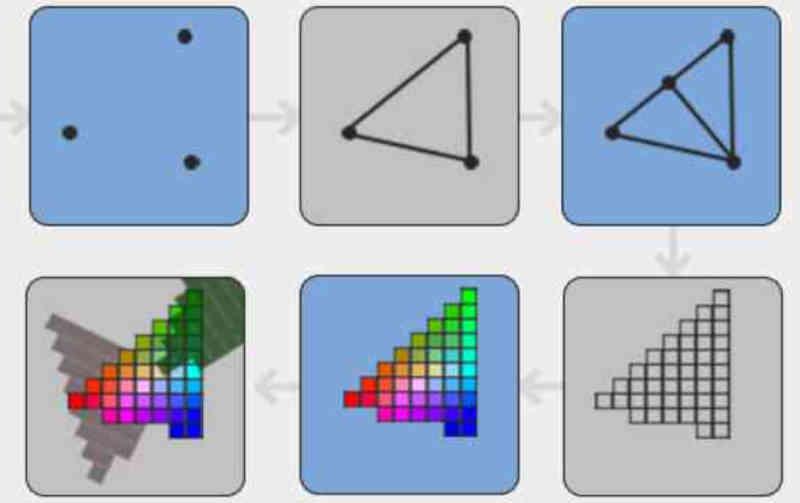

Tile Caching tai DSBR on tehokas, koska se järjestää näkymän geometrian sijainnin mukaan näytöllä ennen kuin se rasteroidaan, tämä oli tärkeä muutos, koska GPU: t ennen tämän tekniikan käyttöönottoa tilasi jo kuvioidut fragmentit juuri ennen niiden lähettämistä kuvapuskuriin.

Tile Caching / DSBR: ssä tehdään järjestää kohtauksen polygonit ennen kuin ne muunnetaan sirpaleiksi rasterointiyksikkö.

Ruudun välimuistissa polygonit järjestetään niiden ruuduissa olevan sijainnin mukaan, missä kukin ruutu on fragmentti n * n pikseliä.

Yksi tämän eduista on, että se sallii etukäteen eliminoida fragmenttien näkymättömät pikselit, jotka ovat läpinäkymättömiä samassa tilanteessa ollessaan. Jotain, jota ei voida tehdä, jos kohtauksen muodostavat elementit järjestetään teksturoinnin jälkeen.

Tämä säästää GPU: ta tuhlaamasta aikaa turhiin pikseleihin ja parantaa GPU: n tehokkuutta. Siinä tapauksessa, että tämä tuntuu hämmentävältä, on yhtä yksinkertaista kuin muistaa, että koko graafisessa putkessa kohtauksen muodostavat erilaiset primitiivit ovat eri muodoissa sen eri vaiheissa.

Tile Caching tai DSBR ei vastaa Tile Rendering -toimintoa

Vaikka nimi voi olla harhaanjohtava, Tile Caching ei vastaa Tile Renderingia seuraavista syistä:

- Laattojen renderöijät tallentavat näkymän geometrian muistiin, tilaavat sen ja luovat ruutulistoja kullekin ruudulle. Tätä prosessia ei tapahdu laattojen välimuistin tai DSBR: n tapauksessa.

- Tile Rendering -ohjelmassa ROPS on liitetty tyhjennyslevymuistiin välimuistihierarkian ulkopuolelle, eivätkä ne tyhjennä niiden sisältöä VRAM: iin, ennen kuin kyseinen ruutu on 100% valmis, joten osumisprosentit ovat 100%.

- Koska laattojen välimuistissa / DSBR: ssä, koska ROPS / RB: t on kytketty L2-välimuistiin, välimuistilinjat L2: sta RAM-muistiin voidaan milloin tahansa hylätä, joten ei voida taata, että 100% tiedoista on L2-välimuistissa.

Koska on todennäköistä, että välimuistilinjat päätyvät VRAM-muistiin, AMD on tehnyt Infinity-välimuistin kanssa lisäämällä välimuistikerroksen, joka kerää hylätyt tiedot GPU: n L2-välimuistista.

Infinity Cache on uhrin välimuisti

- Uhri Caché idea on Zen-arkkitehtuureissa olevien CPU: iden perintö, joka on mukautettu RDNA 2: een.

Zen-ytimissä L3-välimuisti on se, jota me kutsumme uhri-välimuistiksi hylättyjen välimuistilinjojen kerääminen L2: sta sen sijaan, että se olisi osa tavallista kätkö hierarkia. Toisin sanoen Zen-ytimissä peräisin olevat tiedot RAM ei seuraa RAM-polkua → L3 → L2 → L1 tai päinvastoin, vaan seuraa RAM-polkua → L2 → L1, koska L3-välimuisti toimii uhrin välimuistina.

Infinity-välimuistin idea on pelastaa GPU: n L2-välimuistin linjat tarvitsematta käyttää VRAM-muistia , joka sallii käskyä kohden kulutetun energian olevan paljon pienempi ja siten saavutettavissa suuremmat nopeudet. kello.

Vaikka 128 Mt: n kapasiteetti saattaa tuntua erittäin korkealta, se ei näytä riittävältä välttää sitä, että kaikki hävitetyt linjat päätyvät VRAM: iin, koska parhaimmissa tapauksissa se onnistuu pelastamaan vain 58% . Tämä tarkoittaa, että tulevaisuudessa sen RDNA-arkkitehtuurin iteraatiot ovat hyvin todennäköisiä AMD lisää tämän Infinity-välimuistin kapasiteettia .