Der Markt für Grafikprozessoren oder GPUs, ob in Form von Grafikkarten oder integrierten GPUs, wird derzeit von besetzt NVIDIA, AMD und in geringerem Maße Intel. Bedeutet dies, dass es nicht möglich ist, eine zu bauen? GPU das nutzt keine kommerzielle Technologie? Die Lösung kann in der Verwendung des völlig kostenlosen und offenen ISA RISC-V in einer Variante für Grafiken unter dem Namen RV32X liegen

Die Leute von Pixilica, Schöpfer der CPU basierend auf dem ISA RISC-V namens SiFive haben wir einen Vorschlag namens RV32X gemacht, der darauf abzielt, GPUs mit dem ISA RISC-V zu erstellen. Was durch die völlig freie und offene Natur von RISC-V die Zukunft von GPUs komplett verändern könnte.

RV32X, Anwendung von RISC-V zum Erstellen einer GPU

Der RISC-V-Standard ist ein völlig kostenloser und offener Satz von Registern und Gebrauchsanweisungen, der auf einer Basisspezifikation und einer Reihe optionaler Erweiterungen für die Erstellung von CPUs für verschiedene Arten von Anwendungen und Dienstprogrammen basiert. Aber ist es möglich, mit RISC-V Shader-Einheiten wie NVIDIAs SMs oder AMDs Compute Units zu erstellen? Zunächst nicht, und eine neue Erweiterung des ISA wäre erforderlich, um daraus eine Shader-Einheit zu erstellen.

Das Unternehmen Pixilica hat die Schaffung einer GPU vorgeschlagen, bei der die Shader-Einheiten auf dem ISA RISC-V basieren, und dazu eine zusätzliche Erweiterung des ISA RISC-V mit einer Reihe von Anweisungen vorgeschlagen, mit denen Sie grafische Grundelemente bearbeiten können. Sei es Pixel, Eckpunkte und andere Arten von Daten, die beim Echtzeit-Grafik-Rendering verwendet werden.

Zu diesem Zweck schlagen sie vor, die V-Erweiterung für RISC-V-Vektoranweisungen zu verwenden und die Liste der Anweisungen daraus zu erweitern, um die Shader-Einheit zu erstellen.

Was sind die Komponenten einer Shader-Einheit?

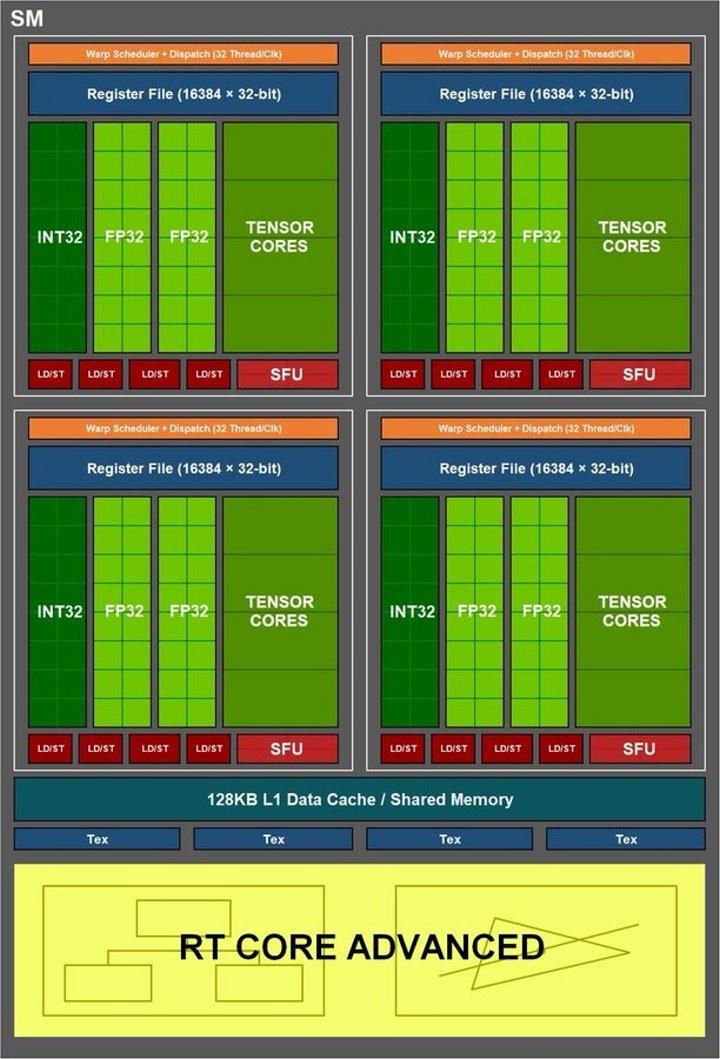

Jede Shader-Einheit, unabhängig von der Marke, über die wir sprechen, hat die folgenden Komponenten:

- Ein Decoder, Scheduler, der die Wellen von Ausführungsthreads aufnimmt und organisiert.

- Eine Reihe von Registern, auf die der Planer die von den ALUs oder Ausführungseinheiten auszuführenden Threads in geordneter Weise legt.

- ALUs oder Ausführungseinheiten mit der Fähigkeit, arithmetische und logische Operationen an den Daten auszuführen. Dies können Vektor oder SIMD und Skalar sein.

- Textureinheiten zur Interpolation von Texturpixeln. Diese Einheiten haben eine feste Funktion.

- Cache der obersten Ebene für Daten

- Möglichkeit, Daten aus dem Datencache in höhere Ebenen des Caches zu exportieren, jedoch weiter von der Shader-Einheit entfernt, und auch in den ROPS zu exportieren

- Ein Anweisungscache, der für jede Shadereinheit intern sein oder von mehreren gemeinsam genutzt werden kann.

Sobald die gemeinsamen Grundelemente bekannt sind, werfen wir einen Blick auf den Vorschlag von Pixilica.

Der RV32X, eine RISC-V-basierte Shader-Einheit

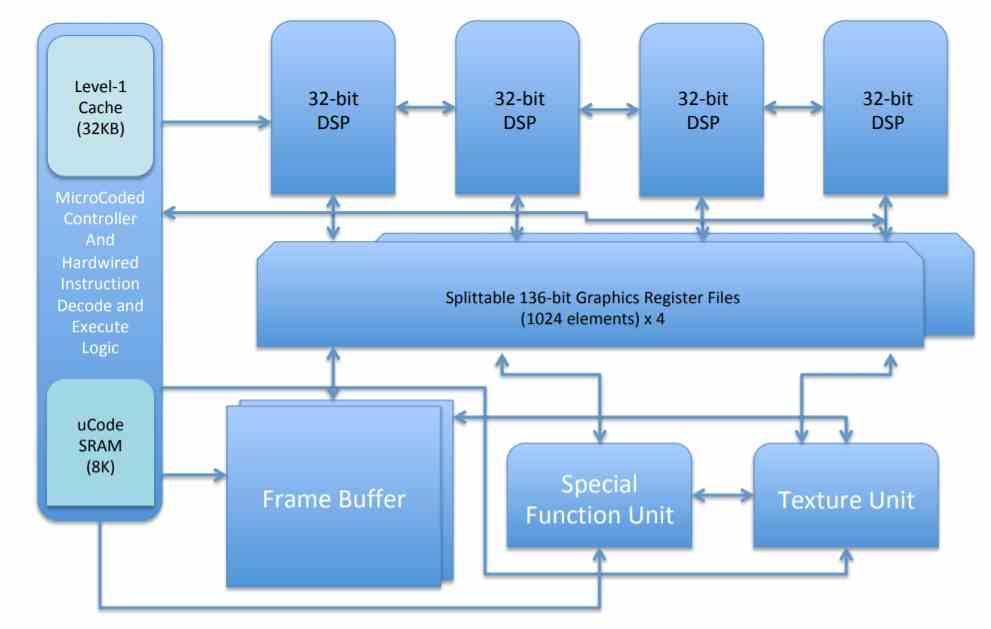

Das erste, was wir beachten müssen, ist, dass der Standard für Vektoren in RISC-V bis zu 128 Bit unterstützt, was wie folgt implementiert werden kann: 1 128-Bit-Operation, 2 64-Bit, 4 32-Bit, 8 16 Bit oder 16 8 Bit. Wir bezeichnen diese Fähigkeit, die Präzision in jeder ALU zu halbieren, als überregistrierte SIMD. Im vorliegenden Fall wird vorgeschlagen, 4 32-Bit-ALUs im Gleitkomma zu platzieren.

Die andere Art von Einheiten sind die sogenannten Sonderfunktionseinheiten, die im Entwurf skalar und mit einer ganzzahligen Genauigkeit von 16 Bit sein werden. Die Anweisungen, die sie ausführen würden, wären die transzendentalen Aufrufe. Das heißt, Sinus, Cosinus, Tangens, Potenzen, Logarithmen und Wurzeln unterschiedlichen Grades. Die aufgrund der Kosten für Transistoren in einer SIMD-Einheit schwer zu implementieren sind.

Ein Unterschied in Bezug auf die in einer CPU verwendeten SIMD-Einheiten wäre, dass die Register nicht 128 Bit, sondern 136 Bit wären, wobei die ersten 8 Bits dazu dienen würden, den Typ des zu verarbeitenden Grafikprimitivs oder der zu verarbeitenden Daten zu definieren. Die 8 Bits erlauben bis zu 256 Datentypen, daher gibt es einen großen Spielraum, um sie zu definieren. Einige der Datentypen ermöglichen die Interaktion mit den verschiedenen festen Funktionseinheiten in der GPU sowie mit dem VRAM.

Insgesamt haben wir ungefähr 4 Register-Wells, von denen jedes 1024 verschiedene Elemente mit jeweils 136 Bit enthält. Dies ist derzeit der maximale Block von Ausführungsthreads in APIs wie Direct3D in DirectX. Jedes der Mannlöcher ist mit einer 4-ALU-32-Bit-Gleitkomma-SIMD-Einheit verbunden. Dies entspricht 16 ALUs pro Mannloch, was durch die Anweisungsunterstützung mit 4 x 4 Elementmatrizen bestätigt würde.

Dekodierungsanweisungen auf dem RV32X

Die Decodierung der Anweisungen würde in einem Decodierer mit fester Funktion erfolgen. Es muss berücksichtigt werden, dass die Anweisungen 32 Bit lang und daher von fester Größe sind. Diese würden über den Befehls-Cache ankommen, während sich die Daten für jeden Befehl auch im Daten-Cache innerhalb der Recheneinheit befinden würden. Die Verwendung eines Mikrocode-Befehlsdecoders ist ebenfalls möglich.

Der Vorschlag beinhaltet die Integration eines Standard-RISC-V-Kerns, der dem RV32X beiliegt. Dies bedeutet nicht, dass er zu einer typischen CPU wird, sondern dass er zur Integration der für GPUs typischen Round-Robin-Ausführung verwendet wird, die auf give basiert Jeder Befehl eine Ausführungszeit. Wenn es nicht in der angegebenen Zeit ausgeführt wird, normalerweise aufgrund fehlender Daten. Dann geht es zurück in die Liste.

Es muss berücksichtigt werden, dass die ALUs der Shader-Einheiten die Anweisungen der verschiedenen Ausführungsthreads in Kaskade ausführen, wenn sie aus den Registern ankommen. Wenn der Scheduler die Register mit den Daten aus den Datencaches und Anweisungen gefüllt hat, wenn sie von den ALUs wie ein Stapel betrieben werden, lesen die ALUs nach dem Auflösen einer Gruppe von Anweisungen die nächste Gruppe, bis alle durchlaufen sind Protokolle und es sind keine Threads auszuführen.

Feste Funktion bei RV32X

Die festen Funktionseinheiten sind auf die gleiche Weise wie die übrigen Beschleuniger im RV32X nicht definiert, aber die Anweisungen, die die Interaktion mit ihnen von den Shader-Einheiten aus ermöglichen, sind. Diese Einheiten sind dafür verantwortlich, immer die gleiche Funktion auszuführen, da sie verkabelt sind oder einen festen Mikrocode verwenden. In jedem Fall handelt es sich jedoch in den meisten Fällen um Einheiten, die vollständig vom RV32X getrennt sind.

Daher hätte jeder Hersteller seine eigenen festen Funktionseinheiten und deren Implementierung. Sowie das Erstellen von proprietären Erweiterungen für den Fall, dass diese zusätzliche Funktionen für den gemeinsamen Betrieb derselben implementiert hatten. Beachten Sie, dass der RV32X keine vollständige GPU definiert, sondern eine Shader-Einheit, die Teil einer GPU ist. Dies ist wichtig, da die verschiedenen Shader-Typen ausgeführt werden, jedoch nicht die gesamte GPU.

Als Hinweis, in Bezug auf Textureinheiten haben wir eine pro Mannloch. Beachten Sie, dass das übliche Verhältnis zwischen ALUs in SIMD-Einheiten in den meisten GPUs normalerweise 16: 1 beträgt. Innerhalb jeder Shader-Einheit werden normalerweise vier Textureinheiten angezeigt, wodurch das Verhältnis für jede Shader-Einheit im Durchschnitt auf 64 32-Bit-Gleitkomma-ALUs erhöht wird.

Eröffnet dies eine neue Niederlassung auf dem GPU-Markt?

Abgesehen vom technischen Teil werden wir beim Blick auf den Markt für PostPC-Geräte und die ihnen zugewiesenen SoCs feststellen, dass eine große Anzahl integrierter GPUs vollständig proprietär ist. Bisher wurde in MalCs, die in China hergestellt wurden, am häufigsten die Mali-Architektur verwendet, jedoch mit dem Kauf von ARM von NVIDIA schränkt dies die Möglichkeiten ein. Qualcomm besitzt die Adreno-Architektur, Apple hat auch seine eigenen, und selbst Imagination mit PowerVR bedeutet, dass ein Dritter lizenziert werden muss, um die Technologie zu nutzen.

Die Tatsache, dass es einen Vorschlag für eine auf RISC-V basierende Shader-Einheit gibt, ist von entscheidender Bedeutung, da damit neue GPUs auf der Grundlage eines Standards erstellt werden können, der völlig kostenlos und daher nicht proprietär ist. Dies bedeutet, dass neue Einheiten und Verbesserungen geschaffen werden können, die gemeinsame Probleme lösen, anstatt gleichzeitig aus verschiedenen Perspektiven nach derselben Lösung zu suchen.

Wenn wir uns eine Weltmacht ansehen wollen, die von einer solchen Technologie profitieren kann, ist klar, dass China als erstes in den Sinn kommt, aber wir können auch eine Entwicklung von AMD, NVIDIA oder Intel sehen, um die RISC-V-Version zu nutzen Baue Shader-Einheiten, um vom gemeinsamen Fortschritt zu profitieren. Genauso wie es in Software und der Open Source-Welt passiert.