Wenn es darum geht, die Leistung von zu messen RAM und VRAM sprechen wir normalerweise über zwei Leistungsparameter, nämlich Bandbreite und Latenz. Aber wie ist die Beziehung zwischen diesen beiden Merkmalen und können wir sie als konstant klassifizieren?

Eines der Probleme mit technischen Spezifikationen besteht darin, dass die Daten unter perfekten Bedingungen mit 100% Leistung ausgeführt werden. Im Fall von Speicher geschieht dies nicht, da nicht alle Daten die gleiche Latenz haben und die Bandbreite niemals 100% beträgt.

Mehr Bandbreite bedeutet nicht weniger Latenz

Wir verstehen als Latenz zwischen einer Verarbeitungseinheit und dem zugehörigen Speicher die Zeit, die benötigt wird, um eine angeforderte Information zu empfangen oder das Signal zu empfangen, dass eine Änderung im Speicher vorgenommen wurde. Die Latenz ist also wirklich eine Möglichkeit, die Zeit zu messen.

Die Bandbreite ist stattdessen die Datenmenge, die in jeder Sekunde übertragen wird, also eine Geschwindigkeitsrate. Durch direkte Logik können wir also denken, dass bei einer höheren Geschwindigkeit, wenn wir nach Daten suchen, in kürzerer Zeit die CPU, GPU oder eine andere Verarbeitungseinheit erhält die Daten.

Die Realität ist, dass dies nicht der Fall ist. Darüber hinaus gibt es die Besonderheit, dass je mehr Bandbreite ein Speicher hat, desto mehr Latenz hat er normalerweise im Vergleich zu anderen. Dieses Phänomen hat eine Erklärung, die wir Ihnen in den folgenden Abschnitten dieses Artikels erklären werden.

Durch die Suche nach Daten wird die Latenz erhöht

Fast alle Verarbeitungseinheiten haben heutzutage eine Hierarchie von Caches, in denen der Prozessor jeden von ihnen zuerst fragt, bevor er auf RAM zugreift. Dies liegt daran, dass die direkte Latenz zwischen Prozessor und RAM groß genug ist, um einen Leistungsverlust gegenüber dem idealen Prozessor zu verursachen.

Stellen Sie sich vor, Sie suchen nach einem bestimmten Produkt. Als erstes suchen Sie im örtlichen Geschäft, dann in einem etwas größeren Geschäft und schließlich in einem Kaufhaus. Der Besuch in jeder Einrichtung erfolgt nicht sofort, sondern erfordert Reisezeit. Dasselbe passiert in der Cache-Hierarchie. Dies wird als "Cache-Miss" bezeichnet, sodass wir die Zeit wie folgt zusammenfassen können:

Suchzeit = Suche Zeit im ersten Cache + Cache-Fehlperiode +… Suchzeit im letzten Cache.

Wenn die Cache-Suchzeit länger ist als die Zeit, die benötigt wird, um zum Haupt-RAM zu gelangen, ist das Cache-System auf einem Prozessor schlecht ausgelegt, da es dem Zweck widerspricht, für den der Cache erstellt worden wäre.

Das Latenzproblem ist jetzt komplexer, da wir zu der durch die Cache-Suche hinzugefügten Zugriffszeit die Latenz hinzufügen müssen, die hinzugefügt wird, um die Daten im RAM zu durchsuchen, wenn sie nicht im RAM gefunden werden. Mit welchen Problemen können wir uns konfrontiert sehen? Nun, zum Beispiel sind alle Speicherkanäle belegt und es wird ein Konflikt erzeugt, der auftritt, wenn der RAM Speicherkanäle belegt hat und andere Daten empfängt oder liefert.

Wie wirkt sich die Latenz auf die Bandbreite aus?

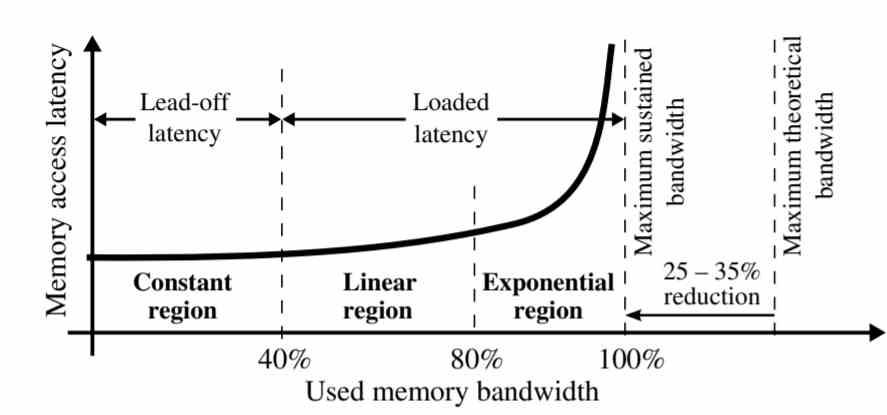

Wie in der Grafik dargestellt, ist die Latenz nicht für alle Speicherbandbreiten gleich.

- Konstante Region: Die Latenz bleibt konstant bei 40% der anhaltenden Bandbreite.

- Linearer Bereich: Zwischen 40 und 80% der anhaltenden Bandbreite steigt die Latenz linear an. Dies liegt an der Tatsache, dass es eine Übersättigung von Anforderungen an den Speicher gibt, die sich am Ende aufgrund von Konflikten angesammelt haben.

- Exponentielle Region: In den letzten 20% des Bandbreitenabschnitts nimmt die Datenlatenz exponentiell zu. Alle Speicheranforderungen, die in der vorherigen Periode nicht gelöst werden konnten, werden in diesem Teil akkumuliert, wodurch Konflikte zwischen ihnen entstehen.

Dieses Phänomen hat eine sehr einfache Erklärung. Die ersten Anfragen an den Speicher, die beantwortet werden, sind diejenigen, die zuerst gefunden werden. Die meisten befinden sich im Cache, wenn diese eine Kopie haben, aber diejenigen, die nicht im Cache sind, sammeln sich an. Einer der Unterschiede zwischen Caches und RAM besteht darin, dass erstere mehrere gleichzeitige Zugriffe unterstützen können. Wenn jedoch im RAM nach Daten gesucht wird, ist die Latenz viel höher.

Wir neigen dazu, uns RAM als eine Art Wasserstrom vorzustellen, in dem die Daten nicht mit der angegebenen Geschwindigkeit nicht mehr zirkulieren, wenn RAM Daten nicht wirklich verschieben wird, es sei denn, es hat eine Anfrage an sie. Mit anderen Worten, die Latenz beeinflusst den Durchsatz und damit die Bandbreite.

Möglichkeiten zur Reduzierung der Latenz

Sobald wir wissen, dass Konflikte beim Zugriff auf Daten zu Latenz führen und dies die Bandbreite beeinflusst, müssen wir über Lösungen nachdenken. Das deutlichste davon ist die Tatsache, dass die Anzahl der Speicherkanäle mit RAM erhöht wird. Genau dies ist einer der Schlüssel, mit denen der HBM-Speicher eine geringere Zugriffslatenz als GDDR6 aufweist, da 8 Speicherkanäle weniger Konflikte zulassen als mit 2 GDDR6-Kanälen.

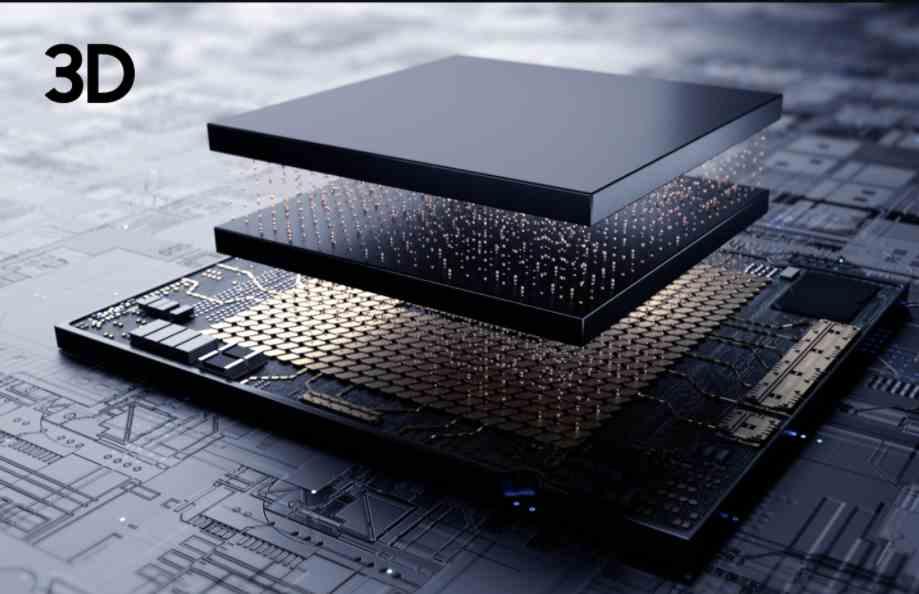

Der beste Weg, um die Latenz zu reduzieren, besteht darin, Speicher so nahe am Prozessor wie einen Cache zu erstellen. Es ist jedoch unmöglich, RAM mit genügend Speicherkapazität zu erstellen, um voll funktionsfähig zu sein. Wir können einen Speicherchip platzieren und über TSV verbinden, aber da der Speicher so nah ist, um ein thermisches Ertrinken und damit die effektive Bandbreite zu vermeiden.

In diesem Fall wäre der Effekt der Latenz auf den Speicher viel geringer, da die Latenz aufgrund der Nähe zwischen Speicher und Prozessor die Bandbreite beeinflusst. Der Kompromiss bei der Implementierung einer CPU oder GPU mit 3DIC? Dies würde die Kosten des PCs verdoppeln und der komplexere Herstellungsprozess würde dazu führen, dass weniger Einheiten uns erreichen, was zu mehr Knappheit und damit zu noch teureren Preisen führen würde.