Aufgrund der mit den neuen Chip-Fertigungstechnologien einhergehenden Kostensteigerung ist es notwendig, einen Chip in mehrere verschiedene zu trennen. Dies ermöglicht eine billigere Herstellung in bestimmten Teilen des Prozessors. Allerdings müssen diese Schnittstellen miteinander kommunizieren, und bis vor kurzem gab es dafür keinen Standard. Vor einigen Wochen wurde dafür der UCIe oder Universal Chiplet Interconnect Express vorgestellt. Dadurch können mehrere unterschiedliche Chips in demselben Gehäuse vorhanden sein. Brunnen, Intel hat neue Informationen über den Standard veröffentlicht.

Der UCIe ist ein Standard, der im vergangenen März vorgestellt wurde. Es ist eine Schnittstelle, um das, was wir Chiplets nennen, miteinander zu kommunizieren und die von Unternehmen wie Intel, TSMC, ARM, Qualcomm, Samsung und Microsoft. Wir stehen also vor einem Standard, den wir in Zukunft in vielen Systemen sehen werden. Nun, wir konnten neue Details darüber erfahren

Was ist die Intensivstation?

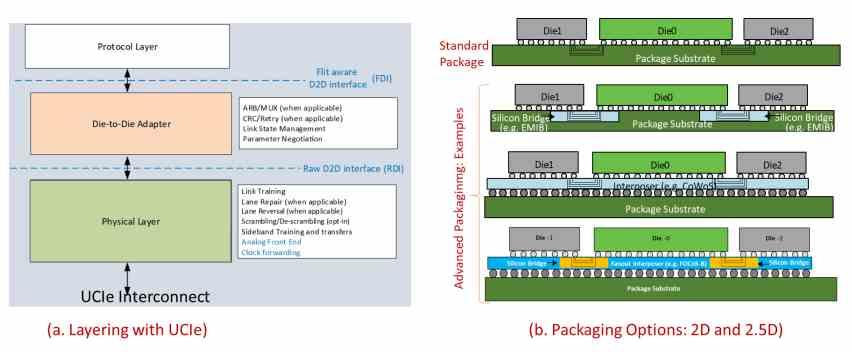

Um zu verstehen, was diese Schnittstelle bedeutet, müssen wir uns vorstellen, dass sie PCI Express sehr ähnlich ist. Im vorliegenden Fall besteht der Unterschied darin, dass es in diesem Fall nicht darum geht, Grafikkarten anzuschließen, sondern sondern Chips auf demselben Substrat oder Interposer miteinander verbinden . Somit können unterschiedliche Chips mit unterschiedlichen Funktionen und Eigenschaften unter demselben Gehäuse untergebracht werden. Bisher war der einzige Prozessor dieser Art AMD's Ryzen, das die Infinity Fabric-Schnittstelle verwendet. Obwohl es sich um eine Version mit Unterstützung für HyperTransport-Speicherkohärenz handelt, ist sie immer noch proprietär von AMD. Daher wurde ein Standard benötigt, der Chiplets mit Technologien mehrerer Marken und nicht nur einer erlaubt.

Nun, Intel hat neue Informationen über die erste Generation dieses Standards gegeben. Welches die Kapazität haben wird, zwischen zu übertragen 12 und 16 Gigabit pro Sekunde an Informationen pro Kontaktstift . Wovon wir im Moment sprechen Bandbreiten äquivalent zu PCI Express 4.0 . Jedoch mit der Verwendung einer viel kürzeren Verdrahtung. Dies stellt eine deutliche Reduzierung des Energieverbrauchs , zwischen 10 und 20 mal . Dies ist jedoch nicht der Hauptvorteil des neuen UCIe-Standards.

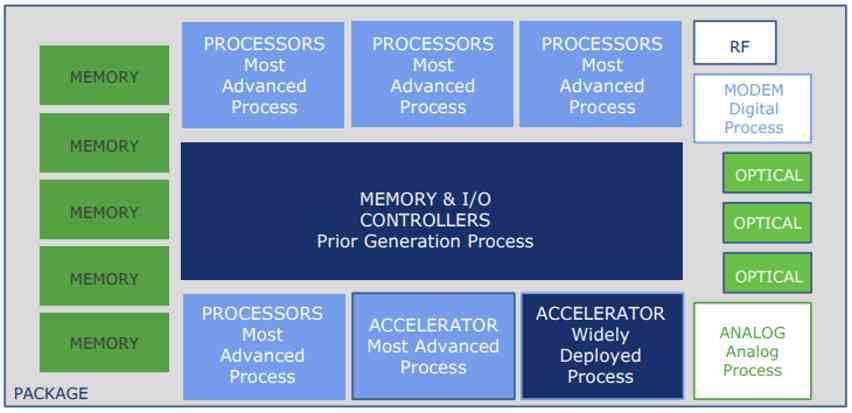

Der andere Vorteil ist, dass es möglich sein wird, zu platzieren Chips verschiedener Marken unter demselben gemeinsamen Substrat. Wie ein Intel-Prozessor und NVIDIA Grafik. Alles unter einem Paket zu haben. Obwohl dies nicht die Norm sein wird, eröffnet es die Kapazität für kundenspezifische Prozessoren für bestimmte spezifische Lösungen. Darüber hinaus ist die UCIe keine Lösung, die sich auf einen einzelnen Chiphersteller konzentriert. Da es kompatibel ist mit Intel-EMIB und TSMC CoWoS-Lösungen .

Unterstützung für konsistente Speichermechanismen

Darüber hinaus wird die UCIe haben Unterstützung für den Compute Express Link und dem Kohärente Hub-Schnittstelle . Dies ermöglicht die Erstellung heterogener Systeme, die jedoch hinsichtlich des Speichers vollständig kohärent sind. Dies ist von entscheidender Bedeutung, da es die Verwendung eines einzigen Pools von ermöglicht RAM für das Gesamtsystem. Dies ist bei den heutigen eingebetteten Systemen und insbesondere bei kostengünstigen Lösungen mit geringem Stromverbrauch weit verbreitet, bei denen sich verschiedene Komponenten denselben Speicherpool teilen.