Eines der heute am weitesten verbreiteten Konzepte im Computerbereich ist zweifellos das von XMP. Jeder Benutzer, der mäßig an Hardware interessiert ist, weiß, dass, wenn wir über Speicherübertaktungsprofile sprechen, Intel hat das Maß genommen AMD, das sich durch seine AMP-Technologie ständig an diese Anforderungen anzupassen versucht. Mit der Abkehr von Alder Lake-S als revolutionärer Architektur geht Intel einen Schritt weiter und präsentiert XMP 3.0 , aber welche Neuigkeiten verbirgt es?

Einige fragen sich nach den Gründen für Intels Entscheidungen bezüglich RAM und speziell XMP. Obwohl wir es nie erfahren werden, war der Wechsel von DDR4 zu DDR5 aus der Perspektive der Übertaktung ein idealer Zeitpunkt, um Änderungen und Verbesserungen zu implementieren, da die 4,800 MHz des JEDEC sie werden nur wenige Tage nach der Einführung der Core-12-CPUs zurückgelassen.

Daher und angesichts der Geschwindigkeit, mit der Hersteller ihre Module mit zunehmender serieller Geschwindigkeit beschleunigen und aktualisieren, bleibt nur die Frage, ob Intel dies berücksichtigt hat? Ist XMP 3.0 auf dem neuesten Stand der Anforderungen?

Intel XMP 3.0, eine notwendige Wendung

eXtreme Memory Profile oder XMP ist seit 2007 bei uns und in dieser dritten Version rückblickend und nach 14 Jahren ist es normal, dass der blaue Riese eine neue Überarbeitung mit Neuigkeiten veröffentlicht. Wieso den? Für die Änderungen, die DDR5 gegenüber DDR4 voraussetzt. Wir gehen nicht auf dieses Thema ein, da wir es bereits in der Erweiterung behandelt haben, aber wenn es etwas zu XMP 3.0 zu sagen gibt, dann ist es exklusiv für DDR5 als solches.

Der Begriff Profil seines Namens kommt in den Finger, um den ersten der Punkte zu erklären, die Intel den Herstellern gegeben hat, da diese Technologie, wie wir wissen, auf der Erkennung einer Reihe von Konfigurationstabellen basiert, die jeder Hersteller je nach Modell nach Geschmack integriert , Chip- und Speicherversion, damit der IMC diese Einstellungen erkennt und über die Firmware anwendet.

Was ist neu in Intel XMP 3.0

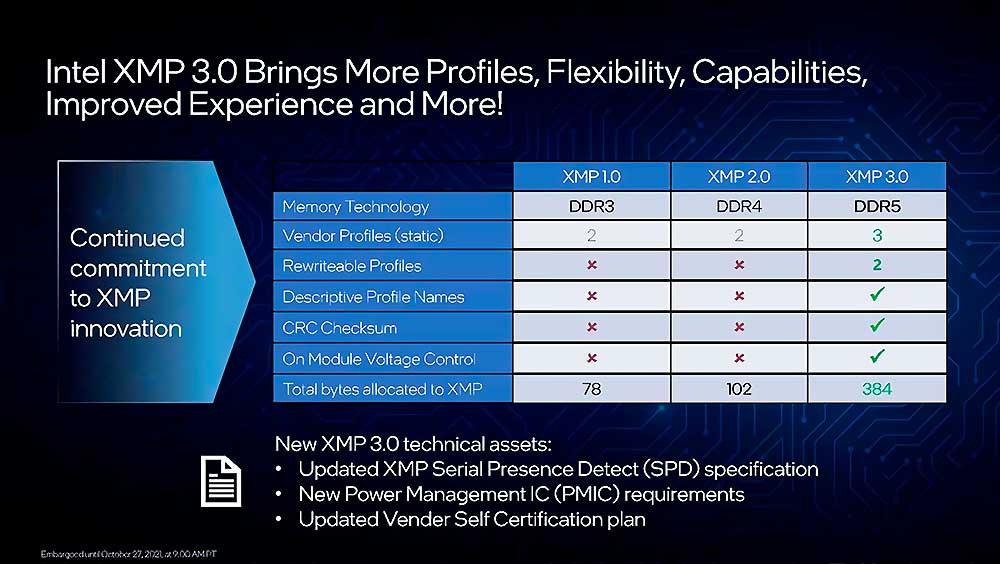

Diese Tabellen enthalten Geschwindigkeiten in MHz, Takte und Zeiten von primären, sekundären und tertiären Zugriffen, die in einigen Fällen logisch schneller oder in anderen langsamer sind, aber in allen Fällen die allgemeine Leistung des Speichers und damit des Systems erhöhen. In der ersten Version namens XMP hat es Intel geschafft, das Lesen eines Profils im Speicher und des JEDEC (technisch gesehen ist es ein Profil, aber sie werden als zwei gezählt) aufzunehmen.

XMP 2.0 hat das Niveau auf zwei Leseprofile angehoben, bei denen Hersteller festlegen können, ob sie zwei verschiedene Werte und Tabellen wünschen, die Benutzererfahrung personalisieren und unterschiedliche Leistungen bevorzugen (drei reale Werte zählen die JEDEC). Mit XMP 3.0 können Hersteller nun zwei oder drei Profile einbinden, wobei sie zwei vom Benutzer angepasste auswählen können.

SPD-Update

Einer der Schlüsselpunkte für das XMP-Profil ist genau das SPD- oder Serial Presence Detect-Spezifikation . Dies hat Herstellern und Benutzern mehrere Kopfschmerzen bereitet, hauptsächlich weil sie vom EEPROM geschrieben werden können und daher beschädigt werden. Es gibt einige Programme, die das können und natürlich verursacht es Abstürze im Speichercontroller, da dieser die Werte nicht korrekt aus dem XMP lesen kann und der Speicher unbrauchbar ist, bis ein erneutes Flashen korrekt erfolgt.

Jetzt und mit XMP 3.0 werden wir zwei aktualisierbare Profile haben, die helfen, dass, wenn eines beschädigt ist, das andere den Speicher arbeiten lässt, sein SPD extrahiert und später Modul für Modul geflasht werden kann, um den Speicher zu reparieren, als ob nichts gewesen wäre passiert.

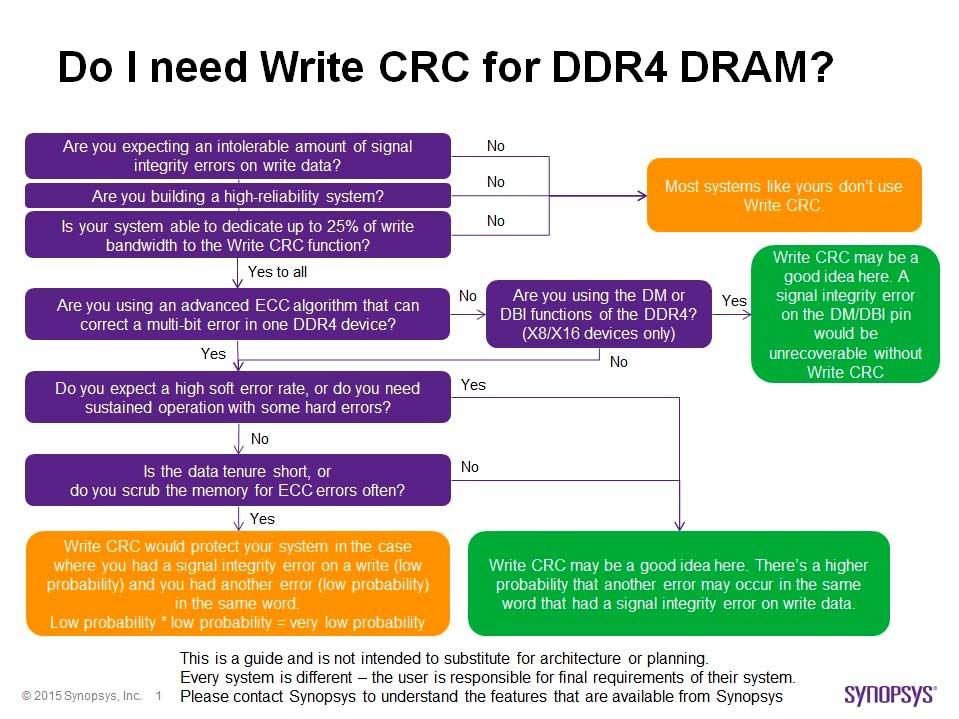

CRC-Prüfsumme

Seltsamerweise und bereits erklärt, warum haben DDR4-Module mit XMP 2.0 keinen CRC? Es ist nicht genau so und logischerweise hat es ein Warum. CRC als solches wurde in seiner Write-Version im JEDEC-Standard für DDR4 hinzugefügt, aber der zyklische Redundanzcode hat ein Problem: einen hohen Bandbreitenverbrauch. Die Daten zeigen den Verbrauch von 25 % des gesamten Schreibens des Systems und natürlich ist es nicht akzeptabel, mit den Margen und Geschwindigkeiten, die wir heute bewegen, so viel Bandbreite zu verlieren.

Dies ist mit DDR5 kein Problem mehr, da neben der Einbeziehung des PMIC in den Speicher selbst, physikalisch in das Modul, die Geschwindigkeiten im Vergleich zu DDR4 monströs sind und sein werden, insbesondere wenn wir über die doppelte Bandbreite verfügen, die diese Art von Speicher integriert . Daher integriert Intel mit XMP 3.0 die begehrte CRC-Prüfsumme, die die Daten und Integrität der SPD sowie die CPU Speichercontroller.

Größerer Platzgewinn für XMP 3.0

Einer der Schlüsselaspekte und wir verstehen bereits alles, was wir über das neue XMP 3.0 gesagt haben, ist, dass wir logischerweise mehr Platz brauchen, um all dies unterzubringen. Daher hat Intel von 78 Bytes pro Modul für XMP 1.0 auf 102 für XMP 2.0 angehoben und erhöht es jetzt auf 384 Byte Kontrolle für XMP 3.0.

Dadurch können voreingestellte Speicherprofile wie SPD aus den Hauptplatine BIOS/UEFI. Die Frage, die wir haben, ist dann das Verhalten des BMI der neuen Alder Lake- und Meteor Lake-Prozessoren (ein signifikanter Frequenzsprung wird erwartet) mit den unterschiedlichen Geschwindigkeiten, die wir von den Herstellern und Chips sehen werden.

Werden wir XMP 3.0-Profile über 6000 MHz sehen? Kann der BMI der CPUs sie unterstützen, ohne die Spannung und damit den Verbrauch und die Degradation zu übersteigen? Im Moment wissen wir, dass es Marken gibt, die an Profilen für DDR5-7000 arbeiten. Die Ausdauer der integrierten Speichercontroller ist größer als man meinen könnte.

Zu bedenken ist, dass XMP 3.0 zwar bei bestimmten Modulen sehr hohe Geschwindigkeiten erreicht, aber der IMC bestimmt, ob er diese Geschwindigkeit und seine Spannung unterstützen kann, die logischerweise unabhängig von der des RAMs selbst ist.

Nachdem dies gesagt und klargestellt wurde, können wir nur sagen, dass Intel einen sehr großen Schritt nach vorne gemacht hat, den größten seit der Einführung von XMP im Jahr 2007, und als solcher muss AMD jetzt seine Technologie und IMC an diese neuen anpassen Anforderungen mit Zen. Vier.