Sicherlich ist den allermeisten von euch nicht bewusst, dass wir soweit am Rande eines Scheidewegs stehen CPU und GPU sind besorgt. Es gibt nicht viel Spielraum, es ist nicht viel Zeit und was übrig bleibt, wird knapp. Ein so grundlegendes Bauteil wie das Rechnen selbst muss geändert werden: im Transistor. Intel hat seine Vision des Problems und eine Lösung: das wird der Intel RibbonFET.

Um die Lösung zu verstehen, müssen wir uns zunächst des Problems bewusst sein, es verstehen und wissen, was die Grenzen sind, die uns markieren werden, also werden wir in diesem Fall dort beginnen, mit den Problemen der Transistoren heute. Ein Transistor ist die kleinste elektrische Einheit, die für ein elektronisches Bauteil hergestellt werden kann, ein elektrisches Element als solches, das aus Halbleitern besteht und von unglaublich fortschrittlichen Scannern mit einer Wellenlänge auf Spiegeln aufgezeichnet wird.

Es ist im Grunde ein Schalter, der zwischen Dutzenden von Siliziumschichten (in der Regel) von sehr kleiner Größe verbunden ist und eine äußerst klare Funktion hat: den Stromfluss zu ändern, den es durchläuft, nachzugeben oder zu schneiden. Jeder Schnitt oder Schritt stellt entweder eine Null oder eine Eins in binärer Form dar und im Laufe der Zeit wurde erreicht, dass sie verbessert wird, was mehr Geschwindigkeit bei der Zustandsänderung, mehr oder weniger Energie für diese Änderung und mehr oder weniger Effizienz beim Lassen ermöglicht der aktuelle Pass.

Wir nähern uns dem Rand der Transistortechnologie

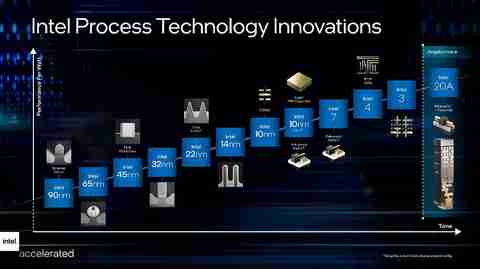

Wie wir bereits dachten, hat jeder Transistor eine Reihe von Bauformen, die je nach Hersteller variieren. Intel hat seine Vision, TSMC die gleiche und Samsung mehr vom gleichen, also obwohl alle mehr oder weniger in den Fortschritten kopiert wurden, sind die Implementierung und die Verbesserungen unterschiedlich.

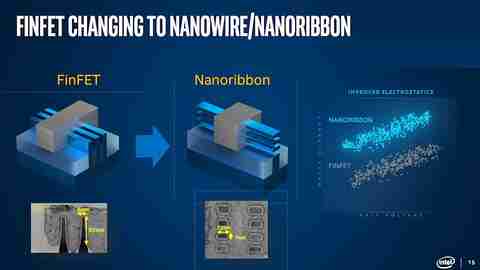

Vor einem Jahrzehnt hat Intel den FinFET-Transistor vorgestellt, der von allen Herstellern gewählt wurde, aber dieses Design geht aus mehreren Gründen zu Ende. Mit diesem Transistortyp hatten wir ein flexibles Design mit der gleichen, normalerweise breiten, wo mehrere Gates ihn kreuzten, was es Herstellern ermöglichte, Energiemanagement, Schweißen und Baumaterialien besser zu kontrollieren und seine Größe in Nanometern weiter zu reduzieren.

Das Hauptproblem, das wir haben, ist einfach: Es kann nicht viel mehr verkleinert werden, da wir in Längsrichtung begrenzten Platz haben und die Gates jedes Transistors nicht mehr zusammenfügen können, ohne Elektronen zu verlieren. Hinzu kommt, dass der Abstand zwischen ihnen so gering ist, dass das Schweißen und Verbinden enorm teure neue, zum Teil noch experimentelle Materialien und Legierungen erfordert, die den Energiedurchgang garantieren und nicht den Preis auslösen.

Was ist die Lösung? Ein neuer Transistortyp, der es nicht nur ermöglicht, mehr Schichten Strom zu treiben, die Steuerung, das Schweißen und die Effizienz zu verbessern, sondern auch den Abstand zwischen den Transistoren auf Angström (molekulare und atomare Maßeinheit) zu reduzieren.

RibbonFET, Intels Lösung für die neue Grenze der Lithografie

Wenn Sie den Platz nicht weiter reduzieren und alle Parameter kontrollieren können, ohne die Kosten auszulösen, müssen Sie nur einen neuen Weg untersuchen. Dieser neue Weg in Form einer neuen Architektur für den Transistor heißt GAA oder auch als Gate-All-Around bekannt. Von hier aus wird das Konzept in drei oder sogar 4 Aspekte unterteilt (es ist nicht ganz klar):

- TSMC GAAFET .

- Samsung MBCFET .

- Intel Bändchen-FET .

- Global Foundries steckt in einer Schwebe mit Gerüchten, aber nichts Konkretes.

was geschieht hier? Nun, wie bei FinFET wird es bei GAA mehrere Varianten geben, die alle auf demselben Transistorkonzept basieren. Wir haben bereits über Samsung MBCFET gesprochen, GAAFET wurde noch nicht als solches enthüllt, obwohl es mit den 2 nm des Unternehmens ankommen wird des riesigen Blaus: RibbonFET.

Das Konzept ist einfach, aber schwer umzusetzen. Sie nehmen einen Transistor mit flexibler Breite, der sich bei jedem lithographischen Sprung verkleinert und der es ermöglicht, mehrere Schichten, von der Industrie heute Nanosheets, Dry Sheets oder Finnen genannt, vertikal statt horizontal auf dem Transistor zu verbinden. Was wird erreicht? Nun, zunächst einmal die Breite des Transistors stark reduzieren, mehr Nanoblätter auf einer kleineren Oberfläche und vor allem ein einziges Gate ermöglichen, das die gesamte Energie der Zelle steuert.

Die Elektrostatik hat sich enorm verbessert, wie Intel in seiner offiziellen Präsentation gezeigt hat, bei der wir nur die Größen des Pitch Gate und des Gate Stack sehen müssen. Es geht von 6 nm x 50 nm bis 12 nm x 7 nm und mit mehr Kontroll-Nanoblättern und besser gelötet.

Ein variables Nanosheet-Design entsprechend den Anforderungen des Transistors

Anscheinend und wie wir in verschiedenen Dokumenten gesehen haben, seit Intel von diesem neuen Transistortyp sprach, scheint es, dass der blaue Riese eine variable Anzahl von Nanoblättern pro Transistor sammeln kann.

Dieses Detail ist wichtig, da Intel die Lithographie basierend auf besseren EUV-Scannern abschwächt, kann es entweder die gleiche Anzahl beibehalten oder diejenigen entfernen, die es zur Optimierung jedes Gates benötigt. Die Dokumente zeigen von 2 bis 5, aber im letzten Datenblatt scheint die runde Zahl 4 zu sein bis Sie über eine verbesserte Gravur und Produktionskontrolle, Materialien und Schweißnähte verfügen, die es Ihnen ermöglichen, eine Reihe bestimmter Nanoschichten zu eliminieren und Kosten zu senken, ohne die Stabilität, Geschwindigkeit oder Effizienz der Transistoren zu beeinträchtigen.

Dies hängt logischerweise von der Höhe des Gates und damit von der Anzahl der Sheets ab, die wir darin installieren können, da jedes Ende jetzt, anstatt wie in FinFET von drei Seiten umgeben zu sein, vollständig vom Gate umgeben ist, was einer ist Seite ist optimal, aber die andere macht es schwierig, die Höhe zwischen den Blättern zu reduzieren.

Wann wird Intel RibbonFET in seinen Chips implementieren? Nach Angaben des Unternehmens selbst im Jahr 2024 sicherlich bis Ende desselben Jahres, wenn alles gut läuft, obwohl wir es bei einem reibungslosen Ablauf bis Mitte desselben Jahres sehen könnten. In jedem Fall wird es sein 20A-Lithografieprozess sein, der es einschließt und mit dem konkurrieren wird TSMCs GAAFET und Samsungs MBCFET . Intel ist so zuversichtlich, dass es einen Unterschied machen wird, dass es bereits erklärt hat, 2025 wieder führend in der Halbleiterindustrie und deren Technologie zu sein – zweifellos eine Absichtserklärung.